* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download A 7GHZ 1MV-INPUT-RESOLUTION COMPARATOR WITH 40MV

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Current source wikipedia , lookup

Power inverter wikipedia , lookup

Three-phase electric power wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Surge protector wikipedia , lookup

Alternating current wikipedia , lookup

Power MOSFET wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Stray voltage wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Voltage regulator wikipedia , lookup

Buck converter wikipedia , lookup

Power electronics wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Oscilloscope history wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrating ADC wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

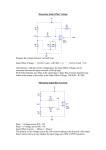

A 7GHZ 1MV-INPUT-RESOLUTION COMPARATOR WITH 40MV-INPUT-REFERRED-OFFSET COMPENSATION CAPABILITY IN 65NM CMOS Anh T. Huynh, Chien M. Ta, Praveen Nadagouda, Robin J. Evans, and Efstratios Skafidas National ICT Australia (NICTA) Department of Electrical and Electronic Engineering The University of Melbourne E-mail: [email protected] ABSTRACT A 7GHz-clock 1mV-input-resolution comparator is designed and simulated in a 65nm CMOS process. The comparator offset is compensated by changing the body voltages of the input differential triple-well NFET transistor pair. A reset switch is added between two regeneration nodes to further match voltages in reset phase. Kickback noise in this comparator is reduced by isolating regeneration nodes of the cross-coupled inverters from the input nodes. Simulated delay of the comparator at ΔVin = 1mV@VDD=1.2V is 69ps. The comparator can operate with a 7GHz clock and a differential input voltage as small as 1mV@VDD=1.2V and can compensate for an input-referred offset of up to 40mV. Index Terms— Comparator, high speed ADC, offset, complementary metal-oxide-semiconductor(CMOS). comparators with low input-referred offset still remains an open challenge. In this paper, we propose a clocked comparator with added offset compensation capability. The offset is compensated by adjusting the bulk voltages of the triple-well NFET transistors which form the input differential transistor pair of the comparator. With this technique, an input-referred offset of up to 40mV can be compensated. This comparator can operate with the clock frequency up to 7GHz and with a differential input voltage as small as 1mV at VDD=1.2V. 2. PROPOSED COMPARATOR DESIGN 2.1. Comparator Schematics VDD Clkb M11 1. INTRODUCTION INV1 Out2p Comparators are an essential component of analog-to-digital converters (ADCs). Their function is to compare two input voltages or two input currents and to output a logical value which indicates whether one signal is greater than the other. For high-speed high-resolution ADCs, they are required to have low input-referred offset and high speed operation. Several approaches have been proposed in the literature to compensate offset including: (1) store the offset using a capacitor [1]; (2) connect the output of the preamplifier to a current DAC which can supply or remove excess current flowing through the differential pair [2, 3]; and (3) place trimmable buffer in front of the comparator [4]. However, these approaches connect offset compensation circuit to either the source or the drain terminal of the input differential transistors of the comparator. This introduces excess capacitance which decreases comparator speed. Therefore, designing high-speed The authors would like to thank IBM and National ICT Australia (NICTA) for their support. National ICT Australia is funded by the Australian Government’s Department of Communications, Information Technology, and the Arts and the Australian Research Council through Backing Australia’s Ability and the ICT Research Centre of Excellence programs M9 M10 Outm Out1m Out1p INV2 MA M5 M7 M8 M6 Out2m Outp Clkb VDD M0,M1,M2,M3,M4: Clocked Preamplifier M3 M4 Clk Out0m Vp Vb1 Out0p Vb2 Vm M5,M6: intermediate amplifying stage M7,M8,M9,M10,M11: crossed-coupled inverters M2 M1 MA: Reset switch Clk M0 Fig. 1. Comparator Schematics In Fig. 1, the proposed comparator consists of a clocked preamplifier, an intermediate amplifying stage, a pair of clocked regenerative cross-coupled inverters with a reset switch followed by two inverters, and a NAND-based latch [5]. Its operation can be divided into two phases: reset (Clk=0) and comparison (Clk =1). CCECE 2011 Niagara Falls, Canada 978-1-4244-9789-8/11/$26 ©2011 IEEE IEEE CCECE 2011 - 000333 ∙ Reset phase: transistors M0 and M11 are switched off; transistors M3 and M4 are on. Out0m and Out0p are precharged to VDD. Out1m and Out1p are pulled to ground. Reset transistor MA is on. The advantage of adding MA to the circuit is to ensure that the voltages at Out1m and Out1p are equal at the beginning of each comparison phase. ∙ Comparison phase: M3 and M4 are off. M0 is switched on. Out0p and Out0m are discharged through M1 and M2. If the voltage at Vp is higher than the voltage at Vm, Out0m is discharged faster than Out0p. The positive feedback operation in the cross-coupled inverters pulls Out1m down to ground and Out1p up to near VDD. Furthermore, kickback noise of the comparator is suppressed because M5 and M6 isolate Out1m and Out1p from Vp and Vm, respectively. The insertion of INV1 and INV2 between the cross-coupled inverters and the following latch reduces the parasitic capacitance at Out1p and Out1m, thus further increases the comparator speed. of the clock signal during compensation can be as low as several MHz. Thus, the offset compensation circuit can be optimized to consume a minimum amount of power. Using this scheme, the input offset of the comparator can be compensated within 64 clock cycles. Fig. 2. Histogram of Input-referred Offset of proposed core comparator 2.2. Input-Referred Offset Compensation The input offset of comparator due to device mismatch limits the resolution of the comparator. Therefore, designing an efficient offset calibration circuit plays an important role in comparator design. Fig. 2 shows the histogram of the inputreferred offset of the proposed core comparator obtained from 100 Monte Carlo runs. The mean and the standard deviation 𝜎 of the offset is about 300uV and 10.5 mV, respectively. An offset compensation scheme which is able to compensate up to ±3𝜎 = ±31.5𝑚𝑉 of input-referred offset is required. The offset in the comparators are largely caused by their threshold voltage variations. Theoretically, the threshold voltage of a transistor can be described as ) (√ √ (1) 2𝜙𝐵 + 𝑉𝑆𝐵 − 2𝜙𝐵 𝑉𝑇 𝐻 = 𝑉𝑇 𝐻0 + 𝛾 Where VTH0 is the threshold voltage when VSB = 0 , 𝛾 is the body effect coefficient, and 𝜙B is the surface potential at threshold. Device mismatch changes body effect coefficient which manifests variations of the threshold voltage (ΔVin). In order to compensate for this threshold voltage variation, body biasing offset compensation scheme [6] is used in this paper. As shown in Fig. 3a, a control logic, a 6-bit counter, and a resistive DAC are used to adjust the body voltages of the triple-well NFET differential input transistor pair, which has the layout structure shown in Fig. 3b. Kickback noise effect is simulated by using an input signal source with finite source impedance. The offset compensation process is complete when the output of the comparator switches between 0 and 1. Since the output of the DAC is connected to the bulk terminals, the high speed operation of the design is not negatively affected by the offset compensation circuit. Frequency Clkb Signal source ~ Vmi DAC 6 bits 6-bit Counter ~ Vpi Buffer Vb1 Buffer Vb2 Vp Vm Clkb Clk Up Mode Outp Comparator Outm Clk Control Logic (a) Offset Compensation (b) Triple-well NFET layout Fig. 3. Offset compensation Scheme. 3. SIMULATION RESULTS The proposed comparator design was simulated using Cadence SPECTRE simulator with IBM 65nm CMOS process technology. In order to simulate kickback noise effect, a signal source with a finite source resistance is used. Fig. 4 shows the transient behavior of the comparator for two values of peak-to-peak differential input amplitude: ΔVin = 2mV and ΔVin = 50mV. The common-mode voltage in both cases is 700mV and the power supply voltage VDD is 1.2V. The comparator was clocked with a 7GHz clock. As shown in the figure, in the reset phase (CLK =0), Out1p and Out1m are precharged to ground; Out2p and Out2m are precharged to VDD. The logical values of Outp and Outm are held. In the comparison phase (CLK = 1), because of shielding effect of transistor M5 and M6, large variations at the nodes Out1m and Out1p only cause small disturbances at Vp and Vm. Therefore, kickback noise effect does not cause the comparator to make a wrong decision. It also can be seen that the IEEE CCECE 2011 - 000334 180 : ΔVin=2[mV] : ΔVin=50[mV] 1.2V Comparison Reset 0.6V 0V Clkb 160 Clk 140 ΔVin = 2mV ΔVin = 10mV ΔVin = 50mV ΔVin = 100mV ΔVin = 200mV Vp 120 Delay [ps] 720mV 700mV Vm 680mV Out1m 1.2V 100 80 0.6V 60 Out1p 0V Out2m 1.2V 40 0.6V 1.2V 20 0.9 Out2p 0V Outp 0.6V 1 1.2 VDD [V] 1.3 1.4 1.5 Delay=67ps (ΔVin=2mV) Delay=51ps (ΔVin=50mV) Outm Fig. 6. Delay versus VDD 0V 80 1.1 100 150 200 250 300 350 Time [ps] Fig. 4. Transient behavior of the proposed comparator 76 Vcm = 550mV Vcm = 575mV Vcm = 600mV Vcm = 650mV Vcm = 700mV Vcm = 750mV 74 72 Delay [ps] 70 68 66 64 62 60 58 56 1 3 5 7 ΔVin [mV] 9 11 13 15 Fig. 5. Delay versus input voltage difference delay of the comparator when ΔVin = 50mV is 51ps. This delay increases to 67ps when ΔVin decreases to 2mV. Fig. 5 shows the simulated delay of the comparator versus differential input voltage under different conditions of input common-mode voltage Vcm at VDD = 1.2V. The delay of the comparator at ΔVin = 1mV@Vcm = 700m is 69ps. For a given value of Vcm, the delay decreases as differential input voltage increases. Furthermore, the delay is also dependent on the variation of common-mode voltage. For example, at ΔVin = 9mV, the delay increases by 3ps, from 59ps to 62ps, as Vcm decreases by 200mV, from 750mV to 550mV. Fig. 6 depicts the dependence of the comparator delay on power supply level at various differential input voltages. For ΔVin = 10mV, the delay is 147ps at VDD = 0.9V. This delay drops from 147ps to 50ps when VDD changes from 0.9V to 1.5V. In addition, at a given VDD, the larger the differential input voltage, the smaller the comparator delay. The waveforms of the comparator at both offset compensation and comparison modes are plotted in Fig. 7. The input- referred offset used in this simulation is 40mV. In offset compensation mode, bulk biasing voltages are differentially varied to compensate for the input-referred offset. As the input referred offset is successfully compensated, the comparator outputs periodically switch between logic 0 and logic 1 at the clock rate as shown in Fig. 7a. Fig. 7b shows the waveforms of the comparator after offset compensation is successfully performed. The simulated waveforms shows that the 40mV input-referred offset of the comparator has been removed and the comparator outputs correct logical values when the input voltage difference is as small as 1mV at 7GHz clock signal. Table 1 summarizes the performance of the proposed comparator, in comparison with the designs in [5], [6] and [7]. The proposed comparator with offset compensation only consumes 0.8mW at sampling frequency of 7GHz. Table 1. Performance Comparison [7] [8] [9] Year Tech. Supply voltage Max sampling freq. Offset Compensation Input resolution Power IEEE CCECE 2011 - 000335 2009 65nm CMOS 1.2V 2009 130nm CMOS 1.2V 2009 65nm CMOS 1.2V This work 2010 65nm CMOS 1.2V 7GHz 5.4GHz 1GHz 7GHz N/A N/A Yes Yes 15mV N/A N/A 1mV 1.3mW 0.265mW 386uW 0.8mW 5. REFERENCES Clk[V] 1.2 0.6 [1] B. Razavi and B.A. Wooley, “Design techniques for highspeed, high-resolution comparators,” Solid-State Circuits, IEEE Journal of, vol. 27, no. 12, pp. 1916 –1926, Dec. 1992. 0 720mV Vpi Input Referred Offset 700mV Vmi up [V] Mode[V] 680mV 1.2 Offset Compensation Mode 0.6 [2] S. Park a, “A 4GS/S 4b Flash ADC in 0.18𝜇m CMOS,” in Solid-State Circuits Conference, 2006. ISSCC 2006. Digest of Technical Papers. IEEE International, Feb. 2006, pp. 2330 –2331. 0 1.2 Offset is successfully compensated 0.6 0 730mV Bulk biasing voltages generated from the DAC Vb1 400mV [3] K.-L.J. Wong and C.-K.K. Yang, “Offset compensation in comparators with minimum input-referred supply noise,” Solid-State Circuits, IEEE Journal of, vol. 39, no. 5, pp. 837 – 840, May. 2004. Vb2 160mV 1.2V Outp 0.6V Outm 0V 0 1 2 3 4 5 6 Time [μs] (a) Comparator waveforms in the offset compensation mode 1.2V Clk 0.6V Clkb Vpi[mV] 721 720 719 Vmi[mV] 681 680 679 Mode[V] 0V 1.2 142.857ps (7Ghz) [5] D. Schinkel, E. Mensink, E. Kiumperink, E. van Tuijl, and B. Nauta, “A Double-Tail Latch-Type Voltage Sense Amplifier with 18ps Setup+Hold Time,” in Solid-State Circuits Conference, 2007. ISSCC 2007. Digest of Technical Papers. IEEE International, Feb. 2007, pp. 314 – 605. ΔVin=1mV) 0.6 0 730mV Vb2 400mV Bulk biasing voltages found from Compensation mode Vb1 160mV 1.2V Outp 0.6V 0V 6952 Outm 6952.1 6952.2 6952.3 Time [ns] 6952.4 6952.5 (b) Comparator waveforms in the comparison mode Fig. 7. modes [4] Sunghyun Park, Y. Palaskas, A. Ravi, R.E. Bishop, and M.P. Flynn, “A 3.5 GS/s 5-b Flash ADC in 90 nm CMOS,” in Custom Integrated Circuits Conference, 2006. CICC ’06. IEEE, sep. 2006, pp. 489 –492. Waveforms in the compensation and comparison 4. CONCLUSION A high-speed high-resolution comparator design in a 65nm CMOS process was presented. Body biasing of input differential pair using a resistive DAC was used to compensate for the offset caused by device mismatch of the comparator. In addition, the impact of the large variations at the regeneration nodes on the input nodes was reduced by an intermediate stage. Therefore, kickback noise influence could be suppressed. A transistor switch was added between regeneration nodes to rapidly equate their voltages before the comparison phase starts. SPECTRE simulation showed that the delay of the comparator at ΔVin = 1mV@VDD=1.2V was 69ps. For VDD =1.2V, the offset compensation circuit was able to compensate for input-referred offset of up to 40mV, which was more than 3𝜎 variation of the uncalibrated input offset. The comparator could operate at a clock rate up to 7GHz. [6] E. Alpman, H. Lakdawala, L.R. Carley, and K. Soumyanath, “A 1.1V 50mW 2.5GS/s 7b TimeInterleaved C-2C SAR ADC in 45nm LP digital CMOS,” in Solid-State Circuits Conference - Digest of Technical Papers, 2009. ISSCC 2009. IEEE International, Feb. 2009, pp. 76 –77,77a. [7] B. Goll and H. Zimmermann, “A 65nm CMOS comparator with modified latch to achieve 7GHz/1.3mW at 1.2V and 700MHz/47 𝜇W at 0.6V,” in Solid-State Circuits Conference - Digest of Technical Papers, 2009. ISSCC 2009. IEEE International, Feb. 2009, pp. 328 –329,329a. [8] M.J.T. Marvast and M.A.M. Ali, “High speed comparator for flash ADC and UWB application in 130 nm CMOS technology,” in Signal and Image Processing Applications (ICSIPA), 2009 IEEE International Conference on, Nov. 2009, pp. 402 –405. [9] Xiaolei Zhu, S. Tsukamoto, and T. Kuroda, “A 1 GHz CMOS comparator with dynamic offset control technique,” in Asia and South Pacific Design Automation Conference, 2009. ASP-DAC 2009, Jan. 2009, pp. 103 – 104. IEEE CCECE 2011 - 000336