* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Introduction to Sampled

Immunity-aware programming wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrating ADC wikipedia , lookup

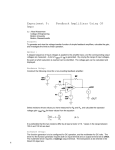

Buck converter wikipedia , lookup

EE215D B. Razavi HO#4 Introduction to Sampled-Data Circuits EE215D B. Razavi HO#4 Sampling Switches An NMOS or PMOS transistor can operate as a switch because: Motivation - It can be on with zero current. - Its source and drain voltage is not “pinned” to the gate voltage. In the resistive feedback circuit shown below: R2 Vin A bipolar transistor is simply not a good sampling switch if used in saturation. Vout R1 Now consider two cases: - R1 loads preceding stage; - R2 loads the op amp; - R1 introduces substantial thermal noise; - Can’t “freeze” (sample) the input. Furthermore, in continuous-time filters the location of poles and zeros depends on the absolute value of resistors and capacitors. Now consider the following circuit: S2 CK Vdd = 1.2 V Vout Vin 0 CK C Vdd Vout Vin 1.2 V 1.2 V 1.2 V C 0V Vdd - Vth Vout t t C2 S1 Vin S3 C1 Vout The switch can pass current in both directions. In the steady state, Vout “tracks” Vin (and the switch acts as a resistor). What is the on-resistance of the switch? - At the instant when S1 turns off, the value of Vin is sampled. CMOS is especially suited to sampled-data applications because it provides: - “zero-offset” switches - High input impedance. 1 2 EE215D B. Razavi HO#4 Switch Nonidealities EE215D B. Razavi HO#4 Upon turnoff, this charge exits the channel. How does the charge split between source and drain? - On-Resistance What happens as the input and output voltages become more positive? Ron CK Vout Vin Vin,Vout Vthp Vdd-Vth Important Note: Since it is difficult to calculate or control the amount of channel charge that does either way, we must design the circuit to be immune to this effect. Also, most versions of SPICE have a very poor model of charge injection. Effect of charge injection: Vdd Vout Note that unlike in cascode stages, VTH limits the swing here. ǻVc ÎUse complementary switches: CK ǻQ Cs realistic Square law CK Vin,Vout The mid-supply range is still troublesome at low supply voltages. ÎTo reduce the effect of clock feedthrough and charge injection, need to make the switch smaller or the sampling capacitor larger. Æ Trade-off between speed and precision - Cancellation Techniques 1. Dummy Switch: M1: 2W/L - Clock Feedthrough and Charge Injection Qch § WLeff Cox (VGS – VTH) 3 Vdd CK CK When a MOSFET is on, it carries charge in the inversion layer” M1 M2 M2:W/L Vdd W 0 2W 0 2WCov ǻQ 4 2WCov C EE215D B. Razavi HO#4 With perfect matching, clock feedthru is cancelled. But charge injection may not be. EE215D B. Razavi HO#4 Other Examples of SC Circuits: 1. “Resistor” Iin 2. Complementary Switches CK Vdd - Vin M1 Vin Vin Neither feedthrough nor charge injection is fully cancelled. Cs CK If every T seconds, Cs charges to Vin and discharges to ground, the average current is: Iin = CsVin/T. Thus, the circuit can be viewed as a resistor equal to: M2 Vin CK 3. Differential Sampling CK CK 2. Integrator Continuous-Time Vin1 Vout1 Vin2 Vout2 Discrete-Time C2 C R Vin Vin Vout 4. “Bottom Plate” Sampling Better discrete-time integrators will be described in the context of oversampling converters. CK M2 CK C1 Vin M1 C2 Vout CK 5 Vout C1 6 EE215D B. Razavi HO#4 EE215D B. Razavi HO#4 Effect of change in Vin after S2 turns off: Noninverting Amplifier S2 S2 C2 C2 S1 C1 Vin Vin X P Vout S1 t C1 p C1 Vin X X Vout Vout S3 S3 Typical cap. Structure: C2 Vin0 C1/C2 * Vin0 C1 P X Unity-Gain Sampler Vout Simple Unity-Gain Sampler t Charge Inj. of S2: S3 S1 S2 ǻq2 Better Unity-Gain Sampler Vin Vout S2 CH C2 S1 Vin0 S1 Vin p C1 CH Vin X X Vout Vout Charge Inj. of S1: S1 turns off C2 S1 Vin ǻq1 p Charge Injection of S2: Vin0 C1 ǻq2 ǻq1/C1 X Vp Vout S3 S1 S3 turns on 0 t Vin S3 S2 CH CH X Vout X Vout No input dependent 0 t ǻq1/C1 * -C1/C2 7 8 Vout -¨q2/CH EE215D B. Razavi HO#4 Charge Injection of S1: Method I: P ǻq1 B. Razavi HO#4 Speed Considerations CH S1 Vin EE215D X CH Vout Cx X Vin X Vout CH Cin Av1 Vout Av1 CL Method II: CH CH S1 P Vin X X Vout ǻq1 CX Vout CX Av1 VoCH + CinVx X X CH Vout Cin Vout Cin Av1 Vout Vs Vo CH (12.48) Note that for s = 0, (12.48) reduces to a form similar to (12.41). Since typically GmRoCH >> CH , Cin , we can simplify (12.48) as Precision Considerations Vin (Gm + Cin*s) Vout (s) = Ro Vs Ro(CLCin + CinCL + CHCL)*s + GmRoCH + CH + Cin (Gm + Cin*s) CH (s) = (12.49) Thus, the response is characterized by a time constant equal to Av1 (CLCin + CinCL + CHCL) IJamp = 9 (CLCin + CinCL + CHCL)*s + GmCH GmCH 10 (12.50) EE215D B. Razavi HO#4 EE215D B. Razavi HO#4 - Hold-Mode Feedthrough Other Sampling Nonidealities Rout MOS Switches - Variation of On-Resistance with Input Vout Vin off CH Switch Bootstrapping Vin Basic Idea: t Î Creates harmonic distortion. Realization (Abo, JSSC, May 99): - Input-Dependent Sampling Instant A MOS device turns off when VGS < VTH. If the clock transition time is nonzero, then the exact time at which the switch turns off depends on the input level: Vck S1 turns off S1 turns off Vck Vin Vin t t Î Creates harmonic distortion. 1 2 Vout Cov Vin CH hold RoutCovs 2RoutCovs + 1 EE215D B. Razavi HO#4 EE215D Operation Details: B. Razavi HO#4 Correction: In Eq. (2.29), change Ts to Tin = 1/fin. Example What is the jitter requirement for Bogner’s 14-bit 100-MHz A/D converter? For an ideal 14-bit converter: SNR § 86 dB. Let’s say the SHA has the same SNR (which means the overall system will have an SNR of 83 dB). Then: Clock Jitter - Jitter is the random time variation in the clock transitions. T1 T2 CK Sample-and-Hold Architectures t Conventional Open-Loop Architecture - Effect of Jitter on SNR CK error Vin t B S B Vout C Max error b/c highest slew - Most suitable for high-speed applications with S implemented as a diode bridge - B1 and B2 directly contribute nonlinearity. Example: Source-Follower Buffers: Jitter makes uniform sampling non-uniform. t İ Vin = A Sin 2ʌ fin t dVin dt n(t) = İ dVin t dt İ Since İ is random, İ d Vin / dt appears as additive noise at the output. 3 4 EE215D B. Razavi HO#4 Switched-Capacitor Architecture S3 S2 S1 Vin CH X Vout (2) Acq. Mode Hold Mode - The dominant sample-and-hold technique in CMOS technology. Simple and relatively efficient. - S1 introduces input-dependent delay Î its on-resistance must be small. - In CMOS, op amp A is actually a transconductance amplifier Gm. - Linearity of op amp determines the overall linearity, and its open-loop gain sets the gain error. 5