* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download A 1-V, 10-MHz Clock-Rate, 13-Bit CMOS A¡ Modulator Using Unity

Power inverter wikipedia , lookup

Voltage optimisation wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Ground loop (electricity) wikipedia , lookup

Electrical substation wikipedia , lookup

Control system wikipedia , lookup

Dynamic range compression wikipedia , lookup

Electronic engineering wikipedia , lookup

Negative feedback wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Two-port network wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Regenerative circuit wikipedia , lookup

Mains electricity wikipedia , lookup

Flexible electronics wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Oscilloscope history wikipedia , lookup

Integrating ADC wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

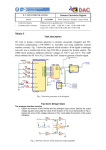

A 1-V, 10-MHz Clock-Rate, 13-Bit CMOS Modulator Using Unity-Gain-Reset Opamps Mustafa Keskin, Un-Ku Moon, and Gábor C. Temes Department of Electrical and Computer Engineering, Oregon State University Corvallis, OR 97331-3211 [email protected] Abstract C C2 A low-voltage modulator, incorporating unitygain-reset opamps, is described. Due to the feedback structure, the opamps do not need to be switched off during operation, and hence can be clocked at a very high rate. A test chip, realized in a 0.35- m CMOS process and clocked at 10.24 MHz, provided a dynamic range (DR) of 80 dB and a signal-to-noise+distortion-ratio (SNDR) of 78 dB for a 20-kHz signal bandwidth, and DR = 74 dB and SNDR = 70 dB for a 50-kHz BW. C1 1. Introduction Fine-linewidth low-voltage CMOS technologies make possible fast and low-power operation for digital circuitry; however, they introduce problems for the designers of analog circuits [1]. One difficulty involves the operation of floating switches required in switched-capacitor (SC) cirbecomes compacuits. If the dc supply range rable to (or is less than) the sum of the magnitudes of the , these floating switches can threshold voltages no longer be turned on for midrange signals [2]. Boosted or bootstrapped clock signals can overcome this problem [3], but they may stress and damage the gate oxide [4]. Low-threshold switches can also be used [5], but they require special fabrication technology which may be expensive, and tend to lead to increased leakage currents. The commonly used technique for realizing lowvoltage (LV) SC circuits in standard CMOS technology uses switched opamps (SOs) [6], [7]. An SC integrator using a SO is shown in Fig. 1. It does not have any floating switches, and hence can use low (e.g., 1 V) supply voltage. However, since the opamp needs to be turned off and then on again in every clock cycle, the settling time of the resulting transients limits the speed of the operation. An alternative to the SO technique was proposed by us earlier [8]. It utilizes opamps whose output is reset to their input during one of the clock phases, and hence will be called reset opamps (ROs). The opamps remain in their active voltage regions at all times, and hence the turn-on and turn-off transients are avoided, making fast operation possible. Details of the various circuit techniques which can be used to implement RO stages were described in [8]. Φ2 Vout Vin Φ2 Φ1 Φ1 Φ2 !#"$&%('!) *,+.-/"/0.132465!7849;:/*"<=5/*2>% This paper describes a LV (1.05-1.2 V) high-speed modulator using RO stages. It was fabricated in a standard 0.35- m CMOS process, could be clocked over 10 MHz, and achieved 13-bit performance over the audio frequency range. Over a 50-kHz signal band, it gave a 12.5-bit conversion accuracy. 2. Modulator architecture Fig. 2 illustrates the block diagram of the modulator. Since the RO integrators used introduce half clock period delays, matching delays were introduced into the feedback paths. These were realized in the digital domain, using half-delay RS flip-flops. IN + - Σ -1/2 z 1 - z -1 1/2 + - Σ -1/2 1/2 OUT z 1 - z -1 &#"8?%@62A)B1DCA2E *,5A&" 7F20!E 5/*23% -1/2 -1/2 z z 3. The RO integrator and the input buffer IJH GFH Fig. 3 shows the basic RO integrator. While is high, the input capacitor is charged to the input voltage , and the opamp output is reset to (more precisely, to , to keep the output devices in saturation). When the next rises, the output voltage of the preceding RO is reset, causing the charge in to enter . Hence, changes by an increment which is a linear function of . All switches in the stage operate at K.L ONP QR IUS KVXW/ K.L GTS M IJH ZY\[ , and hence they all can be realized by single NMOS transistors. Vdd M10 M11p M9p Cp Φ1 Φ2 Is C Φ2 Rp M7p Gnd Vinp M11n Rn Gnd Vinn Vdd M1n M2n Vdd M6p M8p M9n M5n M7n M2p M1p Vdd C2 Cn Vdd M6n M8n Voutp Voutn M12p Vdd Φ1 M5p M4p M3p M12n M4n M3n Vdd  _Ao>/X.63i bn !&6!8 !! o&_AkR;8! /b.qaF!6dU. /A!8i Gnd C1 Φ2 Vout Vin Φ1 &#"8]%_^-A"J&: *a`b13&5;:/1X#"<cX"d*T;:/*"<#5/*2 Adc 68 dB eOf.S Note that (as mentioned above) the integrator introduces a half-period ( ) delay between its input and output signals, and hence adjacent stages must be operated with complementary clock phases. The input integrator is a special case, since its input capacitor is not connected to the output of a RO. Ref. [10] describes an input stage which can be used to feed the first integrator of the filter. The circuit used by us is shown in Fig. 4. It is similar to the buffers described in Refs. [10], [11]. It is basically a track-and-reset (T/R) circuit used as an input-sampling switch. During , it samples the input signal and provides the inverted input signal to the input capacitor of the first stage. During , the opamp is in unity-gain-reset configuration, providing to the first stage. Gg Gh Vinput Φ1 ¡¢ ¢A£¤ Level-Shifter Common-Mode Feedback Circuit Φ2 Vref Φ1 Cdc Previous Stage Ccm Φ1 Ci Φ2 Vref Φ2 Φ1 Vref Ccm Ccm Voutn Voutp Voutp Voutput Cs Vref Φ1 Ci Vref Ccm Φ1 Cdc Φ2 Ccm Voutp Voutn Ccm i !"kj%(^-A"J@lm;:!4&/*cn5!784!E ;:/o+/;=+6 *<% Φ2 Vref Φ1 Φ2 Common-Mode Feedback Circuit « ¬ &M#®¯¦ ¥M O/§/X.63i ¨.#./n !©;/<#/ª Level-Shifter Low-voltage opamp The opamp used is shown in Fig. 5 [12]. It has a pseudo-differential structure, chosen to ease the implementation of the common-mode feedback (CMFB) circuit. Each half contains a PMOS differential pair and an NMOS inverter output stage, with an RC compensating branch between them. The input stage uses a LV current mirror [7]. The minimum supply voltage needed for linear operation is given by RpTLqYmrts!uwv.x VXyz |{ S V,y~} Voutn Φ2 Ci Φ1 Ci Φ2 Φ1 Φ2 Φ2 Φ1 Vref Cs Φ1 4. Slew Rate 100 V/ s A charge-domain dc level shifter is required to maintain the appropriate input and output common-mode voltages for the opamps. With a CM level of at the opamp output, the CM at the next opamp input must be set to ground. Φ1 Vdd Tsettling 20 ns Vref 1.2V 0.6V 0V Φ2 R PM 70 5. Level shifting and CMFB circuits. R 0V -0.6V -1.2V fu 170 MHz (1) The main performance parameters of the opamp with a load of 3.5 pF are summarized in Table 1. ¡°X±b²³ ¡°X±b²´ The SC dc level shifter and CMFB circuit [9] used are shown in Fig. 6. The output voltages and are averaged and used to inject a correction charge into the virtual grounds, so as to obtain an output CM voltage equal to . ¡¢ ¢/£¤ 6. The comparator and the DAC feedback branch The low-voltage comparator used is shown in Fig. 7. It requires dc level shifters at the inputs to set the input CM to ground. The reset switches ground both latch outputs, since floating reset switches cannot be used. The simulated transition speed of the comparator was 12 ns. Vdd Vdd Vdd 8. Layout and floor plan M8 M7 Vdd I M10 Fig. 10 shows the die photo of the prototype IC, realized in a 0.35 m double-poly triple-metal CMOS technology. The digital and analog circuitries are separated, with the opamps located at maximum distance from the digital stages. Well and substrate guard strips and rings were also used to shield the sensitive analog elements from substrate noise. By using static switches, it was possible to allow operation using either the input stage of Fig. 4 or a floating input transmission gate at the frontend. This allowed operation even if the actual threshold voltages of the fabricated chip were different from the simulated values. The total chip area (excluding the input buffer) was 0.41 mm . M12 in+ out+ M1 reset M11 M5 in- M6 M4 M3 M2 outreset !#"kµM%(^-A"o@>l¶+<278465#5/*2>% M13 Fig. 8 shows the circuit diagram of the DAC feedback branches. Its switches operate at ground or . The CM of the DAC signal is cancelled by the level shifter circuits at the opamp inputs. g Vdd Φ1 To Virtual Ground of Integrator from Output of RS FlipFlop Digital Circuits Cref Φ2 Clock lines i !"U·M%(^-A"9E 2A)B1DCA2E *,5A&"9¸¹(ºw»"b"b0¼A56+.½9¼#5!:6+6-i% 7. Switches The overall circuit diagram Track/ Reset The circuit of the modulator (with the CMFB circuits and input buffers omitted for clarity) is shown in Fig. 9. The element values (scaled for optimum dynamic range) are given in Table 2. ^5!¼!E "U?%(^-A"U+<5!4656+/ *,5!:6+d"FCA5!E¾A"<c/% Cs1 Cdac Cdc1 Ci1 2 pF 2 pF 1 pF 8 pF Cs2 Cdac2 Cdc2 Ci2 0.8 pF 0.4 pF 0.12 pf 1.6 pF Vref Φ2 Vref Φ2 Φ1_p Vref Φ1 Cdc1 Φ2 Ci1 Φ1 for Testing Φ1 Cs1 Vinp Vinn Φ1 Φ1 Φ2 Φ1 Φ 2_p Vref Φ2 Cs1 Φ1 Ci2 Φ2 Cs2 Φ2 Vref Φ1 Φ 2_p Φ 2_p Csc Φ2 Φ1 Φ2 Φ1_n Φ1_n Vref Cs2 Ci1 Φ1 Φ2 Vref Φ1 Φ1 Cdc2 Vref Φ2 Cdac2 Φ2 Φ1_p Φ2 Φ 2_n Φ 2_n Ci2 Φreset Φ2 Csc Φ1 Φ1 S Q S Q R Q R Q Φ2 Φ1 Vref Φ1 Cdcc Φ 2_n Φ 2_n Φ2 Φ2 Φ1_n Φ1_n Φ2 i !"8¿M%À^O-/"o@>l¶c,"/+d2:A01a2=0&". 7~2i0&E 5/*2>% Φ2 Φ1 Φ1_p Φ2 Φ2 Vref Cdac1 Cdcc Φ2 Φ2 Cdc1 Φ1 Vref Cdc2 Vref Φ1 9. Test results Φ1 Φ1 Vref Φ2 Φ2 0.4 pF 0.4 pF Φ 2_p Cdac2 Integrators &#"$bÁM%¯^-A"U0 "o4!-A2.*2#5!4!-82.»T@>l¶c,"/+d2:601a2=0" 7~2i0&E 5/*2>% Vref Φ1_p Cdac1 Csc Cdcc First and Second Comparator Φ1 Φ1 Φ1 The fabricated chip was tested with a 10.24 MHz clock signal and with varying (1.05 to 1.2 V) supply voltages. Table 3 gives a summary of the measured results. For audio band (0 to 20 kHz) operation, a true 13-bit accuracy resulted; extending the input frequency range to 0-50 kHz, ENOB = 12.5 bits was obtained. The chip remained operational, but at ENOB = 10.5 bits, down to 0.95 V supply voltage. The SDNR and SNR curves for a 2.5 kHz input sine wave are shown in Fig. 11. The typical measured spectrum of the digital output stream is illustrated in Fig. 12. No harmonics were detected. There was a variation of the threshold voltages from the simulation models to the actual chips. While the models assumed 0.55 V and 0.55 V, in the chips ranged from 0.486 V to 0.563 V, and from 0.422 V to 0.486 V. In the low-threshold chips, the floating input switch could be turned on; in the others, the |{/ |{/ÂY |{dM(ÂY |{dM 80 70 60 11. Acknowledgments SNR 20kHz SNDR 20kHz SNR 50kHz SNDR 50kHz The authors are grateful to José Silva, Robert Batten, Tetsuya Kajita, and Greg Barnes for their assistance during the design and fabrication of the prototype. Additionaly, we are thankful to AMI Semiconductor for fabricating the test chip. This work was supported by the NSF Center for Design of Analog-Digital Integrated Circuits (CDADIC). [dB] 50 40 30 20 10 0 −10 −100 12. References −80 −60 −40 Vin/Vref [dB] −20 0 ci :6!5!"JE¼6$5!$!:A%_0&^c -A"Ã'ÄTÅt5!:A0'ÄT¸ÅÆ»2Ç?ÁZ½&ÈÀÉF5!:609Ê&Á½&ÈÀÉ ^5!¼!E "B¹O]M¸%˺¯^O% -/"~7~"b5Ac<&#"b094.".»2a7F5!:A+<"2»* -/"c,"/+d2:A01a2=0&". Signal Bandwidth Sampling Frequency Max. Diff. Input Dynamic Range Peak SNR Peak SNDR Power Consumption Supply Voltage Chip Core Area Technology 20 kHz 10.24 MHz 1.2 Vpp 80 dB 78.6 dB 77.8 dB 5.6 mW 1.05 V 0.41 mm 0.35 m g 50 kHz 10.24 MHz 1.2 Vpp 74 dB 70.6 dB 70.4 dB 5.6 mW 1.05 V 0.41 mm 0.41 mm g g 0 Magnitude (dB) −20 [1] Edgar Sánchez-Sinencio and Andreas G. Andreou, LowVoltage/Low-Power Integrated Circuits and Systems, IEEE Press, NJ 1999 [2] M. Steyaert, V. Peluso, J. Bastos, W. Sansen, “Custom analog low power design: The problem of low voltage and mismatch,” IEEE Custom Integrated Circuits Conference, 1997, pp. 285-292. ÏkÐ [3] J. Grilo, E. MacRobbie, R. Halim, Gabor C. Temes, “1.8 V, modulator for voice applications,” 94 dB dynamic range Proc. ISSCC, Feb. 1996, pp. 230-231. [4] “The national technology roadmap for semiconductors,” Semiconductor Industry Assoc., Tech. Rep., 1997 [5] T. Atachi, A. Ishinawa, A. Barlow, and K. Taksuka, “A 1.4 V switched capacitor filter,” Proc. CICC, May 1990, pp.8.2.18.2.4 ÏÃÐ Ñ [6] V. Peluso, M. Steyaert, and W. Sansen, “A 1.5 V 100 W modulator with 12-bit dynamic range using the switched-opamp technique,” IEEE J. Solid-State Circuits, vol. 32, pp. 943-952, July 1997. [7] V. Peluso, P. Vancorenland, A. Marques, M. Steyaert, and W. Sansen, “A 900 mW low-power A/D with 77 dB dynamic range,” IEEE J. Solid-State Circuits, vol. 33, pp. 1887-1896, Dec. 1998. −40 −60 [8] E. Bidari, M. Keskin, F. Maloberti, U. Moon, J. Steensgard, and G. C. Temes, “Low-voltage switched-capacitor circuits,” Proc. IEEE Int. Symp. Circuits Syst., Florida, May 1999, vol. II, pp. 49-52. −80 −100 −120 3 4 5 6 i !"Ì$/?%Í^O-/"cd4."/+ * a&7Î2.»Æ* -/"¶0i *,5!E~2b* 4!b*P¼. * c,* "/5!79% 10 10 10 10 Frequency (Hz) input buffer had to be used. The performance did not vary significantly between the two modes of operation. 10. Conclusions A low-voltage and fast delta-sigma ADC was designed and fabricated. It uses unity-gain-reset opamps, which do not require the turning on and off associated with switched opamps. The test results indicate that this circuit technique is suitable for high-speed high-accuracy operation with 1 V or lower supply voltages. [9] L. Wu, M. Keskin, U. Moon, and G. C. Temes, “Efficient common-mode feedback circuits for pseudo-differential switched-capacitor stages,” Proc. IEEE Int. Symp. Circuits Syst., Geneva, May 2000, vol. V, pp. 445-448. [10] A. Baschirotto, R. Castello and G. P. Montagna, “Active series switch for switch-opamp circuits,” Electron. Lett., vol. 34, pp. 1365-1366, July 1998. [11] M. Ishikawa and T. Tsukahara, “An 8-bit 50-MHz CMOS subranging A/D converter with pipelined wide-band S/H,” IEEE J. of Solid-State Circuits, vol. 23, pp. 1309-1315, Dec. 1988. [12] A. Baschirotto, “A 40 MHz CMOS sample & hold operating at 1.2 V,” ESSCIRC, 1998