* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download Chapter 4 Electrical Characteristics of CMOS

Ground (electricity) wikipedia , lookup

Solar micro-inverter wikipedia , lookup

Electric power system wikipedia , lookup

Power inverter wikipedia , lookup

Electronic engineering wikipedia , lookup

Control system wikipedia , lookup

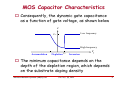

Fault tolerance wikipedia , lookup

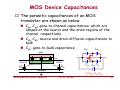

Wassim Michael Haddad wikipedia , lookup

Buck converter wikipedia , lookup

Distributed generation wikipedia , lookup

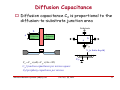

Power engineering wikipedia , lookup

History of electric power transmission wikipedia , lookup

Power electronics wikipedia , lookup

Public address system wikipedia , lookup

Mains electricity wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Distribution management system wikipedia , lookup

Alternating current wikipedia , lookup

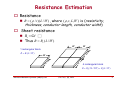

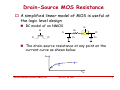

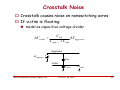

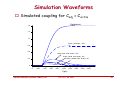

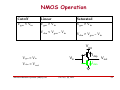

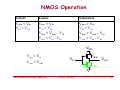

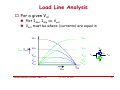

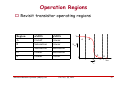

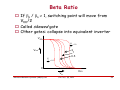

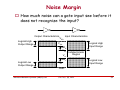

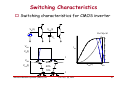

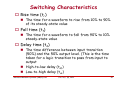

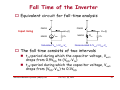

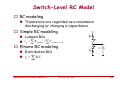

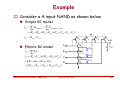

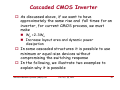

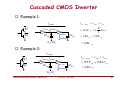

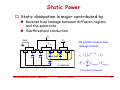

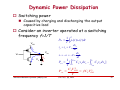

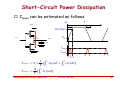

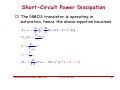

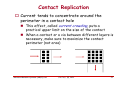

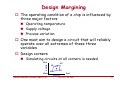

Chapter 4 Electrical Characteristics of CMOS Jin-Fu Li Department of Electrical Engineering National Central University Jungli, Taiwan Outline Resistance & Capacitance Estimation DC Response Logic Level and Noise Margins Transient Response Delay Estimation Transistor Sizing Power Analysis Scaling Theory Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 2 Resistance Estimation Resistance R ( / t )( L / W ) , where ( , t , L, W ) is (resistivity, thickness, conductor length, conductor width) Sheet resistance Rs / □ Thus R Rs ( L / W ) W W t 1 rectangular block R Rs ( L / W ) L W t L L 4 rectangular block R Rs (2 L / 2W ) Rs ( L / W ) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 3 Drain-Source MOS Resistance A simplified linear model of MOS is useful at the logic level design RC model of an NMOS G S S G Rn D Cs D CD The drain-source resistance at any point on the current curve as shown below Ids a b c Vds Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 4 Drain-Source Resistance The resistance at point a The current is approximated by I ds n (Vgs Vt )Vds Thus the resistance is Rn 1 / n (Vgs Vt ) The resistance at point b The full non-saturated current must be used so that 1 2 I [ 2 ( V V ) V V ds n gs t ds ds ] 2 Thus the resistance is Rn 2 / n [2(Vgs Vt ) Vds ] Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 5 Drain-Source Resistance The resistance at point c The current is I ds 1 n (V gs V t ) 2 2 Thus the resistance is 2 Rn 2Vds / n (Vgs Vt ) Rn is a function of both Vgs and Vds These equations show that it is not possible to define a constant value for Rn However, Rn is inversely proportion to n in all cases, i.e., Rn 1 / n n k (W / L) , W/L is called aspect ratio Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 6 Capacitance Estimation The switching speed of MOS circuits are heavily affected by the parasitic capacitances associated with the MOS device and interconnection capacitances The total load capacitance on the output of a CMOS gate is the sum of Gate capacitance Diffusion capacitance Routing capacitance Understanding the source of parasitic loads and their variations is essential in the design process Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 7 MOS-Capacitor Characteristics The capacitance of an MOS is varied with the applied voltages Capacitance can be calculated by C 0 x A d x is dielectric constant 0 is permittivity of free space Depend on the gate voltage, the state of the MOS surface may be in Accumulation Depletion Inversion Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 8 MOS Capacitor Characteristics Consequently, the dynamic gate capacitance as a function of gate voltage, as shown below C Low frequency Cox High frequency Accumulation Depletion Vt Vg Inversion The minimum capacitance depends on the depth of the depletion region, which depends on the substrate doping density Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 9 MOS Device Capacitances The parasitic capacitances of an MOS transistor are shown as below Cgs, Cgd: gate-to-channel capacitances, which are lumped at the source and the drain regions of the channel, respectively Csb, Cdb: source and drain-diffusion capacitances to bulk Cgb: gate-to-bulk capacitance Cgd Cdb gate Cgs Cgb channel source Cgd drain depletion layer Cdb Csb Cgs Cgb Csb substrate Cg=Cgb+Cgs+Cgd Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 10 Variation of Gate Capacitance The behavior of the gate capacitance in the three regions of operation is summarized as below Off region (Vgs<Vt): Cgs=Cgd=0; Cg=Cgb Non-saturated region (Vgs-Vt>Vds): Cgs and Cgd become significant. These capacitances are dependent on gate voltage. Their value can be estimated as C gd C gs 1 0 SiO2 A 2 tox Saturated region (Vgs-Vt<Vds): The drain region is pinched off, causing Cgd to be zero. Cgs increases to approximately C 2 o SiO A 2 gs Advanced Reliable Systems (ARES) Lab. 3 t ox Jin-Fu Li, EE, NCU 11 Approximation of the Cg The Cg can be further approximated with C g C ox A , where Cox o SiO 2 tox The gate capacitance is determined by the gate area, since the thickness of oxide is associated with process of fabrication For example, assume that the thickness of silicon oxide of the given process is 150108 m . Calculate the capacitance of the MOS shown 2 below 0 .5 m 4 5 Cg 3 . 9 8 . 854 10 150 10 8 Advanced Reliable Systems (ARES) Lab. 14 2 25 . 5 2 10 4 pF 0 . 005 pF Jin-Fu Li, EE, NCU 12 Diffusion Capacitance Diffusion capacitance Cd is proportional to the diffusion-to-substrate junction area Substrate b a Source Diffusion Area Drain Diffusion Area a b Cjp Xc (a finite depth) Cd C ja (ab) C jp (2a 2b) Cja=junction capacitance per micron square Cjp=periphery capacitance per micron Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU Cja 13 Junction Capacitance Semiconductor physics reveals that a PN junction automatically exhibits capacitance due to the opposite polarity charges involved. This is called junction or depletion capacitance and is found at every drain or source region of a MOS The junction capacitance is varies with the junction voltage, it can be estimate as C j C j 0 (1 Vj Vb )m C j =junction voltage (negative for reverse bias) C j 0 =zero bias junction capacitance ( Vj 0 ) Vb =built-in junction voltage ~ 0 .6V Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 14 Single Wire Capacitance Routing capacitance between metal and substrate can be approximated using a parallel-plate model Fringing fields W L T H substrate Insulator (Oxide) In addition, a conductor can exhibit capacitance to an adjacent conductor on the same layer Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 15 Multiple Conductor Capacitances Modern CMOS processes have multiple routing layers The capacitance interactions between layers can become quite complex Multilevel-layer capacitance can be modeled as below Multi-layer conductor C23 Layer 3 C22 C21 Layer 2 Layer 1 C2=C21+C23+C22 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 16 A Process Cross Section Interlayer capacitances of a two-level-metal process A B C D m2 m2 E F m2 m2 C C C poly G m1 C m2 m2 m1 C poly C m1 C C Thin-oxide/diffusion Substrate Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 17 Inductor For bond wire inductance L ln( 4h ) 2 d d For on-chip metal wires L ln( 8h w ) 2 h w w h 4h The inductance produces Ldi/dt noise especially for ground bouncing noise. Note that when CMOS circuit are clocked, the current flow changes greatly di V L dt Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 18 Distributed RC Effects The propagation delay of a signal along a wire mainly depends on the distributed resistance and capacitance of the wire A long wire can be represented in terms of several RC sessions, as shown below Ij-1 R C R C Vj-1 R Vj C Ij R Vj+1 C R C The response at node Vj with respect to time is then given by CdV Idt C dV j ( I I ) (V j 1 V j ) (V j V j 1 ) j 1 j R R dt Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 19 Distributed RC Effects As the number of sections in the network becomes large (and the sections become small), the above expression reduces to the differential form 2 dV d V 2 t kx rc x dt dx 2 r : resistance per unit length c : capacitance per unit length Alternatively, a discrete analysis of the circuit shown in the previous page yields an approximate signal delay of RCn( n 1) t n 0 .7 2 rcl 2 t1 0.7 2 Advanced Reliable Systems (ARES) Lab. , where n=number of sections Jin-Fu Li, EE, NCU 20 Wire Segmentation with Buffers To optimize speed of a long wire, one effective method is to segment the wire into several sections and insert buffers within these sections Consider a poly bus of length 2mm that has been divided into two 1mm sections. Assume that t x 4 10 15 x 2 15 2 15 2 t 4 10 1000 t 4 10 1000 With buffer p buf 4ns tbuf 4ns 8ns tbuf Without buffer t p 4 1015 20002 16ns By keeping the buffer delay small, significant gain can be obtained with buffer insertion Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 21 Crosstalk A capacitor does not like to change its voltage instantaneously. A wire has high capacitance to its neighbor. When the neighbor switches from 1-> 0 or 0->1, the wire tends to switch too. Called capacitive coupling or crosstalk. Crosstalk effects Noise on nonswitching wires Increased delay on switching wires Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 22 Crosstalk Delay Assume layers above and below on average are quiet Second terminal of capacitor can be ignored Model as Cgnd = Ctop + Cbot Effective Cadj depends on behavior of neighbors Miller effect B V Ceff(A) MCF Constant VDD Cgnd + Cadj 1 Switching with A 0 Cgnd 0 Switching opposite A 2VDD Cgnd + 2 Cadj 2 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU A Cgnd B Cadj Cgnd 23 Crosstalk Noise Crosstalk causes noise on nonswitching wires If victim is floating: model as capacitive voltage divider Vvictim Cadj Cgnd v Cadj Vaggressor Aggressor Vaggressor Cadj Victim Cgnd-v Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU Vvictim 24 Driven Victim Usually victim is driven by a gate that fights noise Noise depends on relative resistances Victim driver is in linear region, agg. in saturation If sizes are same, Raggressor = 2-4 x Rvictim Vvictim Cadj C gnd v Cadj 1 Vaggressor 1 k Raggressor Advanced Reliable Systems (ARES) Lab. Cgnd-a Vaggressor aggressor Raggressor Cgnd a Cadj k victim Rvictim C gnd v Cadj Jin-Fu Li, EE, NCU Aggressor Cadj Rvictim Victim Cgnd-v Vvictim 25 Simulation Waveforms Simulated coupling for Cadj = Cvictim Aggressor 1.8 1.5 1.2 Victim (undriven): 50% 0.9 0.6 Victim (half size driver): 16% Victim (equal size driver): 8% 0.3 Victim (double size driver): 4% 0 0 200 400 600 800 1000 1200 1400 1800 2000 t(ps) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 26 DC Response DC Response: Vout vs. Vin for a gate Ex: Inverter When Vin = 0 Vout=VDD VDD When Vin = VDD Vout=0 In between, Vout depends on Idsp Vout transistor size and current Vin Idsn By KCL, must settle such that Idsn = |Idsp| We could solve equations But graphical solution gives more insight Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 27 Transistor Operation Current depends on region of transistor behavior For what Vin and Vout are NMOS and PMOS in Cutoff? Linear? Saturation? Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 28 NMOS Operation Cutoff Vgsn < Vtn Linear Vgsn > Vtn Saturated Vgsn > Vtn Vdsn < Vgsn – Vtn Vdsn > Vgsn – Vtn VDD Vgsn = Vin Vin Vout Idsn Vdsn = Vout Advanced Reliable Systems (ARES) Lab. Idsp Jin-Fu Li, EE, NCU 29 NMOS Operation Cutoff Linear Saturated Vgsn < Vtn Vin < Vtn Vgsn > Vtn Vin > Vtn Vdsn < Vgsn – Vtn Vout < Vin - Vtn Vgsn > Vtn Vin > Vtn Vdsn > Vgsn – Vtn Vout > Vin - Vtn VDD Vgsn = Vin Vdsn = Vout Advanced Reliable Systems (ARES) Lab. Vin Idsp Vout Idsn Jin-Fu Li, EE, NCU 30 PMOS Operation Cutoff Vgsp > Vtp Linear Vgsp < Vtp Saturated Vgsp < Vtp Vdsp > Vgsp – Vtp Vdsp < Vgsp – Vtp VDD Vgsp = Vin - VDD Vdsp = Vout - VDD Advanced Reliable Systems (ARES) Lab. Vtp < 0 Vin Idsp Vout Idsn Jin-Fu Li, EE, NCU 31 PMOS Operation Cutoff Linear Saturated Vgsp > Vtp Vin > VDD + Vtp Vgsp < Vtp Vin < VDD + Vtp Vdsp > Vgsp – Vtp Vout > Vin - Vtp Vgsp < Vtp Vin < VDD + Vtp Vdsp < Vgsp – Vtp Vout < Vin - Vtp VDD Vgsp = Vin - VDD Vdsp = Vout - VDD Advanced Reliable Systems (ARES) Lab. Vtp < 0 Vin Idsp Vout Idsn Jin-Fu Li, EE, NCU 32 I-V Characteristics Make pMOS is wider than nMOS such that n = p Vgsn5 Vgsn4 Idsn Vgsn3 -Vdsp Vgsp1 Vgsp2 -VDD 0 VDD Vdsn Vgsp3 Vgsp4 Vgsn2 Vgsn1 -Idsp Vgsp5 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 33 Current & Vout, Vin Idsn, |Idsp| Vin1 Vin5 Vin2 Vin4 Vin3 Vin3 Vin4 Vin5 Vin2 Vin1 Vout Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU VDD 34 Load Line Analysis For a given Vin: Plot Idsn, Idsp vs. Vout Vout must be where |currents| are equal in Idsn , |Idsp | Vin1 Vin5 Vin2 Vin4 Vin3 Vin3 Vin4 Vin5 Vin2 Vin1 Vout Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU VDD Vin Idsp Vout Idsn VDD 35 DC Transfer Curve Transcribe points onto Vin vs. Vout plot Vin1 Vin5 Vin2 Vin4 Vin3 Vin3 Vin4 Vin5 Vin2 Vin1 VDD Vout VDD A B Vout C D 0 Vtn VDD/2 E VDD+Vtp VDD Vin Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 36 Operation Regions Revisit transistor operating regions Region nMOS pMOS A Cutoff Linear B Saturation Linear C Saturation Saturation D Linear Saturation E Linear Cutoff VDD A B Vout C D 0 Vtn VDD/2 E VDD+Vtp VDD Vin Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 37 Beta Ratio If p / n 1, switching point will move from VDD/2 Called skewed gate Other gates: collapse into equivalent inverter VDD p 10 n Vout 2 1 0.5 p 0.1 n 0 Vin Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU VDD 38 Noise Margin How much noise can a gate input see before it does not recognize the input? Output Characteristics Logical High Output Range VDD Input Characteristics Logical High Input Range VOH NMH VIH VIL Indeterminate Region NML Logical Low Output Range VOL Logical Low Input Range GND Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 39 Transient Analysis DC analysis tells us Vout if Vin is constant Transient analysis tells us Vout(t) if Vin(t) changes Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 40 Switching Characteristics Switching characteristics for CMOS inverter Vin(t) Vout(t) Vds=Vgs-Vt CL VDD Ids Vin(t) VDD t tdr tdf 90% Vout(t) Vout(t) 50% 10% tf Advanced Reliable Systems (ARES) Lab. tr VDD t Jin-Fu Li, EE, NCU 41 Switching Characteristics Rise time (tr) The time for a waveform to rise from 10% to 90% of its steady-state value Fall time (tf) The time for a waveform to fall from 90% to 10% steady-state value Delay time (td) The time difference between input transition (50%) and the 50% output level. (This is the time taken for a logic transition to pass from input to output High-to-low delay (tdf) Low-to-high delay (tdr) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 42 Fall Time of the Inverter Equivalent circuit for fall-time analysis PMOS PMOS Vout(t) Input rising NMOS Idsn CL Saturated Vout>=VDD-Vtn Vout(t) NMOS Rcn CL Nonsaturated 0<Vout<=VDD-Vtn The fall time consists of two intervals tf1=period during which the capacitor voltage, Vout, drops from 0.9VDD to (VDD-Vtn) tf2=period during which the capacitor voltage, Vout, drops from (VDD-Vtn) to 0.1VDD Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 43 Timing Calculation tf1 can be calculated with the current-voltage equation as shown below, while in saturation CL dVout n (VDD Vtn ) 2 0 dt 2 tf2 also can be obtained by the same way Finally, the fall time can be estimated with tf k CL nVDD Similarly, the rise time can be estimated with tr k CL pVDD Thus the propagation delay is t p k CL ( 1 1 ) VDD n Advanced Reliable Systems (ARES) Lab. p Jin-Fu Li, EE, NCU 44 Design Challenges n = p , rise time=fall time This implies Wp=2-3Wn Reduce CL Careful layout can help to reduce the diffusion and interconnect capacitance Increase n and p Increase the transistor sizes also increases the diffusion capacitance as well as the gate capacitance. The latter will increase the fan-out factor of the driving gate and adversely affect its speed Increase VDD Designers don’t have too much control over this Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 45 Gate Delays Consider a 3-input NAND gate as shown below P3 P2 P1 out N3 IN-3 IN-2 N2 IN-1 N1 When pull-down path is conducting neff 1 (1 / n1 ) (1 / n 2 ) (1 / n 3 ) For n1 n 2 n 3 neff n 3 When the pull-down path is conducting Only one p-transistor has to turn on to raise the output. Thus peff p Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 46 Gate Delays Graphical illustration of the effect of series transistors L L 3L L w w In general, the fall time tf is mtf (tf/m) for m ntransistors in series (parallel). Similarly the rise time tr for k p-transistors in series (parallel) is ktr (tr/k) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 47 Switch-Level RC Model RC modeling Transistors are regarded as a resistance discharging or charging a capacitance Simple RC modeling Lumped RCs tdf Rpulldown C pulldown path Elmore RC modeling Distributed RCs t d Ri Ci Rp Rn C i Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 48 Example Consider a 4-input NAND as shown below Simple RC model t df R pulldown C pulldown path (RN1 RN2 RN3 RN4 ) (Cout Cab Cbc Ccd ) t dr R p 4 Cout P4 Elmore RC model A N4 Cab t d Ri Ci B tdf (RN1 Ccd ) [(RN1 RN 2 ) Cbc] C [(RN1 RN 2 RN 3) Cab] [( RN 1 RN 2 RN 3 RN 4 ) Cout ] D Jin-Fu Li, EE, NCU P2 P1 out Cout N3 i Advanced Reliable Systems (ARES) Lab. P3 Cbc N2 Ccd N1 49 Cascaded CMOS Inverter As discussed above, if we want to have approximately the same rise and fall times for an inverter, for current CMOS process, we must make Wp =2-3Wn Increase layout area and dynamic power dissipation In some cascaded structures it is possible to use minimum or equal-size devices without compromising the switching response In the following, we illustrate two examples to explain why it is possible Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 50 Cascaded CMOS Inverter Example 1: t inv pair t fall t rise tinv-pair R 3 C eq 2 Icharge 4/1 R 2/1 R 3Ceq Idischarge 3Ceq R 3 C eq 2 3 RC eq 3 RC eq 6 RC eq Wp=2Wn Example 2: tinv-pair 2/1 R 2 C eq 2 R 2 C eq R 2R 2/1 t inv pair t fall t rise Icharge 2Ceq Idischarge 2Ceq 6 RC eq Wp=Wn Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 51 Stage Ratio To drive large capacitances such as long buses, I/O buffers, etc. Using a chain of inverters where each successive inverter is made larger than the previous one until the last inverter in the chain can drive the large load in the time required The ratio by which each stage is increased in size is called stage ratio Consider the circuit shown below It consists of n-cascaded inverters with stageratio a driving a capacitance CL 1 a a2 a3 CL n(4) stages Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 52 Stage Ratio The delay through each stage is atd, where td is the average delay of a minimum-sized inverter driving another minimum-sized inverter Hence the delay through n stages is natd If the ratio of the load capacitance to the capacitance of a minimum inverter, CL/Cg, is R, then an=R Hence ln(R)=nln(a) Thus the total delay is ln(R)(a/ln(a))td The optimal stage ratio may be determined from k a opt a opt e a opt where k is Advanced Reliable Systems (ARES) Lab. C drain C gate Jin-Fu Li, EE, NCU 53 Power Dissipation Instantaneous power The value of power consumed at any given instant P ( t ) v ( t )i ( t ) Peak power The highest power value at any given instant; peak power determines the component’s thermal and electrical limits and system packaging requirements Ppeak Vi peak Average power The total distribution of power over a time period; average power impacts the battery lifetime and heat dissipation t T t T Pave 1 P ( t ) dt V i ( t ) dt T t Advanced Reliable Systems (ARES) Lab. T t Jin-Fu Li, EE, NCU 54 Power Analysis for CMOS Circuits Two components of power consumption in a CMOS circuit Static power dissipation Caused by the leakage current and other static current Dynamic power dissipation Caused by the total output capacitance Caused by the short-circuit current The total power consumption of a CMOS circuit is Pt Ps Psw Psc Ps: static power (leakage power); Psw: switching power; Psc: short-circuit power Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 55 Static Power Static dissipation is major contributed by Reverse bias leakage between diffusion regions and the substrate Subthreshold conduction Vin Gnd VDD PN junction reverse bias Vout leakage current p+ n+ n+ p+ p+ n+ i0 is (e qV / KT 1) n-well n p-substrate Ps I leakage Vsup ply 1 n=number of devices Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 56 Dynamic Power Dissipation Switching power Caused by charging and discharging the output capacitive load Consider an inverter operated at a switching frequency f=1/T 1 T Psw VDD 0 o o dvo dt dv in io C L o dt i p io C L ip Vout Vin in i (t )v (t )dt T CL io Advanced Reliable Systems (ARES) Lab. 0 1 VDD Psw [ CL vo dvo CL vo dvo ] VDD T 0 2 CLVDD 2 Psw fCLVDD T Jin-Fu Li, EE, NCU 57 Power & Energy Energy consumption of an inverter (from 0 VDD ) The energy drawn from the power supply is 2 E QV C LVDD The energy stored in the load capacitance is E cap VDD 0 1 2 Cvo dvo C LVDD 2 The output from VDD 0 The Ecap is consumed by the pull-down NMOS Low-energy design is more important than lowpower design Minimize the product of power and delay Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 58 Short-Circuit Power Dissipation Even if there were no load capacitance on the output of the inverter and the parasitics are negligible, the gate still dissipate switching energy If the input changes slowly, both the NMOS and PMOS transistors are ON, an excess power is dissipated due to the short-circuit current We are assuming that the rise time of the input is equal to the fall time The short-circuit power is estimated as Psc I meanVDD Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 59 Short-Circuit Power Dissipation Imean can be estimated as follows Vin T VDD VDD-|Vtp| isc Vin Vout tr tf Vtn CL Imax Imean t1 t2 t3 I mean I mean t3 1 t2 2 [ i (t )dt i (t )dt ] t2 T t1 4 t2 [ i (t )dt ] T t1 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 60 Short-Circuit Power Dissipation The NMOS transistor is operating in saturation, hence the above equation becomes 4 t2 I mean (Vin (t ) VT ) 2 dt ] [ T t1 2 V Vin (t ) DD t tr t1 VT tr VDD t2 tr 2 Psc 12 (VDD 2VT ) 3f ( tr t f ) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 61 Power Analysis for Complex Gates The dynamic power for a complex gate cannot be estimated by the simple expression CLVDDf Dynamic power dissipation in a complex gate Internal cell power Capacitive load power Capacitive load power 2 PL C LVDD f Internal cell power n P i CiViVDD f int i 1 Advanced Reliable Systems (ARES) Lab. VDD B C C1 A out A C B Jin-Fu Li, EE, NCU C2 62 Glitch Power Dissipation In a static logic gate, the output or internal nodes can switch before the correct logic value is being stable. This phenomenon results in spurious transitions called glitches ABC A B 100 111 D C D Z Z Unit delay Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU Spurious transition 63 Rules for Avoiding Glitch Power Balance delay paths; particularly on highly loaded nodes Insert, if possible, buffers to equalize the fast path Avoid if possible the cascaded design Redesign the logic when the power due to the glitches is an important component Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 64 Principles for Power Reduction Switching power dissipation 2 PL C LVDD f Pint n C V V i 1 i i i DD f Prime choice: reduce voltage Recent years have seen an acceleration in supply voltage reduction Design at very low voltage still open question (0.6V…0.9V by 2010) Reduce switching activity Reduce physical capacitance Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 65 Layout Guidelines for LP Designs Identify, in your circuit, the high switching nodes Keep the wires of high activity nodes short Use low-capacitance layers (e.g., metal2, metal 3, etc.) for high capacitive nodes and busses Avoid, if possible, the use of dynamic logic design style For any logic design, reduce the switching activity, by logic reordering and balanced delays through gate tree to avoid glitch problem In non-critical paths, use minimum size devices whenever it is possible without degrading the overall performance requirements If pass-transistor logic style is used, careful design should be considered Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 66 Sizing Routing Conductors Why do metal lines have to be sized? Electromigration Power supply noise and integrity (i.e., satisfactory power and signal voltage levels are presented to each gate) RC delay Electromigration is affected by Current density Temperature Crystal structure For example, the limiting value for 1 um-thick aluminum is J Al 1 2mA / m Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 67 Power & Ground Bounce An example of ground bounce Voltage Vin L Vout Time Current I Time VDD Pad Vout Vin I VSS Pad VL L VL=L(di/dt) Time Ground bounce Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 68 Approaches for Coping with L(di/dt) Multiple power and ground pins Restrict the number of I/O drivers connected to a single supply pins (reduce the di/dt per supply pin) Careful selection of the position of the power and ground pins on the package Avoid locating the power and ground pins at the corners of the package (reduce the L) Increase the rise and fall times Reduce the di/dt Adding decoupling capacitances on the board Separate the bonding-wire inductance from the inductance of the board interconnect Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 69 Contact Replication Current tends to concentrate around the perimeter in a contact hole This effect, called current crowding, puts a practical upper limit on the size of the contact When a contact or a via between different layers is necessary, make sure to maximize the contact perimeter (not area) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 70 Charge Sharing Charge Q=CV A bus example is illustrated to explain the charge sharing phenomenon A bus can be modeled as a capacitor Cb An element attached to the bus can be modeled as a capacitor Cs Bus Vb Cb Vs (Qb CbVb ) QT CbVb CsVs CT Cb Cs Advanced Reliable Systems (ARES) Lab. VR Cs (Qs CsVs ) QT (CbVb C sVs ) /(Cb C s ) CT Jin-Fu Li, EE, NCU 71 Design Margining The operating condition of a chip is influenced by three major factors Operating temperature Supply voltage Process variation One must aim to design a circuit that will reliably operate over all extremes of these three variables Design corners Simulating circuits at all corners is needed PMOS Fast Slow Advanced Reliable Systems (ARES) Lab. SF SS FF TT FS NMOS Fast Jin-Fu Li, EE, NCU 72 Package Issues Packaging requirements Electrical: low parasitics Mechanical: reliable and robust Thermal: efficient heat removal Economical: cheap Bonding techniques Wire Bonding Substrate Die Pad Lead Frame Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 73 Yield Estimation No. of good chips per wafer Y 100% Total number of chips per wafer Wafer cost Die cost Dies per wafer Die yield wafer diameter/22 wafer diameter Dies per wafer die area 2 die area Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 74 Die Cost Single die Wafer Going up to 12” (30cm) Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 75 Scaling Theory Consider a transistor that has a channel width W and a channel length L We wish to find out how the main electrical characteristics change when both dimensions are reduced by a scaling factor S>1 such that the new transistor has sizes ~ L ~ W L W S S Gate area of the scaled transistor A~ SA The aspect ratio of the scaled transistor ~ W W L L~ 2 Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 76 Scaling Theory The oxide capacitance is given by Cox t ox ox If the new transistor has a thinner oxide that is t decreased as ~tox ox , then the scaled device has S ~ Cox SCox The transconductance is increased in the scaled device to ~ S The resistance is reduced in the scaled device to R 1 R~ S (VDD VT ) S Assume that the supply voltage is not altered Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 77 Scaling Theory On the other hand, if we can scale the voltages in the scaled device to the new values of V~DD VDD V~T VT S S The resistance of the scaled device would be ~ unchanged with R R The effects of scaling the voltage, consider a scaled MOS with reduced voltages of ~ V VDS DS S ~ V VGS GS S The current of the scaled device is given by S VGS VT VDS I ~ [( ) ] D ID 2 S S S S The power dissipation of the scaled device is P~ V~DS I~D VDS 2I D P2 S Advanced Reliable Systems (ARES) Lab. S Jin-Fu Li, EE, NCU 78 Summary We have presented models that allow us to estimate circuit timing performance, and power dissipation Guidelines for low-power design have also been presented The concepts of design margining were also introduced The scaling theory has also introduced Advanced Reliable Systems (ARES) Lab. Jin-Fu Li, EE, NCU 79