* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download ISSCC 2008/SESSION 6/UWB POTPOURI/6.2

Survey

Document related concepts

Ringing artifacts wikipedia , lookup

Electronic engineering wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Regenerative circuit wikipedia , lookup

Rectiverter wikipedia , lookup

Oscilloscope history wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Chirp compression wikipedia , lookup

Opto-isolator wikipedia , lookup

Transcript

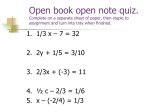

Copyright © 2008 Year IEEE. Reprinted from 2008 IEEE International Solid-State Circuits Conference. This material is posted here with permission of the IEEE. Such permission of the IEEE does not in any way imply IEEE endorsement of any of Institute of Microelectronics’ products or services. Internal or personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution must be obtained from the IEEE by writing to [email protected]. ISSCC 2008 / SESSION 6 / UWB POTPOURI / 6.2 6.2 A 0.18µm CMOS 802.15.4a UWB Transceiver for Communication and Localization Yuanjin Zheng, M. Annamalai Arasu, King-Wah Wong, Yen Ju The, Andrew Poh Hoe Suan, Duy Duong Tran, Wooi Gan Yeoh, Dim-Lee Kwong Institute of Microelectronics, Singapore, Singapore Recently, IEEE 802.15.4a has specified a UWB PHY for low-rate commutation with ranging capability for wireless personnel area and sensor network applications [1]. Related work is reported on low-rate energy-efficient UWB radios [2-4]. However, they are not fully standard compliant or localization enabled. 802.15.4a supports three bands of operation, i.e., sub-1GHz band (249.6 to 749.6MHz), low band (3.1 to 4.8GHz) and high band (6.0 to 10.6GHz) with 16 channels in total. A combination of the burst position modulation (BPM) and binary phase shift keying (BPSK) is adopted. With different coding rate, bursts per symbol, and chips per burst, the mean pulse repetition rate (PRF) could vary from 3.9 to 62.4MHz for data throughput of 120kHz to 31.2MHz. This work presents an UWB RF transceiver which supports 12 channels, variable date rate, and ranging capability as specified in IEEE802.15.4a. Figure 6.2.1 shows the RF transceiver architecture. On the TX side, the digital clock (TX_clk) triggers a baseband pulse-shaping filter (BPSF). The output pulses are modulated by the TX binary data. The signal is then upconverted by a mixer and amplified by a driver amplifier (DA) prior to the antenna. On the RX side, the weak signal is amplified by an LNA, is downconverted by I/Q mixers and is low-pass filtered to recover the phase of the transmitted BPSK signals. A VGA, in each I and Q path, is then used to boost the signal level. The output of each VGA is used in two paths. In one path it is connected to an integrator followed by an ADC for recovering the digital data while in the other path it goes through a signal detector (squarers and a limiting amplifier) to recover a clock (denoted as RC_clk). The delay time between the rising edge of RC_clk and that of TX_clk are extracted through a digital edge detector. The low-pass filtered output is thus precisely proportional to the delay and can be used for ranging calculation in baseband. The muti-tone frequency generator produces I/Q LOs. Typically, the duration of UWB pulses occupies a small duty cycle (<5%) allowing TX or RX to be powered down accordingly whenever there is no pulse transmission. The transmitter circuits are shown in Fig. 6.2.2. The BPSF consists of a cascade of a 1st-order and a biquad Gm-C filter with proper pole-zero placements to generate channel-mask-compliant pulses. Four switches, controlled by modulation data, change the polarity of the pulses. The upconvertor is a Gilbert-cell active mixer optimized for high linearity and is resistively loaded to cover the full UWB band. The mixer achieves a conversion gain of −9.6dB, IIP3 of 15.2dBm, NF of 15.4dB. The differential DA is a switched Class-A amplifier in order to preserve the constrained spectral and improve the efficiency. M3/4 and M5/6 allow DA to be turned off when no pulse is being transmitted. The complementary control inputs (Cr/Crb) are slightly delayed from each other to prevent undesired pulse generation by Ll/L2 during fast transitions of the control signals. The input transistors M1/M2 use resistive feedback to improve their bandwidth. The DA achieves a gain of 6 to 8dB, a BW of 6GHz (3 to 9GHz), and maximum output power of 8dBm. The TX draws a peak current of 8mA when generating 500MHz PRF pulses. Two measured pulse sequences at two mandatory channels and their spectrum are demonstrated in Fig. 6.2.3. For low-band mandatory Channel 3, the generated BPSK pulses are of 2ns width and the PSD spectrum of the transmitted signal complies with both the FCC-band mask and channel mask. Similarly, a pulse sequence generated in the high-band mandatory Channel 9 and its PSD spectrum are also shown. 6 The RX front-end circuits are shown in Fig. 6.2.4. The LNA is designed to operate at one channel at any given time, through band switching and channel selection, to minimize power consumption. The capacitive cross-coupled input stage is used to boost the Gm of the stage, and reduce input-referred noise while achieving good input matching. The band switching between low and high band can be done by transistors M3/M4 and M5/M6. Within each band, there are two-stage cascaded amplifiers. The first stage is an LC-tuned load where a capacitor bank is used to tune to the desired channel. The second stage is a common-source amplifier with an LC-tunable loading network. A double-balanced differential Gilbert cell is used as the mixer and its resistive loads are used to cover the entire UWB band. The combined RF front-end achieves a voltage gain of 30.4/21.3dB, an NF of 5.5/7dB, and an IIP3 of −16.7/−10.7dB for low and high bands, respectively. The RX LPF is implemented by a 3rd-order elliptical Gm-C filter with cut-off frequency of 250MHz. The five-stage cascaded dB-linear VGA achieves a dynamic gain from −20 to 50dB with 400MHz BW. The variable BW integrator captures the reflected pulses from multipath and extends the duration of the demodulated pulses. For localization purpose, two squarers and one nonlinear low-pass filter (NLPF) [5] are used to regenerate RC_clk, where the squarers are used to detect the signal energy and NLPF is used to boost signal level to rail-to-rail. Through the edge detector, a digital pulse train is turned on and off at the rising edge of TX_clk and RC_clk, respectively. A passive 5th-order RC LPF with cut-off frequency of 500kHz is applied to average the jitter and noise and hence to significantly improve the ranging accuracy. Operating at 500MHz PRF, the peak current of the RX is 31mA. A nine-tone frequency generator is shown in Fig. 6.2.5. A digital frequency-tuning loop is used to lock the quadrature VCO (QVCO) output frequency to an external 15.6MHz crystal reference. Once the QVCO is tuned to the desired channel, as determined by the lock detector, the tuning loop is powered off. The VCO tuning voltage is stored as a digital word in an 11b latch, where 3 bits are used for coarse tuning and the 8b DAC output is used for fine tuning. The accuracy of frequency tuning is <10MHz, which is limited by DAC resolution. To significantly reduce the die size, a four-stage ring oscillator with a frequency doubler is used as the QVCO core. The ring oscillator generates 45°/90° phase difference LOs covering 2.8 to 4.75GHz, and the frequency doubler generates quadrature LOs covering 5.6 to 9GHz. The measured QVCO start-up time is 5.39ns, and has a phase noise of −90dBc/Hz at 1MHz offset for 4.5GHz LO with output power of −2.1dBm. The peak current is 40mA. The transceiver IC is implemented in a 0.18µm CMOS technology. The chips are housed in a QFN48 package and mounted on Rogers PCB for evaluation. A transmitted data pattern (at the TX input), received pulse pattern (at the RX input), and demodulated data pattern (at the integrator output) are shown in Fig. 6.2.6. Also a measured ranging result is illustrated where the measured time delay is 14.9ns which corresponds to the ranging distance of 223.5cm. Furthermore, the system can achieve 0.2ns resolution which translates to two-way ranging accuracy of 3cm [1]. The transceiver performance is summarized in Fig. 6.2.6. Targeting low-cost and high-energy-efficiency implementation, it achieves 0.74nJ/pulse for TX and 6.5nJ/pulse for RX while occupying 4.5mm² of die area. The chip micrograph is shown in Fig. 6.2.7. References: [1] IEEE P802.1.4a/D6, Part 15.4, “Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs): Amendment to add alternate PHY,” Dec. 2006. [2] F. S. Lee and A. P. Chandrakasan, “A 2.5nJ/b 0.65V 3-to-5GHz Subbanded UWB Receiver in 90nm CMOS,” ISSCC Dig. Tech. Papers, pp. 116-117, Feb. 2007. [3] D. D. Wentzloff and A. P. Chandrakasan, “A 47pJ/pulse 3.1-to-5GHz AllDigital UWB Transmitter in 90nm CMOS,” ISSCC Dig. Tech. Papers, pp. 118-119, Feb. 2007. [4] J. Ryckaert, G. van der Plas, V. De Heyn et al., “A 0.65-to-1.4nJ/burst 3to-10GHz UWB Digital TX in 90nm CMOS for IEEE 802.15.4a,” ISSCC Dig. Tech. Papers, pp. 120-121, Feb. 2007. [5] Y. Zheng, K.-W. Wong, M. Annamalai et al. “A 0.18µm CMOS Dual-Band UWB Transceiver,” ISSCC Dig. Tech. Papers, pp.114-115, Feb. 2007. • 2008 IEEE International Solid-State Circuits Conference ©2008 IEEE ISSCC 2008 / February 4, 2008 / 2:00 PM Mixer 3ROH=HUR0DS ADC VGA LPF Antenna RX data %E %E Ranging Squ 'LJ 'LJ RC Clk 0RG 0RG LA RX LO_Q )LUVWRUGHU ,PDJLQDU\$[LV %LTXDG ADC RX LO_I %XIIHU VGA LPF LNA [ 5HDO$[LV [ %36)DQGPRGXODWRU Squ Switch 5/ Baseband Processor Coarse tuning 2XW buffer Muti-tone VCO Burst control To TX To RX buffer Modulator BPSF 2XW FWUO /R /R 0 RXW / 0 0 ,Q 6 0 0 RXW FWUO %E TX Clk 0 / %E Mixer DA 5/ /R To TRX FWUOBE FWUOBE Ranging « Fine tuning Frequency Generator 9GG 9GG ADC « Mul LPF3 Receiver (Rx) ,Q ,GG TX LO Transmitter (TX) TX data 8SFRQYHUWHU PL[HU Figure 6.2.2: Transmitter circuits. Figure 6.2.1: 802.15.4a BPM-BPSK UWB Transceiver System Architecture. /%+% &K6HO // // 9RXWO 9RXWK 9RXWO 9RXWK 9 9 0 5)6ZLWFK 5)6ZLWFK &QWUO /1$VHFRQGVWDJH 9RXWO 9GG 9GG /% & K6HO +% & K6HO / / / / &DS $UUD\ 9/ 0 0 9 9 9/ 9+ 9RXWK 9RXWK +LJK%DQG 6HFRQG6WDJH &KDQQHO 0L[LQJ SDLU &KDQQHO 6HOHFW &DS $UUD\ 0 9RXWO /RZ%DQG 6HFRQG6WDJH 0L[LQJ SDLU 6HOHFW %DQG 6HOHFW /RZ%DQG )LUVW6WDJH 9 0 +LJK%DQG )LUVW6WDJH 9+ 9RXW4 3RZHU GRZQ &RQWURO 0 0L[HU ,QSXW WUDQVFRQGXFWDQFH 6WDJH 3RZHU GRZQ &RQWURO (QDEOH 9RXW4 9/2, 0 9/2, 9 9 9/ 9+ 0 9/24 0 9/24 9/ 9+ 9 'ULYHUDPSOLILHU 9RXW, 9RXW, &DSDFLWLYH&URVVFRXSOHG ,QSXWVWDJH &QWUO VHOHFWVWKHEDQGRIRSHUDWLRQ 0 9FWK 9FWK 9FWK 9LQ 9LQ 9FWO 9FWO 9LQ (QDEOH /1$ 9LQ /1$LQSXWVWDJHDQGILUVWVWDJH Figure 6.2.4: Multi-channel front-end circuits. 9'' / 2ns /RFNGHWHFWRU Time domain pulse (channel 9: 7.9872GHz) RBW 1 MHz Ref Lvl -41.67 dBm VBW 1 kHz -20 dBm 4.50300601 GHz SWT 19 s RF Att Unit 10 dB RBW Marker 1 [T1] dBm 1 MHz Ref Lvl -41.06 dBm VBW 1 kHz -20 dBm 7.98797595 GHz SWT 19 s RF Att Unit )L[HG 10 dB 0 0 5)B, ·WR· · 3URJUDPPDEOH 763& FCC UWB Band Spectrum Mask A -30 1 40 FCC UWB Band Spectrum Mask -50 &0/ -70 -80 90 -90 00 -100 7[5[6HOHFW &RDUVH WXQH E )LQH WXQH VWDJHV 5LQJ 2VFLOODWRU ,4 ,4 )UHTXHQF\ 0 0 9LQ ,4+% 'RXEOHU 5[0L[HU Start 2.5 GHz 750 MHz/ Stop 10 GHz 5)B4 0 0 4XDGUDWXUH )UHTXHQF\*HQHUDWRU Start 2.5 GHz Figure 6.2.3: Measured transmitted pulses and their spectra. 750 MHz/ 9R 9R 0 0 9 9LQ 'HOD\FHOO 9R 9R 0 0 7[0L[HU ,4/% -120 20 9'' %DQG6HOHFW (QDEOH -110 10 5)B4 9FWUO 80 0 )UHTXHQF\'RXEOHU $'LJLWDO)UHTXHQF\7XQLQJ/RRS 1AP -60 70 /2B, 0 · &0/ &026 Channel 9 Mask 1AP 60 1 -40 Channel 3 Mask 50 0 0 dBm A 30 5)B, 0 0 -20 20 /2B, /2B4 0 0 /2B, · Frequency domain PSD Frequency domain PSD Marker 1 [T1] 49&2 ELWV ,4 Time domain pulse (channel 3: 4.4928GHz) /2B4 /2B4 0+] BPSK modulation RXWS '$& ELWV ELW &RXQWHU ODWFK )UHT 'HWHFW 5 RXWQ )LQHWXQH &U\VWDO 5HI 9 9 9R &RDUVH 7XQLQJ FRQWURO 9R 9 9 9 9 9R 9R 9 9 49&2&LUFXLWV Stop 10 GHz Figure 6.2.5: Multi-tone frequency generator. Continued on Page DIGEST OF TECHNICAL PAPERS • 7 Amplitude (500mV/) ISSCC 2008 PAPER CONTINUATIONS Clock Input ∆t=14.9ns Modulation signal Tx_clk ∆d=223.5cm Received pulse Rc_clk Squarer output Driver Amplifier Received BPSF/TX Mixer LNA SPI Pulse Demodulation output Time (20ns/) Peak PRF: 499.2/1000MHz Modulation: BPM-BPSK BW: 499.2/1331.2MHz Energy/pulse: 0.74nJ/[email protected] Pulse duration: 2/1ns Start-up time: 6.9ns Receiver Receiver gain (LB/HB): Noise Figure (LB/HB): Sensitivity (LB/HB): IIP3: Energy/pulse: Start-up time: 80/90dB 8.2/9.4dB −75/−70dBm −12/−8dBm 6.51nJ/[email protected] 25.5ns Figure 6.2.6: Measured transceiver performance. 8 LPF Measured two-way Ranging (15.6Mb/s, LO 4.49GHz): ∆d=∆t×c/2; ∆d: object distance, ∆t: time delay, c: velocity of light. Measured Receiver BPSK demodulation (31.2Mb/s, LO 7.89GHz) Transmitter RX Mixer Freq. Tuning Loop QVCO Overall VGA VDD: 1.8V(can be as low as 1V) Technology: 0.18µm CMOS Freq. generator: Ring QVCO based Freq range: 3 to 9GHz/12 channels Ranging accuracy: 3cm Die size (die size): 4.5mm² Reserved for Integrating ADC and Digital Baseband etc. Ranging Integrator Figure 6.2.7: TRX chip micrograph. • 2008 IEEE International Solid-State Circuits Conference ©2008 IEEE