* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Implementation of Digitally Controlled Phase Shift Full Bridge

Standing wave ratio wikipedia , lookup

Regenerative circuit wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Coupon-eligible converter box wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Power MOSFET wikipedia , lookup

Index of electronics articles wikipedia , lookup

Phase-locked loop wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Radio transmitter design wikipedia , lookup

Surge protector wikipedia , lookup

Voltage regulator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Wilson current mirror wikipedia , lookup

Operational amplifier wikipedia , lookup

Current source wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Integrating ADC wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Opto-isolator wikipedia , lookup

Current mirror wikipedia , lookup

Power electronics wikipedia , lookup

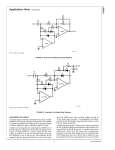

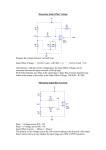

Implementation of Digitally Controlled Phase Shift Full Bridge Converter for Server Power Supply Je-Hyung Cho, Hyun-Wook Seong, Shin-Myung Jung, Jin-Sik Park, Gun-Woo Moon, Myung-Joong Youn KAIST Department of Electrical Engineering, KAIST, 335 Gwahangno, Yuseong-gu, Daejeon, Republic of Korea E-mail : [email protected] Abstract -- The digital controller of the phase-shift full bridge converter for a server power supply is designed and implemented in this paper. Analog controllers are replaced by single MCU (micro controller unit) that not only manages the protection or the operational flow of a power supply but also controls the converter. Voltage mode controller is designed based on the z-domain small signal model considering effect of variation on output filter inductance. Moreover, gain scheduling is applied to adjust the controller gain according to load current. The current offset flowing through a magnetizing inductor is eliminated by adding PI compensator instead of inserting a blocking capacitor that may increase loss, cost, and volume. The saturation of a transformer and the conduction loss due to the current offset can be prevented. The performance of designed controller is verified by the experiments on 1.2kW phase-shift full bridge converter. Index Terms-- adaptive control, digital control, gain scheduling, magnetizing current offset, phase shift full bridge, server power supply I. INTRODUCTION Nowadays, internet is one of the most essential services in everyday life. E-mail, social networking services, internet banking, online shopping, and even TV broadcasts are provided on the internet. Data centers and servers are required to supply internet services. The market of the data server is steeply increasing as various internet services like portal sites, on-line games and on-line date storages are supplied. Accordingly, demands on power supplies for the server system have also grown rapidly. The server power supply handles from 600 W to 3 kW. The distributed power system (DPS), composed of PFC stage and frond-end DC-DC stage, is widely used for the server power supply. High power density, efficiency, performance and reliability are required for the power supply. The power density is increased continuously and it is over 30 W/in3 in state-of-the-art products. The efficiency is regulated by the CSCI (Climate Savers Computing Initiative) regulation to prevent global warming. It is increased up to 91% for the full load condition. The reduction in loss is also a critical problem to increase the power density. The output voltage variation should be regulated within 5% of the output voltage under 50% load change. Since the space is limited to achieve high 978-1-4244-5287-3/10/$26.00 ©2010 IEEE power density, it is not possible to use sufficient capacitors for reduction in output voltage fluctuation under the load variation. It is necessary to design a proper controller widening a bandwidth to reject the disturbances effectively. For maintaining high reliability, the redundant structure is used. An extra module is provided for the cases one of the power supply modules is suddenly out of order. And MCU manages the operation and the status of the server power supply, and communicates with other MCU and the host. In the server power supply, MCUs have been dedicated to the mentioned functions. However, digital control utilizing the MCUs for the in power supplies becomes an attractive candidate for the sever power supply since the performance of MCU is improved and the cost is lowered rapidly. MCU can be used not only for the management but also for the control of power converters. Moreover, the built-in enhanced peripherals are supported like ADC (analog to digital converter), PWM (Pulse width modulator), and SCI (serial communication interface) which are required for control and communication. Thereby, the analog controller for a converter and a current sharing controller for multiple server power supplies can be removed. That helps the increment in the power density and the decrement of the cost. The digital control for high frequency AC-DC and DCDC converters and related issues have been researched for last ten years [3]-[12]. For non-isolation type converters, especially PFC (power factor correction) converters and POL (point-of-load) converters, various digital control techniques have been proposed. Differently from the PFC stage, the frond-end DC-DC stage consists of an isolation rectifier. Among various isolation type converters, the phase shift full bridge converter [1] is attractive for the DC-DC stage of the server application. Since it is similar to the buck converter from the point of view on the secondary rectifier, the control strategy for a buck converter can be applied. Although studied digital control methods for non-isolation type converters are applicable to isolation type converters, several issues from the existence of an isolation transformer should be considered. One of the issues is the magnetizing current of the transformer which rarely exists in non-isolation type. When the control is performed based only on the 802 information from the secondary side such as an inductor current and an output voltage like in a buck converter, the primary current is not controllable for lack of information of the primary side. As the magnetizing current offset occurs, conduction losses and switching losses are increased. In worst case, components may be destroyed by the over-current caused by the saturation of the transformer [14], [15]. Consequently, the magnetizing current offset should be eliminated to prevent from lowering efficiency and reliability. The design and implementation of the digital controller for a phase shift full bridge converter are presented in this paper. The controller is designed as a voltage mode controller considering the variation on the output inductor. Moreover, the magnetizing current offset is also researched to provide reliability and to prevent from lowering efficiency. II. DESIGN OF DIGITAL CONTROLLER Fig. 1 shows a digital control system for a phase shift full bridge converter. Since the primary side and the secondary side of the phase-shift full bridge converter are electrically isolated by the transformer, the controller is located on either the primary side or the secondary side. In DC-DC stage of the server power supply, many signals for the communication with a host and signals related to hot-swap and current sharing operation, are located in the secondary side. Therefore, MCU is placed on the secondary side to reduce components used for the isolation. One isolation device is used to transfer four gate signals to the primary switches. Synchronous rectifier is adopted to reduce the losses from a diode forward drop since the high current is flowing in the secondary side. The gate signals for synchronous rectifier are generated in MCU. A. Selection of Control Method To determine the type of a controller, the specification of the server power supply is considered. An important requirement is the output voltage regulation under the load transient which is fast and frequent. Since the power supply for a server system is designed to have high power density, it is not recommended to add excessive capacitors to improve the load transient characteristic. Therefore, one important role of controller is the achievement of high bandwidth of the voltage loop up to 10 kHz to satisfy the dynamic load transient specification. Various control methods can be considered for the controller of the phase shift full bridge converter. Voltage mode control and current mode control are typically used in products. Item Vs Vo Po fs Fig. 1. Block diagram of digital control system for phase shift full bridge converter For the digital control of the phase shift bull bridge converter, voltage mode controller, which does not contain an inner current loop, is employed to maximize the bandwidth of the voltage loop within the performance of a microprocessor. Since the phase shift full bridge converter operates around 100 kHz, the switching frequency of an output filter is 200 kHz. Practically, only 50 ~ 60% of the time is permissible for the computation. The remained time is reserved for communication, protection, monitoring and the interrupt latency. The number of clock for 60MHz processor usable during 3μs, which is 60% of 5us, is only 200 clocks. Therefore, a sampling and a control routine can be executed only once during half period. It is well-known that the sampling frequency must be 10 times higher than the closed loop bandwidth when the controller is designed by the frequency response method [3]. The upper bound of the system bandwidth is limited to 20 kHz. Moreover, the digital system has less phase margin compared with an analog controller when it is compensated by conventional methods, poles and zeros insertion, since the computational delay and the ZOH (zero-order hold) result in a phase lag. From these reasons, it is hard to insert a current loop whose bandwidth is 5 to 10 times higher than that of a voltage loop. Therefore, the voltage mode controller is designed in this paper. B. Variation of Output Inductance The voltage mode controller is designed based on a small signal mode. The small-signal model Gd(s) is analyzed as (1). The complex poles are determined by output inductor L, output capacitor C, load resistor R, and leakage inductance Llkg. Vin and fs denote the input voltage and the switching frequency respectively. TABLE I SPECIFICATION OF SERVER POWER SUPPLY Specification Item Specification Load Transient 400Vdc ΔVO < ΔIO=50A with 600mV 12 ± 5% Vdc 0.25A/μs 1200W Phase margin 45° 85kHz Gain margin Gd s vˆo nV 1 in ˆ R 1 LC 1 Rd d eff d 1 s2 s RC L LC R (1) where Rd 4n 2 Llkg f s 6dB The permeability of the output inductor, CS270075, is 803 shown in Fig. 2 [16]. When the load current is changed, the inductance of the output inductor is changed since the inductance is proportional to the permeability. Measured inductance according to the load current is shown in Fig. 3. As load current increases, the inductance decreases. Fig. 4(a) shows the transfer function Gd(s) with the constant output inductance. Fig. 4(b) shows the transfer function Gd(s) considering the variation of the output inductance. Comparing two cases, the location of double poles is moved to lower frequency as the load becomes lighter. Consequently, phase lag increases and the gain near the desired bandwidth, 10 kHz, decreases. The locations of complex poles are affected by the output inductance and the output inductance varies 30~50% according to the load condition. The gain at the full load condition is 1.9 times larger than that at the no load condition. Accordingly, the effect of the variation on the output inductance must be considered to design a controller. C. Design of Voltage Mode Controller The derivation of the z-domain small signal model for the phase shift full bridge converter Gd(z) is necessary to design a digital controller Gc(z). The discrete-time small signal model can be calculated from the analog small signal model of (1). As mentioned above, time for multi sampling is not enough so that the maximum sampling rate is limited to twice of the switching frequency. The sampling frequency is selected as the maximum rate, 2fs. ZOH and computational delay should be considered to obtain the z-domain model [3], [4]. The z-domain model can be achieved from (2) with the specifications of Table I. Since it is complicated to derive the z-domain transfer function directly [6], the transfer function is calculated using various transformations [3]. The z-domain transfer function at the full load condition is calculated as (3). 1 e sTs / 2 sTd e Gd s Gd z Z s 0.1686 z 0.1686 Gd ( z ) full load z 1 2 z 1.869 z 0.8914 (2) (3) 1 e sTs represents the effect of a ZOH and e sTd s stands for the computational delay. Since the operating frequency of the output filter stage is twice as the switching frequency, the time step for ZOH and the computational delay is Ts/2, not Ts. When one-step delay is used, then Td = Ts/2. Z-domain transfer function Gd(z) is drawn in Fig. 5 and 6. The phase continuously decreases by the effect of ZOH and the computational delay. As mentioned previously, the variation on the output inductance affects the parameter of the transfer function. The effect is considered to design the controller. In Fig. 4(b), the gain and the phase have the smallest value at the no load condition. Accordingly, it is the worst case in aspect of the gain. The controller is designed to satisfy the specifications in the worst case. 3zeros are inserted to compensate the plant poles and boost the phase. An integrator is added to remove In (2), Fig. 2. Variation on permeability Fig. 3. Output inductance according to load current Fig. 4. Bode plot of transfer function Gd(s) 804 ( z 0.813)( z 0.894)( z 0.985) z ( z 0.691)( z 1) (4) Phase (deg) Gc z 31 Magnitude (dB) steady state error. One pole is located at high frequency to guarantee the gain margin. The other pole is inserted to match the order of the denominator and the numerator. The result is shown in Fig. 5 and expressed as (4). Kd is the output voltage sensing gain and equals to 0.0667. Phase margin is 51.6 deg and gain margin is 6.87 dB with 10 kHz bandwidth. Now, the designed controller is used for the full load condition without modification. As shown in Fig. 6, the converter becomes unstable for lack of the gain margin and the phase margin. The gain has to be reduced to satisfy the requirement of the gain margin and the phase margin as depicted in Fig. 6. The controller for the full load is expressed as (5). Phase margin is 61.7 deg and gain margin 7.18 dB with 10.5 kHz bandwidth. Gc z 17 ( z 0.813)( z 0.894)( z 0.985) z ( z 0.691)( z 1) Fig. 5. Bode plot of designed controller under no load 40 Gd(z) 20 Gain : 31 0 (5) -20 GM : 7.18 dB Gain : 17 Kd * Gc(z) BW : 10.5 kHz BW : 18.8 kHz -40 90 D. 0 -90 PM : 20.6 deg -180 PM : 61.7 deg -270 2 3 10 4 10 10 5 10 Frequency (Hz) Fig. 6. Bode plot of designed controller under full load Controller Gain Gain Scheduling The gain of the controller is fixed for all load conditions in previous works [6], [7]. However, the modification of the gain is necessary as shown in the design procedure performed previously. When the controller is designed for the full load condition, designed gain has the minimum value. The plant can operate stably under all load conditions with this controller. Nevertheless, the gain is not sufficiently large to satisfy the bandwidth under light load conditions. On the contrary, designed gain has the maximum value if the controller is designed for the no load condition. Although this controller satisfies the bandwidth requirement for the light load condition, it makes the converter unstable when the load current increases since the phase margin decreases. Consequently, the gain of a controller must be changed in accordance with the load current to keep the converter stable while sufficient bandwidth and phase margin are preserved. As well as the gain of the controller, the location of compensating zeros affects the bandwidth and the phase margin of the system. Since the location of double poles is moved as the load changes, it is effective to modify the location of compensating zeros in conformity to the change of the load current. However, that increases the complexity of a control since the location of each zero affects to bandwidth, gain margin and phase margin simultaneously. To reduce the complexity of an adaptive controller, zeros are designed and fixed to be compatible with all load range. From above, the parameter to be modified according to the load current is limited to the gain of the controller. Gains are designed for various load conditions considering the variation of the output inductance as Fig. 7. Since the output inductor current is already sensed for monitoring and protection, it is used for the gain scheduling instead of Kd*Gd(z)*Gc(z) Fig. 7. Required gain according to load sensing the load current. Ki represents a current sensing gain and iL.sense[n] represents sensed current processed in MCU. Gc z Gain ( z 0.813)( z 0.894)( z 0.985) z ( z 0.691)( z 1) Gain 30.545 0.1455 iL.sense [n] / K i (6) (7) This gain scheduling technique is adopted to maintain the required bandwidth and phase margin for the large load variation causing the variation of the output inductance significantly. For applications which do not need wide bandwidth, this gain scheduling may not be much attractive. The gain is designed for the full load condition for that case. 805 III. MAGNETIZING CURRENT OFFSET In a full-bridge converter, the magnetizing current of a transformer has an offset when the voltage-second product of a magnetizing inductance is not balanced. The solutions to remove the offset of a transformer have been studied [12][15]. Simply, a blocking capacitor is connected in series with the transformer to prevent the imbalance of the transformer current. However, that lowers the efficiency and the power density due to the insertion of an additional component. It is desirable to eliminate the offset by the control without adding any external components. The duty cycle during the first and the second power transfer is slightly modified in the direction of the magnetizing current offset decreasing [12]. It is simple and intuitive method, however, the design guideline is not presented in [12]. If the modification of the duty ratio is too fast or too large, it affects to the output voltage regulation what is not expected. In this paper, the guideline for designing compensator to suppress the magnetizing current offset will be presented based on the derived model. To implement the mentioned solution, the primary current must be sensed. In many server power supplies, the primary current is sensed using a current transformer and external circuits for a protection and monitoring functions. The circuit and its sensed waveform are shown in Fig. 8. The primary current is sensed twice in a period. If the offset occurs, then the difference between the first sensed current and the second sensed current will come out. It is possible to determine the amount of the magnetizing current offset by comparing these two sensed signals. The small amount of duty cycle is modified to remove the offset in the direction the current offset decreases. The design guide on the magnitude and the speed of the modification on duty cycle should be considered to keep the voltage loop stable while the magnetizing current offset is compensated. The model for the magnetizing current offset is derived to design the proper offset compensator. A. Derivation of Magnetizing Current Offset Model The magnetizing current offset is generated by the difference of the voltage-second product between the first and the second power transfer of one period. The difference is come from the voltage difference applied to the magnetizing inductor and the disparity between time durations of the first and the second power transfer. The imbalance of the voltage-second product occurs from several reasons. In [13], it is reported that the parameter tolerance of MOSFETs and output diodes practically do not affect on DCDC converter unbalancing. Other reason to induce the offset is transient. When the duty ratio is suddenly changed to reject the disturbances, the bias is generated on the flux of the transformer so that the current offset takes place [14]. The difference between the first and the second powering time causes the offset. Since generated PWM signals and the gate drivers are not identical, the small difference in powering time continuously exists. That makes the offset be generated. Fig. 8. Sensing circuit and waveforms The effect of unbalanced powering time is considered in Fig. 9. The effect of transition periods due to the existence of parasitic components is neglected to simplify the analysis. The duty cycle of the first powering is D1[n] and that of the second powering is D2[n] for n-th interval. The difference between D1[n] and D2[n] is defined as Δd[n] which causes the offset. The voltage across the magnetizing inductor during the power transfer, which is equal to the input voltage, causes linear increase in the magnetizing current. Zero voltage applied during freewheeling makes the magnetizing current keep constant. As shown in Fig. 9, the magnetizing current offset is described as follows. ios [n] ios [n 1] ios [n] Vin d [ n]Ts 2 Lm (8) Equation (8) is transformed to (9) by the z-transformation. I V T os in s 1 D 2 L z 1 m (9) As shown in (9), the magnetizing current offset is modeled as single integrator since only the magnetizing inductor is considered to derive the small signal model. The bode plot is shown in Fig. 10. The magnitude decreases linearly and the phase also decreases as frequency increases. To compensate the offset based on this model, Pcontroller is enough if the bandwidth is determined under several kHz since the phase margin is guaranteed up to that point as shown in Fig. 10. The product of the gain of the Pcontroller and the sensing gain of primary current Kpri having a 500 Hz bandwidth is 0.0229 as Fig. 10. The experimental results with P-controller will be shown in chapter IV. K pri.sense Gc.os ( z ) 0.0229 (10) It can be seen that there still remains small offset although it is considerably removed compared with the case without any compensation. This is because the single integrator model having an infinite DC gain is not exact. If the offset 806 really features as a perfect integrator, the magnetizing current will increase infinitely when even the small difference on the duty cycle is continuously applied. And the magnetizing current should keep the injected disturbance. However, the effect of suddenly injected disturbances is practically diminished by the parasitic resistance that behaves like negative feedback. And the experimental results show that the magnetizing current saturates with a finite offset in normal operating condition despite of the small duty difference realistically generated by the gate driver and turnon/off delay of switches. That means the small signal model caused is not a perfect integrator. The above mentioned features indicate the model has a finite DC gain and low frequency pole. Therefore, the model is modified as (11). I V T os in s 1 D 2 L z p1 m Fig. 9. Offset generation due to unbalanced duty (11) This is because the negative feedback effect which resides naturally in transition period by the parasitic components. Assume that the first powering time is larger than the second powering time, that is, Δd[n] is positive as Fig. 11. Then, the magnetizing current offset starts to appear and the offset makes the primary current flowing during the first half larger than that of the second half. ZVS transition time for switch Q1 and Q4 is less than that for Q2 and Q3. It makes larger duty loss in the first half. From this, the effect of the duty difference is reduced due to the transition. Consequently, the system pole is moved from z=1, which indicates an integrator, to low frequency pole z=p1. Insertion of an integrator is necessary to remove steady-state error completely. Thus, PI controller is adopted to remove the magnetizing current offset. Fig. 10. Bode plot of magnetizing current offset model D1Ts Q2 Q1 Q3 Q4 vDS2 vDS1 vDS3 (C) PI Compensator to prevent Magnetizing Current Offset PI controller is inserted in the controller. By sensing and comparing the primary peak currents of the first and the second power transfer, isense1[n] and isense2[n] in Fig. 8(b), the magnitude of the offset is acquired. vDS4 (A`) (A) B. iOS isense1[n] isense 2 [n] / 2 (B`) vLlkg (D) ipri i1H i2H (B) vLm iLm i1L tlag2 (12) The purpose of the controller is to balance the peak of the primary currents since the output inductor current of the first and the second powering are not much different. The peak value is sensed twice in a period, and the difference between the peak current of the first and the second is defined as error, which is an input of compensator. The compensator output, Dcomp[n], is added to D2[n+1] or Dcomp[n]/2 is subtracted to D1[n+1] and added to D2[n+1]. The magnitude of the compensator output Dcomp[n] is relatively small compared with the duty cycle so that it does not have a decisive effect on controlling the output voltage. To design PI controller, the location of the pole p1 is considered. The location of the low frequency pole is determined by various reasons. The factors affecting the D2Ts dTs teff1 tlead1 tlag1 teff2 tlead2 i2L tlag2 Fig. 11. Effect of transition period location of p1 are similar to the factors influencing the transition of the converter. They are load condition, dead time, magnetizing inductance, input voltage, parasitic components like parasitic capacitance, leakage inductance and so on. The pole location is not higher than 1 kHz with the specification of Table I. One integrator is inserted to remove steady state error and one zero is inserted to guarantee the phase margin. The worst case for the design is when the system pole exists in the lowest frequency in aspect of the phase margin. Therefore, the compensator is designed for the single integrator model. The bandwidth of the compensator is selected below 500 Hz which is 20 times lower than that of the voltage mode control loop. The magnitude of the compensation duty Dcomp[n] is limited to 5% of nominal duty 807 ipri.sense Current Sensing Circuit Q1 Gd(s) Q3 L Ipri 1 VS Q2 QB n vO Current Monitor C R n Kd Q4 QA Ki DRIVER ADC ADC DRIVER iL.sense[n] D Isolation vO[n] Gain Scheduling PWM Hc D[n] Gc(z) e[n] ZOH Dcomp[n] ipri.sense Kpri Gc.os(z) vref MCU Magnitude (dB) Fig. 13. Block diagram of overall system Parameter Kd Ki Kpri Phase (deg) B. Fig. 12. Bode plot for PI offset compensator cycle. The designed results are shown in Fig. 12(a). The phase margin and the bandwidth are 87.4 deg and 506 Hz respectively. When the location of system pole is moved to 1 kHz, the bandwidth of the compensated loop decreases to 8.37 Hz as Fig. 12(b). Since the bandwidth is not a critical issue for this compensator, the offset compensator (13) is used without modification for all conditions. K pri Gc.os ( z ) 0.0229 z 0.9991 z 1 (13) IV. EXPERIMENTAL RESULTS A. Overall System The control system for the phase shift full bridge converter is shown in Fig. 13. As designed so far, the system contains a voltage mode controller adopting the gain scheduling technique and the magnetizing current offset compensator. The voltage mode controller and the gain scheduling law are executed twice a period. TABLE II SYSTEM PARAMETERS Value Component 0.0667 L 0.009 C 0.0952 n Value. 1.2 μH 1650 μF 1/24 Experimental Results 1.2kW industrial sample is used to verify the designed controller. The digital controller is implemented using TMS320F28027 whose core clock is 60 MHz from Texas Instrument. Fig. 14 shows the load transient waveforms with fixed gain controller of (5). For stable operation, the gain is selected as the minimum value Gain=17. The transient specification is satisfied under half and full load transient in Fig. 14(b)-(d). However, the voltage dip is larger than 600 mV when the load is changed from no load to half load. Since no load condition is the worst case in the aspect of the phase margin and the gain, the largest voltage spike occurs. Fig. 15 shows improved load transient responses with the gain scheduling. Differently from the fixed gain controller, the output voltage remains within ±5% of the regulated voltage. The gain is modified from 17 at the full load condition to 31 at the no load condition as (6) and (7) so that the load transient specification is satisfied and the converter operates stably under all load ranges. Fig. 16 shows the primary current of the converter. As stated above and shown in Fig. 16(a), the primary current has the magnetizing current offset when the control is performed based only on information from secondary side. The P-controller is designed based on the single integrator model (9). The offset is improved considerably compared with the non-compensated case in Fig. 16(a). There still remains a small amount of the current offset in Fig. 17. To eliminate the offset completely, PI controller in (13) is used. The magnetizing current offset is removed perfectly as Fig. 17. From the experimental results, both P- and PIcompensator remove the magnetizing current offset effectively. 808 ipri [5A/div] 5.5A 6.5A 5ms/div 5μs/div (a) Natural Condition ipri [5A/div] 6A 6A 5ms/div 5μs/div (b) P - controller ipri [5A/div] 6A 6A Fig. 14. Transient response with constant gain 5ms/div vo [200mV/div] vo [200mV/div] Io [50A/div] Io [50A/div] 200us/div 5μs/div (c) PI - controller Fig. 16. Magnetizing current offset under full load 200us/div vo [200mV/div] vo [200mV/div] Io [50A/div] Io [50A/div] 200us/div (c) 50 → 100A Transition 200us/div (d) 100 → 50A Transition ios (mA) (b) 50 → 0A Transition (a) 0 → 50A Transition Fig. 15. Transient response with gain scheduling Fig. 17. Magnetizing current offset V. CONCLUSION [5] Digital controller for the phase shift full bridge is designed and implemented. The proposed digital controller regulates the output voltage variation tightly within 5% of the output voltage when the load current is changed 50%. The offset of a magnetizing current is eliminated using P or PI compensator so that the core saturation and high thermal & current stress are prevented. Moreover, the gain scheduling is applied to compensate the effect of the variation on the output inductance. To verify the performance of the designed controller, 1.2kW industrial sample is experimented with the designed digital controller. The digital control using MCU is promising for the server power supply system. REFERENCES [1] [2] [3] [4] [6] [7] [8] [9] [10] [11] [12] J. A. Sabate, V. Vlatkovic, R. B. Ridley, F. C. Lee, and B. H. Cho, “Design consideration for high-voltage high-power full-bridge zerovoltage-switched PWM converter,” in Proc. IEEE APEC, 1990, pp. 275-284. V. Vlatkovic, J. A. Sabate, R. B. Ridley, F. C. Lee, and B. H. Cho, “Small-signal analysis of the phase-shifted PWM converter,” IEEE Trans. Power Electron., vol. 7, no. 1, pp. 128-135, Jan. 1992. Y. Duan and H.Jin, “Digital Controller Design for Switchmode Power Converters,” in Proc. IEEE APEC, 1999, pp. 967-97. S. Choudhury, “Designing aTMS320F280x Based Digitally Controlled DC-DC Switching Power Supply,” TI Application Report SPRAAB3, Jul. 2005. [Online]. Available :http://focus.ti.com/general/docs/litabsmultiplefilelist.tsp?lite ratureNumber=spraab3 [13] [14] [15] [16] 809 P. F. Kocybik and K. N. Bateson, “Digital Control of a ZVS FullBridge DC-DC Converter,” in Proc. IEEE APEC, 1995, pp. 687-693. J. G. Lim and S. K. Chung, "Digital Control of Phase-Shifted FullBridge PWM Converter," Journal of Power Electronics, vol. 8, no. 3, pp. 201-292, Jul. 2008. L. Corradini and D. Maksimovic, "A digital pulse-width modulator for phase-shift operation of full-bridge isolated DC-DC converters," in Proc. IEEE APEC, 2010, pp.277-283. D. Maksimovic, R. Zane, and R. Erickson, “Impact of digital control in power electronics,” in Proc. ISPSD, 2004, pp. 13-22. J. Chen, A. Prodic, R. W. Erickson, and D. Maksimovic, "Predictive digital current programmed control," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 411-419, Jan. 2003. S. Chattopadhyay and S. Das, "A Digital Current-Mode Control Technique for DC–DC Converters," IEEE Trans. Power Electron., vol. 21, no. 6, pp. 1718-1726. Nov. 2006. A. V. Peterchev and S. R. Sanders, "Quantization resolution and limit cycling in digitally controlled PWM converters," IEEE Trans. Power Electron., vol. 18, no. 1, pp. 301-308, Jan, 2003. E. S. Kim, T. J. Kim, Y. B. Byun, T. G. Koo, and Y. H. Kim, “High power full bridge DC/DC converter using digital-to-phase-shift PWM circuit,” in Proc. IEEE PESC, pp. 221-225. B. A. Gesev, V. I. Meleshin, and D. A. Ovchinnikov, “Transformer Core Unbalancing Issue in a Full-Bridge DC-DC Converter with Current Doubler Rectifier,” in Proc. PEDES, pp.1-6. J. A. Claassens and I. W. Hofsajer, “A flux balancer for phase shift ZVS DC-DC converters under transient conditions,” in Proc. IEEE APEC, 2006, pp. 523-527. T. Kohama, S. Tokimatsu, and H. Shimamori, “Elimination of magnetic saturation due to fast dynamic response in DC-DC converter,” in Proc. INTELEC, 2009, pp. 1-6. “CSC MegaFlux Material”, Mar. 2007. Available : http://www.mhwintl.com/assets/CSC/MegaFlux%20Material%20March%202007.pdf