* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download DESIGN, DEVELOPMENT, CONSTRUCTION AND

Survey

Document related concepts

Transcript

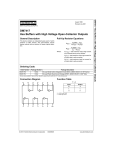

DESIGN, DEVELOPMENT, CONSTRUCTION AND COMMISSIONING OF A LOCAL PARLIAMENTARY VOTING SYSTEM By H.E. Orovwode (MNSE) [email protected] and S.T. Wara (PhD, FNSE, R. ENG) [email protected] Product Development/Energy Centre, College Of Engineering, Department of Electrical and Electronics/Computer Engineering Igbinedion University, Okada, Nigeria. ABSTRACT: The need to concretize our democratic structure has led to the design, development, construction and commissioning of a local parliamentary voting system. The system has ability to accredit voters, permit only accredited voters to vote, nullify multiple voting,, collate votes cast and display results. Locally available materials were used and the design was based on basic electrical and electronic principles. Operating the system is easy and anyone with little orientation can use it. The system is stable, reliable, efficient, rugged and easy to maintain by anyone who is familiar with electronic circuitry. Keywords: Accredited, Voters, For, Against, Collation, Parliament, Democracy. 1.0 INTRODUCTION Nigeria operates a three tier (LEGISLATURE, EXECUTIVE, and JUDICIARY) form of government. [11] The legislature comprise of elected representatives that makes laws for the smooth governance of the society. Here, motions are brought; debated and finally passed or rejected depending on the side the majority cast their vote. Three conditions can exist. These are:- (1) that the motion is passed (when those that voted in favor of the motion are more than those that voted against (ii) that the motion has failed (when those that voted against are more than those that vote in favor) and (iii) that the motion is tied (both sides are equal). Since the number of votes is very crucial to motion or bill passage, the house needs to count the votes correctly and guard against any form of manipulation. 1.1 FORMS OF VOTING PROCESS IN NIGERIA PALIAMENTARY HOUSES AND THEIR ASSOCIATED PROBLEMS. In present day parliamentary houses in Nigeria be it Senate, House of Representative, Local Government Area Legislative Arm; two forms of voting process were observed in the course of our research. The voting process is either by voice vote or by lifting of hands for manual counting. These results are at times difficult to collate accurately. Taking the case of voice vote for instance, those who can shout always win whether they are simple majority or not. Also in the case of lifting of hands, three problems were observed: the person who is doing the counting could make mistakes easily as a result of fatigue especially when the number is high as is the case of the House of Representative. Secondly, some may want to vote twice by raising two hands instead of one. This creates difficulty for the person counting and thirdly, lifting of hands and waiting for counting could be strenuous especially for those who might be having problem with their arms and cannot afford to lift their for more than a minute. There is also the problem of exposure, which could make one not to vote according to his/her conscience. There are situations where a member 1 who did not want to support a side now finds himself doing so simply because his friend is the mover of the motion at hand and might not be happy seeing his/her own friend voting against his/her motion since the process is not confidential. Finally, there are situations where some members may want to remain neutral (not supporting either side) hence will refuse to be accredited for the voting. On, the long run, some will suddenly decide to vote if a side is winning. This work is then aimed at giving SECRET and ACCURATE vote in a parliament when the need arises and display it taking care of the various problems enumerated above thus guaranteeing a FREE and FAIR voting system. 1.2 DESIGN APPROACH The system is designed to give a short time for accreditation, voting and disallow any person who has not been accredited initially from participating in the voting process. Also, any one who voted twice will have his/her vote nullified. Every parliamentarian thus has a dedicated terminal for simultaneous voting. The house leader presides either by choosing the automatic or manual mode from his terminal. He initiates the accreditation, voting and collation processes and as soon as the collation is completed, the system displays the results visually audibly. The display will show the number of voters accredited, number of those that voted in favour of the motion (for the motion), number of those who are against the motion and number of votes nullified. When the motion is passed, the victory tune sounds to indicate victory (applause). 1.3 FUNCTIONAL BLOCKS OF THE SYSTEM The unit consists of various blocks or subunits that are linked through cable. The block diagram of the entire unit is as shown in fig1. 1.3.1 THE POWER SUPPLY SUBUNIT. The power supply unit consists of the step down transformer, the rectifier, the filter and regulator. Its purpose is to provide a regulated dc supply for the entire system. (Fig 2) 1.3.2 THE PALIAMENTARIANS LEADER’S TERMINAL. Fig 3 shows the block diagram of the parliamentarians’ leaders’ terminal. This terminal controls the proceedings of the voting process. To effectively control the voting process, it has a mode switch which makes it possible to operate in the manual or automatic mode. In the manual mode, the leader dictates the sequence of voting by depressing the switches for ACCREDITATION, VOTING AND COLLATION in that sequence and allowing the time for each process to elapse. On the other hand, the automatic mode dictates its proceedings. By simply switching to that mode, the parliamentarians only watch for indicators and act accordingly. This mode guarantees transparency, free and fair elections free from undue manipulation. He toggles the switch to that mode and leaves his seat and all proceedings will be carried out on its own. 1.3.3 THE PALIAMENTARIAN TERMINAL. This is the unit that will be placed at the desk of each parliamentarian. The unit is to be used only for ACCREDITATION AND VOTING (either FOR or AGAINST). The accreditation as well as the voting switch is rendered inactive until the go ahead signal comes from the leader’s terminal. The signals are seen when the indicator lights comes on. The VOTING switch becomes active when the VOTING signal comes from the leaders’ terminal and the voter has been accredited initially. This prevents any one who has not been accredited initially from participating in the voting process. The voting button allows you to make one choice out of two i.e. either FOR or AGAINST. If the voter now makes both choices the detection unit will be activated and such votes will be mollified by bringing a nullified signal ON and canceling the two votes and bringing an output of ‘zero’. Fig 4 shows the block diagram of the parliamentarian’s terminal. This unit is duplicated for all the seats required. For the purpose of this work, only five terminals were built. 1.3.4 THE MAIN PROCESSING UNIT. This section is responsible for collating the results, by counting the votes as well as those accredited and nullified, displaying the counted result, decides the outcome of the vote and 2 displays it at the end of the counting process. Figure 5 shows the various sections that make up this unit. [3, 5, 7] 1.3.5 THE VICTORY TUNE MODULE. The victory tune module is to produce sounds (play tones) when the motion is passed. The block diagram of this module is as shown in fig 6 The output of the tone generator is amplified in the power amplification block and it is used to drive the voice coil speaker. [4] 1.4 DESIGN OF THE SYSTEM UNITS 1.4.1 THE POWER SUPPLY UNIT. The unit was estimated to consume a current of 600mA at 9V DC. Therefore the transformer to supply a regulated voltage of 9V, must be able to supply 11V which is the minimum voltage to the three terminal regulator used for the power regulation. Therefore a transformer is capable of supplying 12V was chosen. 1.4.2 RECTIFICATION A full wave bridge rectifier was used. IN4002 was chosen with maximum normal forward current of 2A and a peak inverse voltage (PIV) rating of 100V. 1.4.3 FILTERING CIRCUIT. An electrolytic capacitor whose value was chosen based on equation (2) was used to remove ripples from the rectified DC voltage. peak ripple voltage IT/C……………(2)[2] (p-p) = Where I is maximum current to be demanded, T is the period of the frequency of the rectified voltage (which is twice the supply frequency) C is the capacitance of the capacitor to be used as the filter. . 1.4.3 THE POWER INDICATOR Diode D5 is a light emitting diode with characteristic voltage drops in the forward based condition of 2v and Sinks a maximum current of 15mA. The colour is red. The current limiting resistor is calculated using equations 3, 4 and 5. VR = Vs – VD…………(3) VR = ID/R………… (4) R=VR / ID………… (5)[4,8] 1.4.4 REGULATION. The 7809 position three terminal integrated regulator was chosen. The voltage output is 9V and maximum current of 1A. The capacitor C2 and C3 of this unit are for transient compensation. The circuit diagram of the power supply unit is as shown in fig. 7. 1.4.5 THE PARLIAMENTARIANS LEADER’S TERMINAL The terminal has the capabilities of operating in two modes. In the manual mode, the leader initiate voting proceedings and he determines the sequence of events but cannot influence the results In the Auto Mode, the leader does not have any control over either the sequence of events or the results . This mode is used if the leader is being accused of vote manipulation. It consists of auto oscillator, a sequencer and three multivibrators. 1.4.5.1 THE AUTO OSCILLATOR The oscillator was configured using the monolithic 555 timer integrated current. The frequency is determined by the selection of R1, R2 and C1.from the f 1.44 ………… (6)[2] ( R1 2 R2 )C1 1.4.5.2 THE SEQUENCER. The sequence of events is controlled by a counter, which provides an output per clock of the oscillator. The counter used was the decade counter (4017 1.4.5.3. THE ACCREDIT ENABLE, VOTE ENABLE AND COLLATE ENABLE MULTIVIBRATORS. These are monostable multivibrator whose period is given as 1.1CTRT = Ґ………………… (7) Where CT is the timing capacitor. RT is the timing resistor. Ґ is the pulse duration. . Fig 8 shows the complete circuit diagram of the parliamentary leader’s terminal. 1.4.6 THE PALIAMENTARIAN TERMINAL This terminal allows the parliamentarian to be accredited and to vote. Flip- flop 1 (4013) is used for the accreditation. The flip-flop is set by ICTa which is an AND gate.] The voting section is built around IC5a and b while IC5a is for the FOR, IC5b is for the AGAINST. 3 Since accreditation has been acknowledged, the output of IC4 is a high. When the voting enable is triggered, pins 5 and 1 of IC1 are high and parliamentarians can now vote FOR or AGAINST the motion on ground. The combination of IC2a, IC2c and IC3a are used as anti- double vote sub system. If either of the flip-flop output is high and not both, the output of IC3a will be high and this will allow the vote ‘FOR’ or ‘AGAINST’ to pass through to the output. However if vote of the FOR or AGAINST switch is depressed or both are depressed the output of IC3a will be low hence the output of the voting will not get through. IC3b is used to check if both output of ‘FOR’ and ‘AGAINST’ are the same. If this is true, its output will be low. This will be combined with the accreditation output to provide a high to indicate the vote has been notified.[6] The complete circuit diagram of this unit is as shown in fig. 9 1.4.7 THE MAIN PROCESSING UNIT. This is the unit that processes or counts the numbers FOR, AGAINST, ACCREDITED and NULLIFIED. Multiplexes are used for this purpose. The ACCREDIT output of all the parliamentarians were connected to multiplexed 1, all NULLIFIED VOTES, FORTHE MOTION AND AGAINST THE MOTION were connected to multiplexes 2,3, and 4 respectively since their output were flip flop, the output logic is held constant while processing is taking place.[7] As the input of the multiplexers are being addressed, it connects the input to its output 1.4.7.2 THE DECISION BLOCK The final result is between FOR and AGAINST votes. A four built magnitude comparator 4585 was used to compare the output of SD1 and SD2.The outputs of the magnitude comparator has three possible output i.e. A=B, A<B, AB. [3] If A = B, then output (3) will be high. It is used to switch relay RL3 to ON the ‘TIED’ indicator. If A B, pin 13 will be high. It is used to switch RL5 to on the ‘PASSED’ indicator. If AB, pin 12 in high it switch RL4 to on the ‘FAILED’ indicator. 1.4.7.3. DISPLAY FLASHING UNIT The purpose of this unit is to flash whatever is being displayed on the board. It dose not come on except at the end of each vote processing. It is basically a free running (astable) oscillator generated using the 555 monolithic IC. The frequency of oscillation was chosen to be 1 HZ 1.4.7.4. THE SWITCHING (INTERFACE) SECTION. Micro relays were used as interface since the power to the display board is alternating current (AC) RL1 –RL5 are identical and are switched by transistors Q1, Q3 – Q6 respectively. R9, R4, R5, R10, R11 and R12 are base resistors for transistor Q1 – Q6 respectively. Since they are performing the same function their value are the same. Given as RB = VB/IB………………… (8) IB = IC / ß………….(9) [ 4] Fig 10 shows the complete main processing unit circuit diagram 1.4.7.5 VICTORY TUNE MODULE. The victory tune module is made up of three sections i.e. the tempo generator, the counter/Decoder and the note generator. The tempo generator is a free running multivibrator configured using the monolithic 555 timer. Its function basically is to clock the counter. The clocking frequency dictates how fast or slow the tempo of the tune generator will be. Components were selected based on equation (6) Each of the ten ‘count’ output of the counter/decoder IC go high (+Vcc) in turn. Counts ‘0’ to 9 are connected via diodes to resistors, which are adjusted to determine the frequency of the notes to be generated by the tone generator. The notes played by the tune model are generated by IC3, which is a monolithic 555 timer IC and its frequency is determined by the value of the particular resistor being driven by the counter/decoder. The output of the note generator is further amplified using Q1 and Q2 connected in Darlington form. The capacity of the amplifier was chosen to be 0.5W. The circuit diagram of the victory tune module is as shown in fig 11 4 1.5 FABRICATIONS AND ASSEMBLY The blocks were assembled separately as detailed in the design outlay unit by unit. Finally all unit s were coupled. Preliminary test were carried out and adjustment made where necessary on all units on a breadboard before final assembly was done on veroboard. 1.6 TESTS, RESULTS AND ANALYSIS OF RESULTS 1.6.1 THE POWER SUPPLY UNIT seconds. The COLLATE signal should be on for the time it takes to complete the collation process. TESTING THE PALIAMENTARIAN TERMINAL The test carried out on the parliamentarian terminal was to determine if the output for the ACCREDIT, FOR, NULLIFIED and AGAINST actually comes on when the appropriate conditions were applied. First, the unit was tested with out the various input (i.e. ACCREDIT and VOTE) signals. It was seen that all the output remains low to show that the unit did to respond to the pushing of the button when there is no input signal from the leader’s terminal. The first unit to be tested was the power supply unit. The mains input was varied from 200V to 240V and a digital voltmeter was connected across the output. The voltmeter read 9V. This implies that within this range of input values, the output of the power supply will remain constant. The other tests carried out include accreditation without voting, the outputs that are high include the NULLIFIED and the ACCREDITED outputs. 1.6.2 PALIAMENTARIAN”S Accredited and voted ‘FOR’, only FOR output terminal is high, Accredited and voted AGAINST, only the AGAINST terminal was high. LEADER TERMINAL (THE OSCILATOR) The oscillator unit was powered and the ascended oscillators unit was powered and the output (pin 3) was connected to an oscilloscope to determine the waveform as well as the frequency. Since the frequency is so small the oscilloscope only display the waveform in the form of pulse and the output it can be sketch to be of the form of fig 4.3. The output of the oscillator was then connected to the clock input of the decade counter. The output where tested with a logic tester to see that the counter is actually producing a decoded output corresponding to the number of clock pulse received. It was found that the output was as expected. The next unit to be tested under this module was the three monostable multivibrators. They were both manually clocked and auto clocked and the response is as follow. The ACCREDIT monostable was triggered and it stays on for 32 seconds. The VOTE monostable was triggered and it remains on for 31 seconds and the collating period was16 seconds which is the time it takes for complete collation process. However from the design the ACCREDIT signal suppose to stay on for seconds 30, the VOTE for 30 Double voting, that is” FOR and AGAINST;” the output that is high is only the NULLIFIED terminal. From the above results, it can be concluded that this module worked satisfactorily as designed. 4.4.4 OPERATING THE VOTING SYSTEM. Before switching on the unit, ensure that the terminals are positioned at the desks of the parliamentarians. The plug should be connected to mains of 220V input. At switch on, the leaders terminal should be observed that there is no indicator on. If there is, the system should be put off and put on again The leader should then select the mode he wishes to use i.e. either manual or automatic. In the automatic mode, the system alerts for accreditation and voting and subsequently collate by itself while in the manual mode, the leader triggers the button for accreditation, voting and collation. The unit processes the voting result and displays the results while flashing the decision reached. If the motion is passed, the victory tune sounds. To ensure no failure of the system to operate as described above, qualified technical personnel should be consulted for technical assistance 5 1.7 .COST IMPLICATION The prototype cost N21, 510 as at November 2005 1.8 CONCLUSION The parliamentary vote processing unit was designed, constructed and tested. It was found to be efficient, reliable and durable. The unit can be operated by anyone since it does not require high technical knowledge. The system can be modified for general election purposes. Its local content input is high. 1.9 REFERENCES 1. IGIMOH. J. A. “Lecture notes on Logic Design and Switching Theory” 1998 Unpublished Pgs 120-126 7. DEMSEY J. A. “Experimentation with Digital Electronics” , Anderson-Wesley, 1st Edition, 1977. Pgs 70-77 8. DONALD D. L. “Basic Electric Circuit”, McGraw-Hill 2nd Edition 1975, pgs 290-299 9. CUBSON J. R. “Electronic Logic Circuit”, Edward Arnold press, 3rd Edition 1982 pgs 10-51 10. TOCCI R. J. “Digital Systems: Principles and applications Practice”, Hall Jot Edition 1980, pgs 227-254 11. LAWAL A. J. “GOVERNMENT MADE EASY”, Stenon press, 2nd Edition 1992 pgs 47 53 2. HOROWITZ PAUL “The Art of Electronics” Cambridge University Press, 2nd Edition Pgs 75-83, 341-350, 468-489. 3. www.fairchildsemi.com and www.onsemi.com 4. EZIASHI J. E “Basic Electronic Circuits and Devices”, Lecture notes 1998 Unpublished Pgs 37-45, 62-75, 98-126,168172 5. BARTEC T. C. “Computer Architecture and Logic design” McGraw-Hill, International Edition Pgs 136-215 6. CHARLES A L and KENNETH A W “Electronic Engineering” John Willy, London, 3rd Edition 1973, pgs 731-735 Note: All correspondence to: H.E. Orovwode [email protected] 6 MODE CONTROL Parliamentarians Leader's Terminal Results Display Board Manual Automatic Victory Tune Module Clock Pulse Oscillator Power Suppl y Unit Sequencer Main Processing Unit MANUAL TRIGGER Parliamentarian Terminal 3 Parliamentarian Terminal 6 Accredit Enable GATE Vote Enable Collate In Parliamentarian Terminal 5 GATE Out Parliamentarian Terminal 2 GATE Out Parliamentarian Terminal 4 Out Parliamentarian Terminal 1 Fig 3. Parliamentarians Leader's Terminal Fig .1 Block Diagram of the Parliamentary Vote Processing Unit ACCREDIT ENABLE ACCREDIT DC OUTPUT REGULATOR FILTER RECTIFIER MIANS INPUT STEP DOWN TRANSFOMER ACCREDIT OUTPUT ACCREDITATION MEMORY VOTE ENABLE FOR MEMORY VOTE FOR OUTPUT VOTING VOTE ENABLE Fig .2 Power Supply Unit Block Diagram AGAINST MEMORY NULLIFICATION MEMORY AGAINST OUTPUT NULLIFIED OUTPUT FIG 4. PARLIAMENTARIAN'S TERMINAL BLOCK DIAGRAM DATA INPUT MULTIPLEXER COUNTER SEVEN SEGMENT DISPLAY MOTION TIED INDICATOR DECISION BLOCK PRESET RESISTOR CHANGER TEMPO OSC TONE GENERATOR POWER AMP OUTPUT SPEAKER MOTION FAILED INDICATOR ADDRESS GENERATOR MOTION PASSED INDICATOR OVERFLOW DETECTOR VICTORY TUNE GENERATOR FIG 6. VICTORY TUNE MODULE CLOCK PULSE GENERATOR FIG 5. BLOCK DIAGRAM OF THE MAIN PROCESSING UNIT 7 S1 L 7809 9VDC IN4001 D1-D4 R1 N 1.5K C2 16V/0.47uF C1 T1-220/12V D5 25V/2200uF FIG 7 Power Supply Unit 10 8,9 Vcc IC1c IC1- 4093 4 R1 1 ICDT 2 3 R2 6,2 MANUAL 5 10 4 15 4017 R3 1 1 4 7 555 C1 6 14 8,13 5 R4 C2 D2-5 S2 2 R9 7 6 6 3 5 555 Q2 R8 1 C5 C7 D6 C4 R16 3 C6 Q4 ICT/4 3 555 1 5 R19 R20 2 Q3 5 R13 R5 4 ICT/3 555 R15 8 R18 ICT/2 2 8 4 7 Q1 R14 R10 8 R12 R7 4 R11 R6 S3 D8,9 D7 R17 S1 1,6,7 AUTO 16 14 ICT/1 D1 S4 C3 IC1a,b 3,5,6 8 7 C8 SWITCHES S1-ACCREDIT TRIGGER S2-VOTE TRIGGER S3-COLLATE TRIGGER S4- AUTO MANUAL ACCREDIT ENABLE COLLATE ENABLE VOTE ENABLE END COLLATE FIG.8 PARLIAMENTARIANS LEADER TERMINAL CIRCUIT DIAGRAM a Vcc AA VOTE TIMER O/ P ACCREDIT SW IC1 13 a 7 14 14 14 12 IC1b 13 10 9 IC4 D1 5 8 IC2a 8 IC1c 4 IC2b 10 12 9 IC5A 6 R1 ACC TIMER O/P 13 13 8 11 8 11 FOR O/P 7 10 R3 11,9, 10 7 FOR SW 14 1 IC3a 2 R5 3 7 14 AGAINS T SW D2 1 IC1d 3 1 6 5 2 IC5B 1 IC2c 4 6 R6 IC2d 4 3 6 2 C1 9 8 4 IC3c IC1=IC2 4093 INPUTS NAND GATE IC3 - 4070 2 INPUT EX OR GATE IC4=IC5=DUA L D FLIP FLOP AGAINST O/ P 5 IC3b 3,5 10 NULLIFIED,ACCREDITATION ACKNOWLEDGED O/P R4 R7 D3 ACCREDICTED O/P FIG 3.7 PARLIAMENTARIAN TERMINAL CIRCUIT DIAGRAM 8 9 Vcc R5 R1 4 8 SPK1 IC3 555 R4 Q1 R3 3 R2 3 6 C1 8 4 7 IC1 555 Q2 6 2 2 1 5 5 1 C3 C2 C4 8,13 14 IC2 4017 16 4 1 3 6 7 8 9 2 D1-8 Rv1-8 Fig 11. Victory Tune Module Vcc Vcc1 6,13 16 ACCREDIT Multiplexer P1 P2 P3 P4 P5 1 3 5 1 14 SS1 15 12 1 S8S5 D SS1 3 A1 2 15 a b c d e f g 10 12 13 9 11 6 4026 1 CT/SD1 7 13,2, 4,8 R16 8,2 C1 C2 9 C3 ENB 10 Vcc 16,13 11 SS2 Vcc NULLIFIED 16 Multiplexer 5 14 15 12 1 P1 P2 P3 P4 P5 S1 4026 3 D 5 1 4 A2 6 CT/SD2 S85 15 C1 C2 C3 ENB 16 Vcc FOR THE MOTION 3 8 5 S11 D 10 A3 15 9 CT1 S8 5 9 C2 C3 ENB 11 10 R15 2 11 1 6 7 12 11 A4 15 CT2 7 9 C2 C3 10 N(AC) 2 6 14 2 11 1 6 7 4511 9 10 a b 11 12 c d e 13 14 15 SD2 1,2,4,5 ,8,12,1 3 Vcc ENB SS4 C1 C3 Vcc 1 4585 14 10 8 7 2 RL3 3 4 D2-4 D7 R10 Q4 Vcc C6 VR1 Vcc R3 MOTION D6 RL2 R4 16,2 B2 5 4 4520 3 CT3 Q3 14 2 10 13 8 B3 7 11 9 B4 Vcc 12 C2 R2 8-15 TIED C7 Vcc 9 5 6 Vcc 12 8,5 C5 3 Q5 R11 15 C4 FAILED MC1 7,10 B1 RL4 C8 13 1 5,6 1 2 R12 D8 9 2 PASSED Q6 R13 Vcc 16,4, 6 11 R1 C2 RL5 f g 8,5 11 3,4 D9 C9 13 S85 R14 Vcc Vcc 16,3, 4 4510 14 d e f g 5,8 Vcc ,16,1 0 D 9 14 SS3 a b c 9 4511 10 11 12 13 SD1 14 15 Vcc 3 S11 C1 6 1,3,4,5 ,8,12,1 3 Vcc 16 Multiplexer 5 14 15 12 1 2 9 13,2, 4,8 C1 AGAINST THE MOTION e f g Vcc 16,3, 4 4510 Multiplexer 5 14 15 12 1 13,4, 2,8 11 6 7 Vcc 16,10 10 11 P1 P2 P3 P4 P5 a b c d 8,2 13,2, 4,8 P1 P2 P3 P4 P5 10 12 13 9 R5 Q2 D1 C5 D5 RL1 4,8 R7 7 555 3 R8 C3 2 1 Q1 L(AC) R9 6,2 ICT1 1 5 C4 C1 (Y) TO RESET COLLATE (X) 3 FROM COLLATE TUNE MODULE Fig 10. Main Processing Unit Diagram 10