* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

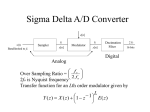

Download Design of a 14-bit fully differential discrete time delta

Audio crossover wikipedia , lookup

Superheterodyne receiver wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Television standards conversion wikipedia , lookup

Spectrum analyzer wikipedia , lookup

Telecommunication wikipedia , lookup

Oscilloscope wikipedia , lookup

Analog television wikipedia , lookup

Oscilloscope types wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Power electronics wikipedia , lookup

Schmitt trigger wikipedia , lookup

Quantization (signal processing) wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Tektronix analog oscilloscopes wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Regenerative circuit wikipedia , lookup

Two-port network wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current mirror wikipedia , lookup

Operational amplifier wikipedia , lookup

Oscilloscope history wikipedia , lookup

Phase-locked loop wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Radio transmitter design wikipedia , lookup

Rectiverter wikipedia , lookup

Integrating ADC wikipedia , lookup

Index of electronics articles wikipedia , lookup

Opto-isolator wikipedia , lookup