* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Stray insensitive switched capacitor composite operational amplifiers

Oscilloscope wikipedia , lookup

Crystal radio wikipedia , lookup

Spark-gap transmitter wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Surge protector wikipedia , lookup

Distributed element filter wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Power electronics wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Phase-locked loop wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Index of electronics articles wikipedia , lookup

Radio transmitter design wikipedia , lookup

Zobel network wikipedia , lookup

Regenerative circuit wikipedia , lookup

Oscilloscope history wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Current mirror wikipedia , lookup

Two-port network wikipedia , lookup

RLC circuit wikipedia , lookup

Operational amplifier wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Integrating ADC wikipedia , lookup

Opto-isolator wikipedia , lookup

Power MOSFET wikipedia , lookup

Calhoun: The NPS Institutional Archive

DSpace Repository

Theses and Dissertations

Thesis and Dissertation Collection

1993-03

Stray insensitive switched capacitor

composite operational amplifiers

Bingham, Eldon Wade

Monterey, California: Naval Postgraduate School

http://hdl.handle.net/10945/24229

Downloaded from NPS Archive: Calhoun

UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE

REPORT DOCUMENTATION PAGE

REPORT SECURITY CLASSIFICATION

UNCLASSIFIED

2a SECURITY CLASSIFICATION AUTHORITY

Approved

PERFORMING ORGANIZATION REPORT NUMBER(S)

4

NAME OF PERFORMING ORGANIZATION

6a

6b OFFICE

(If

ADDRESS

(City. State,

ADDRESS

(City. State,

NAME OF MONITORING ORGANIZATION

ADDRESS

Monterey,

8b OFFICE

SYMBOL

9.

TITLE (Include Security

and ZIP Code)

(City. Sfafe.

CA 93943-5000

PROCUREMENT INSTRUMENT

IDENTIFICATION

NUMBER

applicable)

and ZIP Code)

10

SOURCE OF FUNDING NUMBERS

Program Element No

1 1

unlimited

7a

7b

(If

is

Naval Postgraduate School

and ZIP Code)

NAME OF FUNDING/SPONSORING

ORGANIZATION

distribution

MONITORING ORGANIZATION REPORT NUMBER(S)

EC

8a

release

5

CA 93943-5000

Monterey,

8c

SYMBOL

for public

REPORT

applicable)

Naval Postgraduate School

6c

DISTRIBUTION/AVAILABILITY OF

3

DECLASSIFICATION/DOWNGRADING SCHEDULE

2b

RESTRICTIVE MARKINGS

1b.

1a

Protect

Task No

No

Work unit Accession

Number

Classification)

STRAY INSENSITIVE SWITCHED CAPACITOR COMPOSITE OPERATIONAL AMPLIFIERS

PERSONAL AUTHOR(S)

Eldon Wade Bingham

13a. TYPE OF REPORT

12.

13b TIME

COVERED

14

From

Master's Thesis

DATE OF REPORT

(year,

month, day)

15

PAGE COUNT

March 1993

To

178

SUPPLEMENTARY NOTATION

16.

The views expressed

S Government

in this

thesis are those of the author

and do not

reflect the official policy or position of the

Department

of

Defense

or

the U

17.

COSATI CODES

18.

GROUP

FIELD

SUBJECT TERMS

(Continue on reverse

if

necessary and

identify

by block number)

SUBGROUP

Composite Operational

Amplifiers, Switched Capacitor Networks, Toggle Switched

Capacitor Network, Modified Open-Circuit Floating Resistor Network

19.

ABSTRACT

In this

(Continue on reverse

if

necessary and

identify

by block number)

research, analog active circuits are designed combining the properties of switched capacitors and composite operational amplifiers

finite dc gain, smaller bandwidth, lower slew rate, finite input impedance

performance The switched capacitor is implemented using both the toggle switch capacitor and the modifed opencircuit floating resistor techniques

The composite operational amplifier is implemented using the C20A-1 and C20A-2 designs from the

CNOA-i possibilities These four designs are evaluated in a finite-gam circuit and their results are compared with the results obtained from the

This combined design improves upon the single operational amplifier's

and less than

continuous

ideal output

circuits of the

same

design.

20 DISTRIBUTION/AVAILABILITY

UNCLASSIFIED/UNLIMITED

22a

OF ABSTRACT

SAME AS REPORT

NAME OF RESPONSIBLE INDIVIDUAL

Sherif Michael

DD FORM

1473,

21.

O

OTIC

USERS

ABSTRACT SECURITY CLASSIFICATION

Unclassified

22b

TELEPHONE

(408) 656-2252

JUN 86

Previous editions are obsolete

S/N 0102-LF-014-6603

(Include Area

Code)

22c OFFICE

EC/Mi

SYMBOL

SECURITY CLASSIFICATION OF THIS PAGE

Unclassified

1260213

Approved

for public release: distribution

is

unlimited.

Stray Insensitive

Switched Capacitor

Composite Operational Amplifiers

by

Eldon

W

Bingham

Captain. United States Marine Corps

B.S.. United States

Submitted

Naval Academy

in partial fulfillment

of the requirements for the degree of

MASTER OF SCIENCE

IN

ELECTRICAL ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL

March 1993

ABSTRACT

In

this

research,

analog active circuits are designed combining the properties of switched

capacitors and composite operational amplifiers

This combined design improves upon the single

operational amplifier's finite dc gain, smaller bandwidth, lower slew

less

than ideal output impedance.

The switched capacitor

switched capacitor and

the

operational amplifier

implemented using

possibilites.

is

modified open-circuit floating

These four designs

the

is

rate, finite

implemented using both

resistor

techniques.

C20A-1 and C20A-2

are evaluated in a finite-gain circuit

and

with the results obtained from the continuous circuits of the same design.

in

input impedance, and

the toggle

The composite

designs from the

their results are

CNOA-/

compared

1,1

TABLE OF CONTENTS

I

II

INTRODUCTION

....

1

A

OVERVIEW

1

B

EXISTING PROBLEMS AND SOLUTIONS

2

C

THESIS ORGANIZATION

2

OPERATIONAL AMPLIFIERS

.

THE BEGINNING

A.

IN

B

WHY THE OPERATIONAL

C

LIMITATIONS OF THE OPERATIONAL AMPLIFIER

1

D

Finite

DC

3

3

AMPLIFIER

Gain

3

4

4

2

Limited Bandwidth

4

3

Slew Rate

5

4.

Finite Input

5

Nonzero Output Impedance

6

Finite Linear

7

Offset Voltage

8.

Common-Mode

Impedance

5

5

Range

6

Rejection Ratio

COMPOSITE OPERATIONAL AMPLIFIERS

IV

6

6

III

COMPOSITE OPERATIONAL AMPLIFIERS

7

A

THE NEED FOR THE COMPOSITE OPERATIONAL AMPLIFIER

B.

THE

THEORY BEHIND THE COMPOSITE OPERATIONAL

AMPLIFIER

IV

7

8

C.

C20A-1

10

D.

C20A-2

12

E.

C20A-3

14

F

C20A-4

16

G

ESTABLISHING ACCEPTABLE VALUES FOR a AND K

H

INCREASED BANDWIDTH WITH THE C20As

I

SENSITIVITIES

OF

THE

COMPOSITE

.

18

.

18

OPERATIONAL

AMPLIFIER

20

J.

INPUT OUTPUT OFFSET VOLTAGES

21

K.

SLEW RATES

22

L.

SUMMARY

23

SWITCHED CAPACITOR NETWORKS

24

A.

THE RC TIME CONSTANT

24

B

TWO PHASE NONOVERLAPPING CLOCK

29

C.

NONIDEAL PROPERTIES OF SWITCHED CAPACITORS

D

SWITCHED

CAPACITOR VERSUS

IMPLEMENTATION

.

.

31

DIGITAL

31

V

1.

Limited Accuracy

32

2.

Dynamic Range

32

3.

Flexibility

4

Nonstandard Microprocessor Technology

and Programmability

32

...

33

STRAY INSENSITIVE SWITCHED CAPACITOR NETWORKS

A.

OVERVIEW

B.

STRAY CAPACITANCE

C

NULLIFYING

D

...

34

34

IN

STRAY

THE MOS CAPACITOR

CAPACITANCE

IN

A

34

LOSSLESS

INTEGRATOR

37

A STRAY INSENSITIVE SWITCHED CAPACITOR NETWORK

43

1.

Switched Capacitor Network Design and Layout Precautions

43

2.

A

44

3.

A

Stray Insensitive

Stray

TSC

Insensitive

Implementation of the Lossy Integrator

mOFR

Implementation

of

the

Lossy

55

Integrator

E

SUMMARY

STRAY INSENSITIVE

VI

66

SWITCHED CAPACITOR COMPOSITE

AMPLIFIERS

67

A

DESIGN OF THE STRAY INSENSITIVE C20A-1 AND C20A-2

67

B

TOGGLE SWITCHED CAPACITOR C20A-1

67

1.

67

C20A-1

VI

C

2.

TSC C20A-1

3

TSC C20A-1

with Stray Capacitances

4.

TSC C20A-1

with

5

TSC C20A-1

with Reduced Stray Capacitances

6.

TSC C20A-1

with

7.

TSC C20A-1

with

8

TSC C20A-1

with Even Phase Active

9.

TSC C20A-1

10

Stray Insensitive

with

Combined

Stray Capacitances

Odd Phase

O

O

71

73

75

Active

77

Active and Effective Stray Capacitances

c

Active and Effective Stray Capacitances

e

79

81

TSC C20A-1

83

85

TOGGLE SWITCH CAPACITOR C20A-2

87

C20A-2

87

2.

TSC C20A-2

89

3

TSC C20A-2

with Stray Capacitances

4.

TSC C20A-2

with

5.

TSC C20A-2

with Reduced Stray Capacitances

6

TSC C20A-2

with

7.

TSC C20A-2

8.

TSC C20A-2

with Even Phase Active

9.

TSC C20A-2

with

10.

Stray Insensitive

1.

D

69

Combined

93

Stray Capacitances

Odd Phase

95

97

Active

Active and Effective Stray Capacitances

with

O

e

TSC C20A-2

C20A-1

99

101

Active and Effective Stray Capacitances

MODIFIED OPEN-CIRCUIT FLOATING RESISTOR C20A-1

1.

91

103

105

.

107

107

vn

E

2.

M0FRC20A-1

3

MOFR

C20A-1

with Stray Capacitances

4

MOFR

C20A-1

with

5

MOFR

C20A-1

with Reduced Stray Capacitances

6

MOFR

C20A-1

with

7

MOFR

C20A-1

with O, Active and Effective Stray Capacitances

1

8

MOFR

C20A-1

with Even Phase Active

121

9

MOFR

C20A-1

with

10

Stray Insensitive

Combined

Stray Capacitances

Odd Phase

O

e

MOFR

Active

Ill

113

115

117

19

Active and Effective Stray Capacitances

123

C20A-1

125

MODIFIED OPEN-CIRCUIT FLOATING RESISTOR C20A-2

127

C20A-2

127

2

MOFR C20A-2

129

3

MOFR C20A-2

with Stray Capacitances

4

MOFR

with

5

MOFR C20A-2

with Reduced Stray Capacitances

6

MOFR C20A-2

with

Odd Phase

7.

MOFR C20A-2

with

O

8

MOFR C20A-2

with Even Phase Active

141

9

MOFR C20A-2

with O, Active and Effective Stray Capacitances

143

10

Stray Insensitive

MOFR C20A-2

145

1

VII

109

C20A-2

Combined

Stray Capacitances

Active

Active and Effective Stray Capacitances

EXPERIMENTAL IMPLEMENTATION AND RESULTS

vui

1.31

133

135

137

139

147

A

DESIGN IMPLEMENTATION

147

B

THEORETICAL VALUES

153

1

C

Finite-Gain Resistor Values

153

.

2

Quality Factor

154

3

Capacitor Ratio

154

4.

Switched Capacitor Equivalent Resistance

155

5.

Power Supply Voltage

155

6

Negative Feedback Capacitors

155

7

Input Signal Frequency

156

8

Clock Frequency

158

.'

EXPERIMENTAL RESULTS

CONCLUSIONS

VIII.

.

....

159

AND RECOMMENDATIONS FOR FUTURE

RESEARCH

163

A

CONCLUSIONS

163

B

RECOMMENDATIONS FOR FUTURE RESEARCH

163

LIST OF

REFERENCES

164

BIBLIOGRAPHY

166

INITIAL DISTRIBUTION LIST

167

IX

INTRODUCTION

I.

OVERVIEW

A.

The operational amplifier (OA)

It is

used

in

most

the industry, the

compromise,

all

OA

speed

The composite

It

will

is

the

Though

electronic designs

is

is

not without

most important analog integrated

its

the

OA

traded for accuracy, accuracy

operational amplifier

improve the bandwidth,

is

(CNOA-/)

sensitivity, accuracy,

The switched capacitor network

has a widespread use throughout

An OA, by

limitations

definition,

is

a lesson in

traded for bandwidth, etc

is

a circuit with great flexibility

and speed over the single

will decrease the size

component values during manufacturing. This

circuit today

OA

and improve the accuracy of

size reduction

and increased accuracy

allow more designs to be implemented on a single integrated circuit (IC) than

is

will

possible

otherwise.

Combining

the composite operational amplifier with parasitic free switched capacitor

technology will produce an

OA

that has a considerable

bandwidth extension over the single

and

D/A

conversion,

digital

OA

This combination has direct applications

communications,

processing, modulator-demodulator circuitry,

to

name

a

performance improvement and

filtering,

HDTV,

signal

processing,

in A-

D

speech

and neural network implementation

few

This thesis proposes

to

combine

the

composite operational amplifier and the

switched capacitor network into a single stray insensitive design

This

new

design should

produce an

OA

with an increased bandwidth and a decrease

The removal of continuous

and active elements

in sensitivity to

both passive

resistors in the circuit using

switched

capacitors will decrease the area needed to implement this design on an IC

B.

EXISTING PROBLEMS

AND SOLUTIONS

The accuracy of the switched capacitor network can be degraded by

unpredictable error caused by parasitic capacitances found

Two

an IC

in

the inherent and

parasitic free,

switched capacitor topologies, the Toggle Switched Capacitor (TSC) and the modified

Open-circuit

Floating

(mOFR), provide

Resistor

a

means

to

eliminate

these

stray

capacitances

C.

THESIS ORGANIZATION

The goal of

this

thesis

is

composite operational amplifier

second chapter

to

implement a

will

(parasitic free) switch capacitor

insensitive

The operational amplifier

Composite operational amplifiers

Switched capacitor networks

stray

be discussed

networks

will

will

be discussed

four designs used

designs and

it

in this thesis.

chapter

The seventh chapter contains

in the

will

draw

in

the

chapter

Stray insensitive

chapter

The

development of

sixth

the

the schematics for the four

includes the experimental results obtained from those

The eighth chapter

research.

in the third

in the fifth

chapter will pictonally display the ten step process utilized

capacitor

be discussed

will

be discussed

in the fourth

switch

same four designs

the necessary conclusions and will develop ideas for future

OPERATIONAL AMPLIFIERS

II.

A.

THE BEGINNING

IN

During the 1950's the

made from vacuum

tubes,

furnace, and required large

first

operational amplifiers (OAs) began to appear, they were

were larger than a breadbox, emanated more heat than

power

supplies.

More

a small

importantly, however, they were both

unreliable and expensive

The

early 1960's brought about the transistor

and solid

state circuits

and for the

first

time reliability was added to the operational amplifier equation

The

advances that resulted from

circuit.

By 1965

Fairchild

One of

1960's also brought about the space race.

a

race to space

this

was

the

the

many

technological

development of the integrated

commercially available integrated operational amplifier appeared

-

the

uA709

Today OAs can be purchased

in

no

less

than

150 different types for specific

applications as needed.

B.

WHY THE OPERATIONAL

The widespread use of

The

OA

behaves so much

the

like

OA

its

that

one already

can be traced to the ease of understanding

ideal characteristics that

thus easy to implement in a design.

good chance

AMPLIFIER

With so many

exists that will

it

is

different

its

parts

easy to comprehend and

OAs

available there

meet your design requirements

is

a

LIMITATIONS OF THE OPERATIONAL AMPLIFIER

C.

The

OA

impedance, zero output impedance and

are

too

numerous

maximize

the

weaknesses

The

a voltage controlled voltage source

is

OAs

infinite voltage gain

itself is quite a robust

finite

dc gain, limited bandwidth, slow slew

ideal

output resistance

The differences between an

OA

has infinite input

Designs using the op amp

Electronic designers have gone to great lengths to

strengths in their designs as well

OA

The

mention

to

ideal

and

ideal

as

work around

their

inherent

building block that has limitations such as

rate, finite

a practical

input impedance, and less than

OA

are

many,

in the

next eight

subsections a few of the differences that do exist will be touched upon as they have far

reaching effects later on

DC

Gain

OAs

have

Finite

1.

Ideal

in this thesis

gain, typically in the range

An

ideal

a 6

This 20

to

to

OA

dB

1

have a more modest

million

has unlimited gain across the entire bandwidth

As frequency

have a limited useable bandwidth

stray capacitances

have

from 100

OAs

Limited Bandwidth

2.

OAs

however, practical

infinite gain,

and

finite carrier

mobility

(BW)

Practical

increases the gain decreases due

Additionally, internally compensated

OAs

dB

per octave gain rolloff due to the pole created by the compensating capacitor

dB

per decade rolloff will reduce an OA's gain from typically 100

typically

somewhere between

1

and 10 MHz.

dB

at

10

Hz

Slew Rate

3.

Slew

rate

If a large input step

limited.

the transistors in the

completely cut

voltage

OA

the

at the

few

volts per

which

practical

OA

is

ideal

OAs

are not slew rate

OA, some of

OA

their saturation

regions, or possibly

output can no longer follow the applied input

was applied

output

is

The maximum

called the slew rate.

rate

of change that an

Typically slew rate

is in

micro second range.

input

Impedance

impedance of an

typically in the

ideal

OA

is

infinite

The input impedance of

a

low Mfi range.

Nonzero Output Impedance

5.

OAs

with a buffering output stage have a nonzero output resistance typically

few kQ, which prevents the

to a

also limits the speed with

which,

its

it

OAs,

applied to the input of a practical

is

might be driven out of

rate at

Finite Input

The

voltage

Therefore the

off.

same

OA

can effectively transfer to

4.

up

a limiting factor in practical

is

in effect,

6.

which an

OA

OA

from operating as an

ideal voltage source

can charge a capacitor connected

to its

This

output

determines the highest useable signal frequency

Finite Linear

Range

The output of

a practical

OA

input voltages multiplied by the gain of the

a limited range of output voltage

is

determined by the difference between the

OA, however

The maximum value

this relationship

only holds for

for the output voltage

is

usually

maximum

limited to the

dc supply voltage applied, or even a few volts less

an applied dc voltage of ± 15 volts the output voltage might be limited to

Thus, with

±

12 volts.

Offset Voltage

7.

An

of zero volts

ideal

OA

whose

In a practical

voltage differential

inputs are tied together will produce an output voltage

OA

at the inputs

with the inputs tied together there will

which

voltage needed to be applied to the

be magnified by the gain

will

OA

output voltage

to null the

at the

is

still

be some

output

The

called the offset

voltage

Common- Mode

8.

Rejection Ratio

The common-mode

how much

to

the

OA

suppress noise

common-mode

at its inputs

if

the

CMRR

of a practical

signals at the inputs

is

high

It

not

is

OA

is

a

measure of

This allows the

uncommon

to

OA

have a

60-100 dB

COMPOSITE OPERATIONAL AMPLIFIERS

The gain bandwidth product,

frequency,

slew

(CMRR)

can suppress

rejection in the range of

D.

rejection ratio

is

the product of the finite gain of the

generally considered to be constant in a given

rate limitations,

OAs

that will

Composite

of the single

OAs

OA

and the 3dB

Speed, determined by

and accuracy, determined by the input offset voltage, are usually not

a variable that can be adjusted in single

multiple

OA

OA

OA

designs

However, there

exists designs of

allow for greater user control over these same characteristics

effectively extend the range of single

limitations

Chapter

III

OAs

will discuss this in

and lessen the impact

some

detail

COMPOSITE OPERATIONAL AMPLIFIERS

in.

THE NEED FOR THE COMPOSITE OPERATIONAL AMPLIFIER

A.

Composite Operational Amplifiers (CNOAs) were developed by

W

B.

Mikhael

References

-

1

1981, their research and

in

7.

Their

initial

its

S.

N. Michael and

applications have been published

focus and subsequent development of

CNOAs

in

provided

a systematic technique for extending the operational frequency range (bandwidth) of linear

active networks

filter

Active compensation was examined and applied

to the

design of active

networks.

The systematic technique

for

extending

bandwidth (BW)

the

using

CNOAs

originated from using the nullator-norator pairing to create 136 possible circuit designs

that

were then subjected

to the

following performance

criteria:

The noninverting and inverting open-loop gains of each of the 136 C20As should

show no change in sign in the denominator polynomial coefficients This satisfies the

1.

necessary, but not sufficient,

denominator

coefficients

conditions for stability.

of the noninverting and

should be realized through differences

GBWPs

matched

and

results

in

Also, none of the numerator or

inverting polynomial coefficients

This eliminates the need for single op amps with

low

sensitivity

of the

C20A

with respect

to its

components.

2

The

as possible, the three-terminal

3.

To minimize phase

shifts

To

justify

frequency

function.

the

increased

operation

with

should resemble, as closely

performance of the single OA.

no right-half s-plane (RHS) zeros due

pole were allowed in the closed-loop gains of the

4

C20A

external three-terminal performance of the

number of OAs,

minimum

to the single

OA

C20As.

the

C20A

had

to

have an extended

gain and phase deviation from the ideal transfer

B.

THE THEORY BEHIND THE COMPOSITE OPERATIONAL AMPLIFIER

An

operational amplifier

is

ideal case the input

impedance, Z in would approach

would approach

and the open loop gain. A, would approach

0.

A

A

norator

is

nullator

is

a

infinity

model using nullator and norator singular elements

method of

1,4]

These models can be seen

CNOAs

analysis

of the original 136 possible designs met

a current

all

numbered C20A-1 through C20A-4

(where

N

=

2)

in

Figure

3

Using the

1

Only four

were developed

four of the above performance criteria, they

The

resulting composite devices

had three

external terminals which resembled the input and output terminals of a single op

the

single pole

C20As

model open-loop gain of

A

A oi

the single

OAs

used

in the

amp

modeling of

is

A

where

,

a one port which will sustain an arbitrary voltage and pass an arbitrary

nullator-norator

The

Z out

This can be

one port which neither sustains a voltage nor passes

independent current [Refs

are

In the

output impedance,

infinity, the

,

directly transferred to the idealized

[Refs. 2,4]

(VCVS).

a voltage controlled voltage source

,

co

Li

,

bandwidth product

and

CO-

L_

=

,

are the dc open-loop gain, the

cOj

(GBWP)

output relationships for the

CO,-

-2-J±

=

of the

ith

single

OA,

i

or 2

3dB bandwidth, and

respectfully

C20A-1 through C20A-4

1

The

open-loop

can be described by

(3.1)

the gain

input-

(a)

Nullator

(b)

Norator

lo

00

'in

(c)

Nullor

OA

'out

A

To

Figure 3.1

(a) Nullator,

(b) Norator,

(c)

Nullor

OA (VCVS)

00

C20A-1

C.

C20A-1

For

Equation

3

the open-loop gain input-output relationship can be derived from

2 as

AJl+AMl+a)

AAJl+a)

(3.3)

A

where

a

is

M,

+

(1+a)

the internal resistor ratio as

shown

References

1,

2,

and

3

l

in

Figure

+

(1+a)

3 2.

derive the 3db frequency equation and

Q

equation to be

(3.4)

co.

G)

(l + oc)

2

•d+*)N W

where

the

a

is

GBWP

the internal resistor ratio,

for A,

,

and

co

;

is

the

co

is

p

GBWP

the

for

3db

A

:

(3.5)

l

point, k

is

the closed-loop gain,

co

is

The Routh-Hurwitz criterion produces

.

the necessary and sufficient conditions for stability as

+

1

(1

The C20A-1

in

* a)

k

(3.6)

<

Figure 3.2 clearly shows the similarity of the three terminal

configuration between the composite

OA

and

that

of a single OA.

noninverting and inverting inputs for the composite

OA

10

OA just

Inputs a and b are the

as they

would be on

a single

Figure 3.2

C20A-1

11

C20A-2

D.

C20A-2

For

Equation

the open-loop gain input-output relationship can be derived from

3 2 as

y

where

a

is

VgO^O

y

=

a

A2

References

1,

2,

and

3

+

shown

the internal resistor ratio as

VjM

%

y

_

(1+a)

*

Figure

in

(3.7)

(1+a)

3 3.

derive the 3db frequency equation and

co

Q

equation to be

co

1

(3.8)

:

co.

l+k

\

G),

(1+co

i/(l+*)N

where

the

a

is

GBWP

the internal resistor ratio,

for A,

,

and

co :

is

the

is

co

p

GBWP

the

3db

A

for

(3.9)

w2

point, k

is

the closed-loop gain,

The Routh-Hurwitz

:

to,

is

criterion produces

the necessary and sufficient conditions for stability as

+ k

1

(1

The C20A-2

in

Figure

3 3

configuration between the composite

clearly

OA

(3.10)

<

+ «)

shows

and

that

of a single

noninverting and inverting inputs for the composite

OA

12

the similarity of the three terminal

OA just

OA

as they

Inputs a and b are the

would be on

a single

Figure 3.3

C20A-2

13

C20A-3

E.

C20A-3

For

Equation

3 2

the open-loop gain input-output relationship can be derived from

as

V

v

o3

where a

is

V

v

a

=

the internal resistor ratio as

References

1,

2,

and

3

AjA 2

Agl+AJ

-

(3.11)

V,

(1+oc)

(1+a)

°

shown

Figure

in

3

4

derive the 3db frequency equation and

(x>

<x>

x

00.

Q

equation

2

Yd *)(!+«)

the

is

GBWP

the internal resistor ratio,

for A,

,

and

co

:

is

the

ca

the

is

GBWP

(3.13)

w,

\

a

be

(3.12)

(!+*)(! ^a)o),

where

to

for

3db

A

point, k

is

the closed-loop gain,

The Routh-Hurwitz

:

co

is

criterion produces

the necessary and sufficient conditions for stability as

(1

The C20A-3

in

Figure

3

>

+ a)

4 clearly

configuration between the composite

OA

shows

and

that

the

14

similarity

of the three terminal

OA

Inputs a and b are the

of a single

noninverting and inverting inputs for the composite

OA

(3.14)

\l\+k

OA just

as they

would be on

a single

Figure 3.4

C20A-3

15

C20A-4

F.

C20A-4

For

Equation

the open-loop gain input-output relationship can be derived

3 2 as

A 2 (A^a)

04

where a

is

a

1,

2,

and

3

A2

[A,

shown

* (1+oc)]

(3.15)

*

(1+a)

the internal resistor ratio as

References

(1+a)

Figure

in

3 5

derive the 3db frequency equation and

co

j

co

Q

equation

2

p

(l^)co

(3.17)

1

(l+a)« 2

\|

the

is

GBWP

the internal resistor ratio,

for A,

,

and

co

:

is

the

the

is

co

p

GBWP

be

(l+*)(l+a)

\|

a

to

(3.16)

co.

where

from

for

3db

A

point, k

is

the closed-loop gain, o,

The Routh-Hurwitz

:

is

criterion produces

the necessary and sufficient conditions for stability as

(1

The C20A-4

in

Figure

3 5

>

+ a)

clearly

configuration between the composite

OA

shows

and

that

the

16

similarity

of the three terminal

OA

Inputs a and b are the

of a single

noninverting and inverting inputs for the composite

OA

(3.18)

+ k)

4(1

OA just

as they

would be on

a single

Figure 3.5

C20A-4

17

16), the

criterion

Q

equations (Equations

equations

compensation

(Equations

a

resistor ratio

The closed-loop

13,

3 5, 3 9, 3

3 6,

3

10,

3

and

3

17), as well as the

and

14,

3

and

Q

and

co

p

this

a

Routh-Hurwitz

functions

all

and

of the

many implementations

should allow for a great degree of freedom

for the desired design requirements

resistor ratio, a, can likewise be selected with a similar

Thus

are

18)

gain, k, can be controlled by the designer in

obtaining an acceptable

3 4, 3 8, 3 12,

and the closed-loop gain k

(as in a finite-gain configuration)

and

K

should be noted that the 3db frequency equations (Equations

It

3

a AND

ESTABLISHING ACCEPTABLE VALUES FOR

G.

for each of the four

C20As

it

in

The compensation

amount of freedom

quite easy to select theoretical values for k

is

while ensuring that the required stability

is

maintained

in

each of the four

implementations

INCREASED BANDWIDTH WITH THE C20As

H.

A

single

OA

in

a finite-gain amplifier configuration has a

approximately by a factor of 1/k relative

to its

GBWP When

together in a finite-gain amplifier configuration, the maximally

is

obtained

when each

realize an overall gain

The

GBWP

of

amplifier. A, and

of

k.

The

A

resulting

C20A-1 and C20A-2

:

,

flat,

that decreases

OAs

are cascaded

thus optimum,

has an individual gain of \fk,

BW

shrinks by approximately

can be designed

18

two

BW

to

in

GBWP

order

.66

,<

to

V'X

shrink by only a factor of

1 /

v^

for

Q

p

= 0.707 (maximally

flat) [Ref. 4]

These theoretical

BWs

are

shown more

clearly in Figure 3.6.

dB

{20 Log

(VJVtfk

|

|

}

f

20

40

T) Single

1

00

OA

2)

Two Cascaded

3)

C2QA-1

OA, Two Cascaded

GBWP =

80

single

OAs

Theoretical responses of negative finite-gain amplifiers realized using

Figure 3.6

Single

60

kHz

1

Single

OAs, and C20A-1 for negative gain of 100, and

MHz

19

SENSITIVITIES OF

L

THE COMPOSITE OPERATIONAL AMPLIFIER

In addition to significant

bandwidth improvements, the

C20A

offers a decreased sensitivity to active and passive components.

the first

performance

criteria

equations (Equations 3.4,

3

13,

and

3 17) are

compensation

The

mentioned

3 8, 3 12,

functions of the

resistor ratio in the

and

earlier in this chapter

GBWPs

composite

Q

and the

16)

3

This

configuration also

is

The

a direct result of

3

dB frequency

equations (Equations

of the single

OAs

(A, and

A

3 5,

3 9,

and a, the

;)

OA

C20As

finite gain transfer functions for the

have the general form

+ as

1

(3.19)

+

1

b s +

{

b^ 1

where

b

—±—

=

t

<*

P

(3.20)

Q

and

b2

-L

=

(3.21)

Neither the a or b coefficients are realized through differences,

for single

OAs

respect to

its

with matched

GBWPs

components [Refs

and

results in

3, 4]

20

low

this eliminates the

need

C20A

with

sensitivity

of the

INPUT OUTPUT OFFSET VOLTAGES

J.

Operational amplifiers typically have large gains and will amplify any voltage

differential at

its

of zero volts

An

inputs.

All

OAs

in

OA

ideal

the real

with both inputs grounded would have an output

world have

(V off).

inputs referred to as the input offset voltage

gain of the amplifier

is

a small

DC

voltage differential

This voltage

at the

when amplified by

referred to as output offset voltage [Ref 8 pp

133

-

the

This

138]

input voltage differential can be attributed to a voltage difference applied to the two

inputs of the

OA

(ideal

OAs), or

it

can be attributed to a voltage difference due

having different gains and different internal

transistor pairs in the input differential stage

impedances

[Ref. 8:pp. 500-504], or both (real world).

Input offset voltage places an

artificial

OA

can detect and amplify the input signal

are

found

in

the

few

millivolt range

will be amplified

The possible

lower limit on the

The smaller

accurately detected and amplified.

however

OA

by the

be used and the

OA

select a high

V

otf

for

later

is

voltage that can be

more accurately

This small voltage differential

composite

rate

that not

solution typically

OA

for

OAs shown

A

in

.

:

at

the inputs

gain and could produce a degraded output signal

all

OA

many

but the most

common

are to

with a smaller offset voltage

The

designs will allow a input bias resistor to

comes

at

a cost

-

a slower slew rate

allows for yet another solution, select a small offset voltage

slew

the

Offset voltages are fairly small and normally

solutions to voltage offset problems are

problem with the former solution

DC

the offset voltage, the

use an input bias resistor, or to simply select an

composite

to the

OA

for A,

The

and

This can more easily be shown from the values for

Table

3.1.

21

Notice that

V

otf

is

for

all

practical purposes

a function of

V

otfl

alone and not of

divided by the open loop gain (A

I)

V

off2

.

from

OA

This value

A,.

a

as long as

remains relatively large then

the overall value of

in

Table 3.1

V

olf

V

off

In the case

.

of

either

C20A INPUT OFFSET VOLTAGES

Input Offset Voltages

C20A-1

V

olT

C20A-2

V

off

C20A-3

V

off

C20A-4

V off=

Vofc

/

V

oft

/Al

(V

ofl2

(l+a)/Al).

(V

ort2

(l+a)/Al)

=

V om

-

(

=

V ofn

+

(

=

V om

+

V, tn +

,

a

)

)

SLEW RATES

Slew

[Ref

V

will not play a substantial part

,.,

C20A-/

K.

is

(Al) will always be very

large yielding an extremely small effect on the overall value of

C20A-1,

C20A-4 V otC

For C20A-2, C20A-3, and

8:p.

rate

(SR)

124].

is

the

Slew

maximum

rate

is

possible rate of change of the

offset voltage

Most

OA

output voltage

dependent upon the bias current and the internal

compensation capacitor value [Ref 8:pp 771

most applications, however, a

OA

faster

slew

rate

-

772]

comes

A

faster

at the

designs either incorporate a fast

slew

rate is preferable in

expense of an increase

SR

in

input

design or they incorporate

a small offset voltage design.

The composite

OA

voltage for a composite

offers an alternative

OA

is

It

has already been

shown

that the offset

determined by the A, op amp, thus, choosing an

22

OA

with

an extremely small offset voltage along with

will not hinder the

its

output of the composite op

and dynamic range limitations,

distortion

amp due

A

dependent upon the characteristics of the output op amp,

The output op amp, A

rate,

OA

can

now

wide bandwidth,

can be chosen for

high slew

its

[Refs.

rate,

I,

2, 9,

10].

wide bandwidth, and

OA

The

be designed with a low offset voltage input stage and a high slew

fast settling

output stage for superior performance,

needed.

if

SUMMARY

L.

CNOAs

this

in

value of

chapter,

N

be chosen

OAs

for A,

and

A

:

any

The generation of C20As was shown

made

to

N

>

OA

single

produce a C30A.

will

can be

> 2

to

fill

(A,

or

A

:)

C20A

a

in

This method can by used for any

2 can be

found

in

References

1

-

7

exacting design specifications by choosing the

and careful consideration of the value for

cannot precisely meet any specification then a

CNOAs

low

replacing

Details of proven designs for

appropriate

C20A

C20A

OA

N

for any value of

simply

by

but

The composite

the

made

can be

configuration with a

a

,

:

time thus improving the overall performance of the composite

fast settling

composite

:

composite's output being

to the

CNOA

with

N

a

as well

> 2 can

If

easily

the need.

have an extremely low

offset voltage

of op amps A, and

and high slew

A

:

sensitivity, a high

rate

GBWP,

can be tailored to provide

and can handle the mismatch between the

.

23

GB WPs

IV.

SWITCHED CAPACITOR NETWORKS

THE RC TIME CONSTANT

A.

The

resistors

RC

time constant

is

and capacitors are made

cannot not track one another

resistors

a

little

modern

the limiting factor in

in different steps in

Additionally, the temperature and voltage coefficients of

will

always vary

with temperature and signal level.

solution

is

make- the time constant a factor solely of resistance

to either

or solely of capacitance, but not a combination of both

accurately, at less expense, and they occupy a

than a resistor would.

constant

set

The choice then

is

much

Capacitances can be

made more

smaller area on an integrated circuit

obvious, replace the

RC

time constant with a

c.

Frequency

be

Since

the fabrication process, their errors

and capacitors are not correlated, therefore, the time constants

The obvious

to

active filter design.

is

determined by the

by the constant

on an IC chip

c in

RC

time constant.

We

order to be more accurate and to save valuable real estate

Starting with the

RC

time constant

we have

—

RC

1

gi

Converting

this

are looking for frequency

=

expression to strictly a capacitive one leads to

24

(4.1)

u

We

use

fc

ensure that

to

the expression

for

a)

c

subsequently solving for

we have

in

R

=

cfc

CR

—f

=

(4.2)

c

the correct units for (J,

which

Equation 4.2 into the variable

(x>

1/time.

is

Equation 4

in

(4.3)

C>

Equation 4.3 simply implies that a resistor can be replaced by a circuit that

in

is

and

1

=

fc

expression

1

yields

R

above expression. The

Substituting

circuit or

network

that replaces the resistor

called the switched capacitor (SC)

and

satisfies the

that satisfies this

The switched capacitor

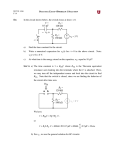

circuit

is

shown

Figure 4.1 below

4>

R

AAV

4>

o-

v:

v,

v,

v,

c

T

cR

(a)

Figure 4.1

(a) Resistor,

(b)

(b)

Switched Capacitor equivalent,

25

(c)

(c) Circuit

Diagram

Figure 4 la

is

generic resistor

a circuit that can be replaced by the circuit in

in

Figure 4.1b, a generic switched capacitor equivalent circuit

Figure 4 lb

we have

CR connected

capacitor

to the left

Taking a closer look

node with voltage V,

,

at

thusC^

stores charge

Ql

CR

Subsequently connecting capacitor

that

was

The switching of

switched capacitor

C R between

The

Q

=

the

{

from V,

Q2

two nodes

it

to

V,

follows that

becomes

V2 )

-

{

is

-

(4.5)

C R (V

=

4 4)

(4.6)

handled by a switch,

S,

hence the name

switch, S, can be flipped periodically with a clock period, T,

now

such that the clock frequency can

be defined as

sufficiently greater than the signal frequency, f,

fc

then the voltage sources V,

The

node with voltage V,

C R V2

=

actually transferred

*Q

<

\

to the right

Q2

The charge

CR V

=

and

definition for current

V

:

»

2/

fc

=

l/T

If

fc

is

kept

such that

(4.7)

can be assumed to be constant over the period

T

is

i

-

**

dt

26

(4.8)

or on the average what

we

have

really

is

but

we had

previously defined

fc =

(4.9)

1/T, so

A(?/c

"

/

it

*Q

_

r

(4.10)

follows from Equation 4 6 that

or by rearranging

we have

(V.

1

-

K)

(4.12;

recalling Equation 4.3 leaves us with

This derivation ends with Equation 4 13 which shows us that Figure 4 la and Figure 4 lb

are indeed approximately equivalent.

Figure

4.

1

c depicts the circuit

nonoverlapping clock signals,

equivalent of the switch capacitor

and

O

between the two voltages without any

same

time.

The two clock

This arrangement

is

best

e

,

to

ensure that the capacitor

Here we have two

is in

in

switched

possibility of both switches being closed at the

signals are generated from a single clock for the

shown

fact

Figure

4.2.

27

same reason

Clock

A

(a>

t

O

o

(b>

t

O.

(c>

Figure 4.2

t

(a)

Qock,

(b)

Odd

Phase

Oock

28

Signal,

(c)

Even Phase

Oock

Signal

The switched capacitor implementation of the continuous

most troublesome problems with the

parameters are

now

set as a function

r.

and that the required

idea as to

real estate

how much

RC

of the

-

time constant namely

ratio

±

pF capacitor

will

will

area was saved

let's

the

assume

kHz

that

CR was lpF

results in an

R

To give

in

:

25%

chip area of approximately

\im

z

.

Thus

the area of the resistor

us

some

Using

size

value of 10

occupy a chip area of approximately 2500 u.m and the 10

6

frequency

}£

on an IC has been reduced drastically

occupy a chip area of approximately 10

B.

that

two

of two capacitors and a clock frequency

-

Equation 4.3 and a nominal frequency of 100

1

resistor has solved the

MQ. The

MQ resistor

the capacitor only requires a

it

replaces

TWO PHASE NONOVERLAPPING CLOCK

The two phase nonoverlapping clock requirement

implemented.

Figure

nonoverlapping clock

4 3

It

is

shows

a

for a switched capacitor

simple circuit that will

this circuit that will

needed clocks. The input clock frequency, f c

,

be used

will

29

easily

produce a two phase

this thesis to

produce the

be maintained sufficiently above the

signal frequency, f, by using a signal frequency of 10

MHz

in

is

kHz and

a clock frequency of

1

CLK°

Figure 4.3

Circuit

Diagram for a

Two

Phase Nonoverlapping

30

Gock

NONIDEAL PROPERTIES OF SWITCHED CAPACITORS

C.

The switched capacitor equivalent

circuit

These switches, when clocked,

switches.

namely clock feed through

will

shown

in

Figures 4 lb and 4.1c contain

produce some undesirable side

Clock feed through

is

effects,

one of four main challenges when

using switched capacitor networks, the other three are:

1

Offset Error and Noise

2.

Nonlinear P-N Junction Capacitance.

3

Incomplete Transfer of Charge.

Offset error was discussed in Chapter

III.

Clock feed through, nonlinear P-N

junction capacitance, and incomplete transfer of charge will be discussed

Chapter

V

SWITCHED CAPACITOR VERSUS DIGITAL IMPLEMENTATION

D.

Switched capacitor networks and

and disadvantages compared

To always

say that one

digital signal processor

in

in

some

is

to

digital signal processors

(DSPs) have advantages

one another depending upon the desired implementation.

better than the other

would be

foolish indeed, however, the

does possess some advantages over the switched capacitor network

arenas.

The switched capacitor network disadvantages include

1.

Limited Accuracy

2.

Dynamic Range

3.

Flexibility

4.

Nonstandard Microprocessor Technology

and Programmability.

31

Limited Accuracy

1.

The

its

ratio

of capacitors that

so crucial to successful

is

SC implementation

biggest weakness Currently, these capacitors can be accurately built to within a

tolerance of their nominal values

This

truly remarkable,

is

an approximate 10-bit floating point accuracy

enough

for applications requiring 16, 32, or

The SC network

combination that limits

even 64-bit accuracy

its

requires the use of

dynamic range

There

is

originating from the switches and the

from supply

lines

exceeds 100 dB

in the

Flexibility

3.

SC

digital

characteristics

4.

and switches

a very large

Add

OAs.

much

It

is

this

amount of noise

in the

configuration and typically ranges

in the

in

very

every

more modest noise

that

70

-

seldom ever

90 dB range

higher dynamic range

and Pro gram inability

Switched capacitor

a

OAs

and the clock and we end up with a dynamic range

Digital signal processors maintain a

to

equates to

This accuracy certainly would not be

SC network

hard

this also

0.1%

Dynamic Range

2.

which

however,

is

signal

circuits can be

processor

can

be

made programmable, however,

made programmable and

changed simply by selecting different coefficients from a

then

the ease at

have

ROM

its

will be

match any time soon.

Nonstandard Microprocessor Technology

Digital signal processors are built with the

same technology

doubling our clock speeds and doubling our transistors per

32

CPU

that has

every three years

been

There

is

a concentrated and continuous effort to increase this technology even

it,

so will

All

bias

DSPs

is

power

more and with

see an increase in performance, accuracy, and flexibility

not lost however, whenever simplicity, speed, limited IC real estate, small dc

are required or

when

the input or output signals are inherently analog in nature

then switched capacitor implementation would be the preferred choice

More

often than not, what will be seen

mixing of analog and

digital in the

Designers are trying

to use the

As long

as

is

the melting of the

same configuration

advantages of each

humans hear with analog

in

is

two technologies

The

happening more and more today

order to improve overall product.

ears then analog implementations will be

required.

33

V.

A.

STRAY INSENSITIVE SWITCHED CAPACITOR NETWORKS

OVERVIEW

Switched capacitor networks require an accurate

ratio

of capacitors,

provides the necessary time constant as well as the capacitance needed

continuous resistor found

in the original

This ratio

to replace the

Currently capacitors can be

circuit

1%

achieve a ratio accuracy of about

a

This accuracy

in

made

to

capacitor manufacturing

provides the same comparative accuracy to the ratio of capacitors,

a

Practical capacitors inherently have internal stray

Practical capacitors are not ideal

(parasitic) capacitances

Additionally, switched capacitor circuits also have an inherent stray capacitance

built into

the

all

them

These

parasitic capacitances are unpredictable

performance of any switched capacitor network

The

and can significantly affect

parasitic capacitances

found

switch capacitor networks cannot currently be eliminated, however, they can be

in

made

ineffective by using an appropriate switched capacitor topology

B.

STRAY CAPACITANCE

Figure

5

1

is

IN

a silicon realization

a similar figure found in Reference

capacitance

the

MOS

CR

.

THE MOS CAPACITOR

1

1

of a

MOS

capacitor that has been redrawn from

In this case the

MOS

capacitor represents the

This figure clearly shows the stray capacitances that are

capacitor

34

to

be found

in

Figure 5.1

Silicon Realization of a

MOS

Capacitor

35

There are three parasitic capacitances shown

Cb

in

Figure

1.

Bottom

2.

Metal Routing Parasitic Capacitance,

3

Voltage Dependent Nonlinear Parasitic Capacitance,

Plate Parasitic Capacitance,

Bottom

plate parasitic

between the bottom plate and the

.

Cm

.

Cb

capacitance,

5.1.

substrate.

the parasitic capacitance that exists

is

,

Cr

Metal routing parasitic capacitance,

Cm

,

is

the accumulated parasitic capacitance

formed by

top plate to the various components.

Voltage dependent nonlinear parasitic capacitance,

all

the metal routing

The

associated with the source-drain diffusions of the switches

Cj, is

which connects the

effects of metal

routing parasitic capacitance and of voltage dependent nonlinear parasitic capacitance are-

normally lumped together into a single parasitic capacitance called top plate parasitic

capacitance.

Bottom

plate parasitic capacitance,

Cb

,

has typical values between

percent of the total design value of the capacitor

capacitance,

total

C (where C = C m +

t

t

Cj

design value of the capacitor

One common method used

capacitance

is

to

source, or to an

but

it

will

),

output.

Top

.

1

and

plate

parasitic

percent of the

5

CR

nullify

connect the bottom plate of

OA

CR

has typical values between

itself,

to

itself,

10 and 20

the

CR

to

effects

ground,

This connection will not help

reduce the accumulated parasitic capacitances

36

to

of bottom

to

plate

parasitic

an independent voltage

produce a more accurate C R

at the

OA

virtual

ground

Parasitic capacitances are also manifested into the

to-source and the gate-to-drain

switching

in the

network. This

MOS

capacitor through the gate-

capacitance from the gates

is

perform

that

also the path for clock feed through

source and

and

O

Though

problem

the clocks used in switched capacitor networks are not a part of the signal

switches that produce the two phase nonoverlapping clocks,

e

,

of the

all

itself,

the

use this gate-to-

gate-to-drain paths to introduce clock feed through into the circuit which

causes signal contamination

C

NULLIFYING STRAY CAPACITANCE

A

simple lossless integrator circuit

SC implementation of

capacitances

shown

the lossless integrator

in this circuit.

A LOSSLESS INTEGRATOR

in

Figure

5.2.

Figure 5.3 shows the

Figure 5.4 shows the possible

parasitic

After simplification and combination of these capacitors the

effective parasitic capacitance,

parasitic capacitance

is

IN

Cp

can be clearly shown

in

Figure

was found by switching the clock through

5 5

its

The

effective

two phases while

applying the following three rules for nullifying stray (parasitic) capacitance:

1.

Capacitors between the inverting input of the

OA

and the switch are

at

virtual

ground and thus always shorted

OA

and ground are inconsequential

2

Capacitances between the output of an

3

Capacitances that are driven by a voltage source are inconsequential

Figure 5.5 shows that not

all

of the parasitic capacitance has been removed

using the above three rules to nullify parasitic capacitance

remains.

Even though

there

exists

still

some

some

After

stray capacitance

still

the effects of most of the stray capacitance has been nullified,

stray capacitance in this lossless integrator circuit.

37

I\

V..O-

Figure 5.2

-A/

'

Lossless Integrator

38

<t>

vh

<J>

O

c,

Figure 5.3

/

Switched Capacitor Implementation of the Lossless Integrator

39

c„=

-C

*.

v„0

c„

c_

c„

—/

c„

1/

Figure 5.4

Switched Capacitor Lossless Integrator with

40

Parasitic Capacitances

out

*.

f

c,

Figure 5.5

SC

Lossless Integrator with Effective Parasitic Capacitance

41

The change

in the transfer

be quite detrimental

It

equation due to this effective parasitic capacitance can

can be easily shown that the transfer equation for the lossless

integrator with parasitic capacitance

is

c

c,

--

Vout

(5.1)

Kn

The

transfer

capacitance

-

1

1

equation for the lossless integrator without the effective parasite

is

C

Vout

-(5.2)

=

y„

The

z-

1

-z~

l

error introduced by the effective parasitic capacitance

therefore

is

C

-£

(5.3)

c2

It

may

ensuring that

still

C

:

be possible

is

to

reduce

this error

kept sufficiently large.

value of C, so keeping

it

switched capacitor circuitry

The

for

C can be

Cp

circuit

Any change

kept small or by

as high as

in the

topology can be altered

Many

is

p

value of

Clearly there must be a better

effects of this lasting parasitic capacitance

will focus

The value

small cannot be done

the integrator circuit characteristics

by ensuring that

in

way

to

20%

of the

C changes

:

implement

order to nullify the

such circuit topologies

exist, this thesis

on two, the toggle switched capacitor (TSC) and the modified open-circuit

floating resistor

(mOFR)

42

A STRAY INSENSITIVE SWITCHED CAPACITOR NETWORK

D.

of the remaining parasitic capacitance, the

In order to eliminate the effect

mOFR

the

Switched Capacitor Ne two tic Design and Layout Precautions

The following seven design and layout precautions

networks were found on pages 562 through 564

OAs

must not be operated

nonlineanties and saturation.

At a

feedback loop

2

No

circuit

in

A

in

Reference

open-loop fashion

at

1

switched capacitor

for

1

any time,

order to avoid

in

switched capacitor alone should not be used

minimum add

stray charge

around an

nodes must be completely isolated by capacitors

accumulations can be discharged.

OA

A

path must exist

As explained

at the

earlier, the

summing node

The noninverting

connected

OA

that

in

leading to saturation of the

order to avoid

OA

bottom plate of every capacitor should be connected either

directly or through a switch to

4

ground so

This implies that a the feedback path

must be closed by a switched capacitor (dc feedback)

charge accumulation

in the

an unswitched capacitor to the feedback loop.

either directly or through a switched capacitor to a voltage source to

3.

and

topologies combined with the seven guidelines listed below will be utilized.

1.

1

TSC

ground or

to a

voltage source

input should be kept at ac ground

to a signal voltage, the circuit

tends to

become

If this input

sensitive to

terminal

all

is

parasitic

capacitors from switches, signal lines, and the substrate

5

Provide separate bias lines for the analog and

capacitor circuit.

digital circuitry

in

the switched

This will help prevent the switching noise from infiltrating the

SC

circuit.

6

Lines with digital signals should be kept as far away as possible from lines that

carry the analog signal.

7

Due

to

sampling, clock feed through usually aliases

offsets of the

OAs.

Its

origin

is

overlap capacitors of the switches

minimized by maximizing the

found

at

in

down

43

dc and adds

to the

dc

the gate-to-source or the gate-to-drain

the inputs to the

size of the

to

OAs

This effect can be

unswitched feedback capacitor

2.

A

Stray Insensitive

Using

both

the

TSC

seven

Implementation of the Lossy Integrator

switched

capacitor

network

design

and

layout

precautions and the three rules for nullifying stray capacitance, coupled with the toggle

switched capacitor topology, the lossy integrator circuit will be transformed into a stray

insensitive switched capacitor network

Figures 5.6 through

The

This transformation

performed pictonally

in

5 15.

transfer equation for Figure 5 15

is

-

c

Vout

i

=

v*

l

This equation clearly shows as does Figure

capacitor lossy integrator can be made.

is

is

one approach used

to

overcome

z2

(5.4)

-z-

5 15 that

1

a stray insensitive toggle switched

The toggle switched capacitor (TSC) topology

the effective parasitic capacitance problem, another

the modified open-circuit floating resistor

(mOFR)

44

topology.

is

R,

v.

Figure 5.6

Lossy Integrator

45

*.

*„

4>.

Figure 5.7

<t>

Toggle Switched Capacitor Implementation of the Lossy Integrator

46

<J>.

<t>

-c sw

Figure 5.8

TSC

c

—

-c m

Lossy Integrator with Stray Capacitances

47

c-

-c.w

c,,

c comb

c comb

*,—

—

a

*.

c„—

<t>

;

comb

''comb

—

c,

*„

*.

*,

r

t>

<t>.

Figure 5.9

TSC

Lossy Integrator with Combined Stray Capacitances

48

'comb

''comb

<*>„—

''comb

c

—

''comb

*„

V;„

<t>„

<t>

Figure 5.10

TSC

Lossy Integrator with Reduced Combined Capacitances

49

*.

c comb

v

c

^comb

c.

c comb

''comb

V..

I

Figure 5.11

TSC

i

Lossy Integrator with

Odd

50

Phase Clock Active

c,

v„

Figure 5.12

TSC

Lossy Integrator with <& Active and Effective Capacitances

51

c comb

'comb

C

^comb

''comb

a

c,

±

Figure 5.13

n(b

TSC

Lossy Integrator with Even Phase

52

Qock

Active

Ci

Figure 5.14

TSC

Lossy Integrator with

O

e

53

Active and Effective Capacitances

4>

<t>e

Ci

*-

<f>.

Figure 5.15

<f>

Stray Insensitive Toggle Switched Capacitor Lossy Integrator

54

3.

A

Stray Insensitive

Using

both

the

mOFR

seven

Implementation of the Lossy Integrator

switched

capacitor

network

and

design

layout

precautions and the three rules for nullifying stray capacitance, coupled with the modified

open-circuit floating resistor topology, the lossy integrator circuit will be transformed into

a

stray

insensitive

switched capacitor network

This transformation

is

performed

pictonally in Figures 5.16 through 5.25.

The

transfer equation for Figure 5.25

is

c

Vout

1

This equation clearly shows as does Figure

in

be studied

in this thesis to

(5.5)

-z-

5 .25 that

circuit floating resistor lossy integrator can be

will

1

i'

=

v*

approach that

-

made

1

a stray insensitive modified open-

The

mOFR

topology

is

the last

eliminate the effects of parasitic capacitance

switched capacitor networks.

55

R

v,.

Figure 5.16

Lossy Integrator

56

<t>

c

*„

t

v„

;

*.

*.

Figure 5.17

MOFR

Implementation of the Lossy Integrator

57

<t>„

<t>

<t>

4W

C sw

SW

~c_ C

C,

<t>

V..

c

"C.wC^

*

Figure 5.18

ra

— ^«

MOFR

—

c b-

v sw

c.sw

w c

A

Lossy Integrator with Stray Capacitances

58

b

—

c.|W

w c

"!W

ccomb

*„

Figure 5.19

MOFR

—

'comb

C.

Lossy Integrator with Combined Stray Capacitances

59

<*>o

c comb

c comb

<t>

c comb

<J>

"'comb

C,

<t>

—

C^

*

*„

c,

*.

*e

\S

Figure 5.20

MOFR

Lossy Integrator with Reduced Stray Capacitances

60

*o

com b

'comb

a

n

^comb

''comb

H

a

1

i

\_

i

iv„

Figure 5.21

MOFR

Lossy Integrator with

61

Odd Phase Oock

Active

Ci

v,

Figure 5.22

1M0FR

Lossy Integrator with

<t>

62

Active and Effective Capacitances

''comb

"'comb

^nTb

''comb

''comb

I

c,

Figure 5.23

MOFR

Lossy Integrator with Even Phase

63

Cock

Active

c,

Figure 5.24

MOFR

Lossy Integrator with <D e Active and Effective Capacitances

64

4>

<t>

*.

4>

/

4>

Figure 5.25

4>.

Stray Insensitive

MOFR

Lossy Integrator

65

<t>

E.

SUMMARY

Stray

insensitive

implemented using a

switched

total

capacitor

networks

can

be

easily

designed

of ten guidelines and an effective circuit topology

and

The toggle