* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download AN-4108 A Fairchild Power Switch based on Switched Mode Power

Spark-gap transmitter wikipedia , lookup

Power factor wikipedia , lookup

Ground (electricity) wikipedia , lookup

Electrification wikipedia , lookup

Audio power wikipedia , lookup

Electrical ballast wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Electric power system wikipedia , lookup

Power over Ethernet wikipedia , lookup

Three-phase electric power wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Amtrak's 25 Hz traction power system wikipedia , lookup

Current source wikipedia , lookup

Power inverter wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Stray voltage wikipedia , lookup

Power engineering wikipedia , lookup

Voltage regulator wikipedia , lookup

History of electric power transmission wikipedia , lookup

Electrical substation wikipedia , lookup

Surge protector wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Voltage optimisation wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Distribution management system wikipedia , lookup

Mains electricity wikipedia , lookup

Alternating current wikipedia , lookup

Opto-isolator wikipedia , lookup

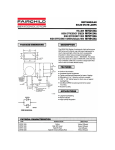

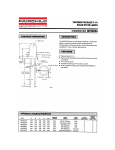

www.fairchildsemi.com Application Note 4108 A Fairchild Power Switch based on Switched Mode Power Supply for CRT Monitor Use 1. Introduction This application note describes a complete flyback switched mode power supply that uses a Fairchild Power Switch. The MOSFET and its control IC are built into one package. The MOSFET is in fact a SenseFET. Various protection features are also included. Fairchild Power Switch can enhance the reliability and productivity of the system when compared to other designs. The FS6S series has a more rugged SenseFET than the previous Fairchild Power Switch series. The FS6S series features include burst mode operation for low power consumption in DPMS mode. This application note describes the features and design considerations of the FS6S series for the monitor power supply, which improves upon the existing KA5S-series. FS6S series has three package types: TO-3P-5L, TO-220-5L and TO-220F-5L as shown below. Fairchild Power Switch is classified according to the voltage and current rating of the internal SenseFET. The TO-220-5L FS6S series has a synchronization pin, which accepts an external sync signal. In order to remove the screen noise generated by the switch action, the FS6S series synchronizes its switching with the external sync signal. When in power saving mode, the FS6S series pulls down the output voltages to a predetermined level and enters burst mode with a switching frequency of 50kHz. TO-220F-5L TO-3P-5L Figure 1-1. Package Line-Up Rev. 1.0.3 ©2002 Fairchild Semiconductor Corporation AN4108 APPLICATION NOTE 2. Internal Block and Important Features Table 1: Product Line-up (Monitor Application) Product Rating Package FS6S0765RCB 7A/650V TO-220-5L FS6S0965RT 9A/650V TO-220F-5L FS6S0965RCB 9A/650V TO-220-5L FS6S1265RE 12A/650V TO-3P-5L FS6S1565RB 15A/650V TO-3P-5L Vref SoftStart & Sync 2.1 Internal Block and Features • • • • • • Current Control Mode Burst Mode Operation Higher Rugged SenseFET (QFET) World wide Input voltage Optimum Gate Driver Low Standby Power Consumption (Low start-up current & low operating current) • Various Internal Protection Circuits (Auto-restart) – Over Voltage Protection (OVP) – Over Load Protection (OLP) – Thermal Shutdown Protection (TSD) – Over Current Latch (OCL) • Minimization of production defects through the VCC surge and internal diode reinforcement. • Reduction of secondary side diode voltage stress at start and other transient condition by employing slope at sync threshold voltage. Vcc Drain 3 1 Vpp=5.8/7.2V Internal Bias OSC 5 Vref Vref UVLO Burst mode controller Vfb Vth=1V S Ron Q R Vcc Vth=11V/12V Roff PWM Feedback 4 2.5R R Ifb Vref Vfb Offset Vcc Rsenese Idelay OCL OLP Vth=7.5V S Vcc Vth=30V OVP UVLO Reset (Vcc=9V) Q Filter (130nsec) Vth=1V 2 GND TSD (Tj=160 ℃ ) R Figure 2-1. Internal Block Diagram 2 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 2.2 Starting resistance design and UVLO Input voltage range: 80 ~ 265V (Ac) Rstart DC Link + At Minimum Input Voltage Va(ave), the starting resistance is: Cvcc 0 1 π Va ( ave ) = ------- ∫ ( Vp ⋅ sint – 15 ) dt 2π o 2Vp – 15π = ----------------------------2π Internal Bias Power On Reset 1 2 15V/9V 5V Vref UVLO Good Logic 0 0 Select: Rstart =142.5KΩ 0.5W At the minimum voltage, the starting resistance is set to ensure that the current through it is larger than the maximum start up current for the Fairchild Power Switch (170µA). The starting resistor produces a starting current, which charges the VCC capacitor. The Fairchild Power Switch starts switching the internal SenseFET when the VCC voltage becomes greater than 15V (the start voltage). Once it starts to operate, the current drawn by the control IC suddenly increases to 10mA. The starting resistor cannot source this and consequently, the transformer auxiliary winding supplies most of the IC current after start up. The start time will be delayed if the VCC capacitor is too large, so a moderate size capacitor should be used. Generally, 22 ~ 47µF capacitor values are considered good. This operation is described in Figure 2-2. VCC only needs to be maintained above 9V after starting, but should be set so that OVP (Min. VCC voltage above 27V) is not triggered. Approximately 24V is appropriate for the VCC voltage. ICC [mA] 20 9 Power On Reset Range 0.1 VCC VZ [V] Figure 2-2. Start-up Waveform Figure 2-3. UVLO Block 2.3 Fairchild Power Switch Protection Circuits. 2 Va ( rms ) P ( loss ) = ---------------------------- = 0.22W Rstart ©2002 Fairchild Semiconductor Corporation 2 0 (Vp = 265 2 ) 15V - 3 Fairchild Power Switch(SPS) 2 1-----∫ ( Vp ⋅ sin t – 15 ) dt 2π 9V 3 Vz and, at Maximum Input Voltage Va(rms), the power loss is: 6V + 9V Rstart = 28.5 ÷ 200µA = 142.5K Va ( rms ) ≅ 177V 1 Latch Comparator 2 × 80 2 – 15π = ----------------------------------------- = 28.5V 2π Va ( rms ) = 0 3 Fairchild Power Switch has several self-protection circuits, which can be used without adding external components, thus providing system reliability without increasing cost. Under auto restart mode, protection circuits become deactivated when VCC falls below 9V (stop voltage), after which Fairchild Power Switch tries to restart. Under latch mode, protection circuits become deactivated only when VCC falls to 6.5V (reset voltage), then Fairchild Power Switch tries to restart. When VCC drops to 9V due to latch protection, the operating current of the IC drops from 10mA to 100µA. Therefore the VCC capacitor starts to charge towards 15V through the starting resistor. For VCC to fall to 6.5V (reset voltage), the input voltage must be removed. 2.3.1 Over Load Protection (OLP) Overload as described here is different from a load short circuit. It is a condition where a load becomes greater than the preset level, though it is operating normally. Essentially, the overload protection circuit forces Fairchild Power Switch to stop its operation if the load draws a higher current then the predetermined maximum value. A problem associated with this type of protection circuit is that it can trigger erroneously on load transients. As a security measure, Fairchild Power Switch triggers the protection circuit after a specific time delay. This avoids false triggering on short load transients. The above operations are executed as follows. Since Fairchild Power Switch uses current mode control, maximum switch current is limited internally. For a fixed input voltage, this limits the power. Therefore, if the power at the output exceeds this maximum, VO shown in figure 2-4 becomes less than the set voltage, and KA431(LM431) can draw only the allowed minimum current. As a result, the photo-transistor’s current becomes zero. If all the current of the 0.9mA Fairchild Power Switch current source flows through the internal resistor (2.5R+R= 3.3K), Vfb becomes approximately 3V. At this time the 2µA current source starts to charge Cfb. Because the photo transistor’s current is zero, Vfb continues to increase. The Fairchild Power Switch shuts down when Vfb reaches 7.5V. The shutdown delay time can be easily determined as the time required to increase the Cfb by 4.5V (from 3V to 7.5V) using 2µA. When Cfb is 47nF, 3 AN4108 APPLICATION NOTE delay time is approximately 100ms. Fairchild Power Switch will not shut down within this time. Increasing Cfb to get a longer delay time can become a problem, because Cfb is an important parameter in determining the SMPS dynamic response time. One method to delay the shutdown time is to add a resistor between the F/B pin and GND and to subtract the amount of the delay current. When the 4. 7MΩ resistor was used experimentally with Cfb of 47nF, shutdown time was almost doubled to 180~200ms. When Vfb voltage is 7.5V, the current flowing to the 4.7MΩ resistor is approximately 1.6µA. To obtain the same results, a zener diode (approx. 3.9V) can be series-connected to a capacitor (47nF) which can then be parallel connected to Cfb as shown in Figure 2.4. Fairchild Power Switch(SPS) 2uA 0.9mA Vo D1 Vfb D2 4 Idelay 1 4 2 3 Cd Cfb 0 Vfb* 1 Vz=3.9V 0 0 6 8 KA431 7.5V 3 + 2 - 1 0 OLP Latch Figure 2-4. Fairchild Power Switch Long Delayed Shutdown 2.3.2 Over voltage Protection 2.3.3 Over Current Protection (OCP). Fairchild Power Switch has self protection features that function even when abnormal states occur such as an open or short circuits in the feedback loop. When the feedback terminal shorts as viewed from the primary side, the feedback terminal voltage becomes zero and prevents switching from starting. If it opens, the protection circuit acts as an over voltage protection circuit. When there is an abnormal state or a possibility of opening due to improper soldering etc. in the secondary side feedback circuit, the primary side continues to switch using the maximum set current until the protection circuit starts to operate. In such instances, it is common for the secondary side voltage to become greater than the rated voltage, which can lead to a fuse blowing or, more seriously, a fire if a protection circuit is not in place. Even if this was not the case, ICs immediately connected to the secondary output without a regulator can be destroyed. Therefore, Fairchild Power Switch employs the over voltage protection circuit to protect against feedback anomalies. The Fairchild Power Switch VCC is proportional to the output voltage. When the Fairchild Power Switch VCC exceeds 30V, the over voltage protection feature is triggered. Therefore, VCC must be maintained at less than 30V during normal operation. The existing concept of Ipeak control does not go beyond limiting the amount of current during normal operation. The OCP block prevents damage to Fairchild Power Switch from abnormal states, such as a diode or a load short. A diode or a load short causes a large current to flow through the SenseFet for a short time. This can be tens of amperes. The leading edge blanking circuit sets the minimum turn on time at 600nS. Tens of amperes for 600nS could destroy the Fairchild Power Switch and so the OCL block senses this instantaneous current and latches like the existing protection circuits. 4 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 frequency synchronization method which uses the horizontal deflection frequency delivered to the number 5 pin of the Fairchild Power Switch. Figure 3-1 shows the circuit around the pins. At start up, a ramp is generated on pin 5 by charging Cs with Ifb and the current through the 50kΩ resistor. This ramp increases the maximum duty cycle slowly, which results in soft start. After the soft start, Vcs remains at 5V and thus the voltage at pin 5 becomes 5V DC plus the external sync input. The sync comparator generates the comparator output waveform (Vcomp) by comparing the voltage of pin 5 with a sawtooth waveform of 5.8~7.2V as shown in Figure 3-1. The internal timing capacitor, Ct, charges and discharges between 5.8 and 7.2v thresholds. The oscillator output waveform VCK becomes low while Ct charges and high while it discharges. This output signal is sent to the set terminal of the S/R latch. Figure of OCL Operation 300ns Minimum Turn-on Time 1 Latch S Q` 2 3 2V Vrs 0V R Vpin5 1 + 3 - 2 5V 0V Vcomp 0V Vthh Rsense OCL Level Vct Vthl 0V 0 0 Vsync.th Vck Figure 2-5. Over Current Latch (OCL) 0V 3. External Frequency Synchronization Method Figure 3-1 Synchronous Operation As mentioned, Fairchild Power Switch operates within a wide frequency range synchronized to the horizontal deflection frequency of a monitor. This section describes the Ifb SPS PWM Comp 3 50K 5 0 sync comp + Cs External Sync Input 1 + 2 - 5V Vcs 3 + 2 - Vcomp 1 OSC 7.2V Rs Vrs 5.8V 0 Figure 3-2. Synchronization Circuit ©2002 Fairchild Semiconductor Corporation 5 AN4108 APPLICATION NOTE V th h = 7 .2 V V sync V th l= 5 .8 V P in 5 Figure 3-3 Negative Slope Synchronized to Sync Pulses The inverse slope of the oscillator output becomes the sync comparator reference, Vsync, which oscillates between 7.2V and 5.8V with the basic frequency of 25kHz. When the sync signal is applied or Vsync reaches at 7.2V, the voltage of Ct, Vct, starts to decrease toward the low threshold voltage, Vthl as shown in Figure 3-2. The oscillator output, Vck, outputs a high signal while Vct decreases. As soon as Vct comes down to Vthl, Vct starts to increase, Vck drops down, and the SenseFET gate turn on signal is generated. The high duration of Vck is restricted to 5% of one switching period to keep switching noise off screen. If a constant sync comparator reference is used, the SenseFET can be turned on just after being turned off by the first sync signal. In this case the secondary rectifying diode is turned off while it is still conducting. This causes a high reverse voltage spike between the anode and cathode of the diode due to the long reverse recovery time. In order to solve this problem, FS6S series uses the negative slope as the sync comparator reference. Generally the levels of sync pulses increase gradually to a certain value. If these gradual increasing sync pulses are compared with the negative slope, the first sync pulse that touches the negative slope will be placed in the back area of the basic period of the oscillator as shown in Figure 3-3. This makes the Mosfet turned off at low or no current levels of the secondary windings of the switching transformer, which can reduce the reverse voltage spike of the rectifying diode significantly. The level of the applies sync signal should be large enough to cross the sync threshold. The level should not exceed 9V for safe frequency synchronization since it is clamped by the 9V voltage source at the sync comparator terminal in the Fairchild Power Switch. Furthermore, the sync signal is added to DC 5V across the soft start capacitor on pin 5. Therefore, the voltage level should be between 8V and 9V (pure sync signal voltage level is 3 ~ 4V) for safe frequency synchronization. Fairchild Power Switch through a transformer. Delay time is short and thus the switching noise is pushed to the left of the monitor screen, and does not appear in the visible area. One turn from the FBT can also used instead of the sync. 3.2 Photocoupler Method Unlike the sync transformer method, this method produces a slight delay time but almost no noise on the screen. The zener diode can compensate the Current Transfer Ratio (CTR) of photocoupler. Though this method is not frequently used, it has a few advantages for auto-assembly during manufacture. 3.3 Quasi Resonance Method The resolution on the screen is slightly poor when using the quasi-resonance method. Switching noise is present on the screen but is not visible since it is not correlated with the picture scan. The Fairchild Power Switch does not depend on the external sync signal but uses the self oscillation frequency which varies with load. However, additional devices, such as the sync transformer or photocoupler etc., are not required because the Fairchild Power Switch is not synchronized to the sync frequency. The method is not only highly cost competitive but also advantageous in terms of power loss because it uses zero voltage switching. 3.1 Sync Transformer Method This is the most commonly used method for frequency synchronization in monitor designs and is shown in Figure 3.4. The horizontal sync signal is applied to pin 5 of the 6 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 R102 4. Display Power Management Signalling (DPMS) Design Method D102 R103 IC101 5 S/S Vfb kbreak 2 GND 3 + 1 Drain 4 TX2 Vcc C110 FS6S0965R C201 kbreak Sync Signal(from H_DRV) C108 4.1 Burst Mode Operation + C109 R104 D104 D103 0 IC301 4 1 3 2 0 Figure 3-4. Sync Transformer Synchronization Method R102 R103 R201 IC101 5 S/S Drain 4 1 Vfb 4 GND 3 + 2 1 kbreak 2 Vcc C110 3 FS6S0965R U5 C108 + C109 R104 D105 0 IC301 4 1 3 2 0 Figure 3-5. Photocoupler Method R102 The FS6S-series has a particularly useful function for the DPMS mode: burst mode operation. Normally, customers use an auxiliary power system for DPMS in large monitors. This method can lower power consumption but increases costs. The FS6S-series can drop the output voltage with only minimal external components by using burst mode. This reduces power loss in DPMS mode. In the DPMS mode, Vfb is pulled low by the external micro-controller. 4.2 Implemetation of the Burst Mode D102 R109 Sync Signal(from H_DRV) With high interest in power management recently, much effort has been concentrated in implementing the DPMS mode. The FS6S series uses burst mode for DPMS in order to achieve cost effectiveness and minimize the power consumption. The required circuit for implementing the burst mode is shown in Figure 4-1. Q1, D1, Rx, R5 and R6 are added to the secondary feedback network. During normal operation, Q1 is on, which isolates Rx from the feedback network. Vo2 is sensed and the amplified error is transferred to the primary side through the photo coupler. By turning off Q1, Rx is connected to the feedback network. The error amplifier increases the current through the photo coupler, and thus Vfb of FS6S-series drops to zero. Therefore no additional opto coupler is required to switch into burst mode. Rx can be calculated by the following equation when KA431(LM431) is used as an error amp. R7 × R8 ( Vol – 2.5 – V D1 ) Rx < ---------------------------------------------------------------------2.5 ( R7 + R8 ) – R8 ⋅ Vo2 where Vo1 and Vo2 are the reduced voltages in burst mode. D102 R103 IC101 5 S/S Drain 4 Vfb GND 3 1 Resonance CAP C112 1n 2 Vcc FS6S0965R R110 D103 C108 + C109 R104 C111 0 IC301 4 1 3 2 0 Figure 3-6. Quasi-Resonance Method ©2002 Fairchild Semiconductor Corporation 7 AN4108 APPLICATION NOTE Vo2 Vo1 R7 Ib Ic R1 Ia R2 4 1 3 2 R3 Rx R5 R8 C1 1 Micom signal D1 Q1 8 R6 6 KA431 Figure 4-1. Rx Setting Circuit for Burst Mode Operation 4.3. Experimental Results of Burst Mode Operation 4.3.1. VCC/Vds and Vregin/Vregout waveforms in burst mode. Vcc 5V/div Vds 200V/div Figure 4-2. VCC/Vds in Burst Mode Operation 8 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 Vregin 2V/div Vregout 1V/div Figure 4-3. Vregin/Vregout Operation in Burst Mode. Experimental results are shown in, Figure 4-2 and Figure 43. With minimum load and normal operation: Vac = 240V, Pin = 4.82W, VCC = 20V, Vo = 190V and Vregin = 12.24V. When Fairchild Power Switch operates Burst Mode: Pin = 2.72W, VCC = 11~12V, Vo = 132V and Vregin=7.07V 4.5 Circuits for DPMS mode T1 D201 1 16 + 2 L201 BD101 C107 + R101 C201 + C202 1 3 C106 + 2 15 3 14 IC202 - D202 1 4 D101 L202 4 + 0 RT101 4 R206 + C203 VIin Vout Vc GND 2 3 C204 Q201 13 C105 R102 D102 R207 D204 6 1k R103 Suspend Signal(from micom) D203 12 1 5 4 3 C110 Q202 + + C205 S/S 3 IC101 + C206 1 Drain R208 11 Vfb 2 GND Vcc R209 FS6S0965R C103 Off -Signal(from micom) C108 External Sync + R104 Q203 Q204 C104 C102 2 L203 7 Line Filter: LF101 C109 TRNSFMR DEL16-640A11_1 C301 C302 C101 0 F101 FUSE R203 R204 IC301 4 1 3 2 C207 1 0 IC201 R205 R201 6 8 R202 Figure 4-4. Micro Controller Method for Controlling DPMS Mode ©2002 Fairchild Semiconductor Corporation 9 AN4108 APPLICATION NOTE T1 D201 1 16 + 2 L201 BD101 C107 + R101 C201 + C202 1 3 + C106 2 15 IC202 D202 - 3 14 1 4 D101 L202 4 + C203 0 RT101 R206 + VIin Vout Vc GND 2 3 C204 R102 4 Q201 13 C105 R103 D102 R207 D204 6 1k Suspend Signal(from micom) D203 12 1 4 3 + C110 + C205 S/S Drain Vfb GND Q202 + 3 IC101 5 2 L203 7 Line Filter: LF101 C206 1 R208 11 2 Vcc R209 Q203 FS6S0965R C103 Q204 C104 Off -Signal(from micom) C108 C102 External Sync R104 + C109 TRNSFMR DEL16-640A11_1 C301 C302 C101 0 F101 FUSE u-com R203 R204 R210 5V-Reg IC301 4 1 3 2 0 C207 1 0 IC201 R205 D7 R201 8 6 Q205 R202 LOW:Off -mode Figure 4-5. Using Burst Mode Operation for DPMS. 10 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 5. Monitor Application 5.1 Flyback converter demo circuit T1 D201 1 16 + 2 L201 BD101 1 C107 47nF/630V 3 + + R101 68K/2W C106 220uF/400V 19T + C201 22uF/400V 46T 2 15 3 14 C202 22uF/400V R201 300k R209 33K R202 4.2k D202 4 - 180V 300mA L202 D101 + 18T 0 RT101 + C203 47uF/160V 37T 4 C204 47uF/160V 13 80V 100mA C105 R102 D102 D203 6 12 15 R103 150K/1W + 11T 7 Line Filter: LF101 IC101 4 3 + C108 1uF/50V C103 S/S Drain Vfb GND + C206 1000uF/35V 15V 800mA D204 1 11 2 Vcc L204 C207 1000uF/35V + 5 L203 C205 1000uF/35V 7T FS6S0965RT C208 1000uF/35V + 47nF -15V 600mA 7T C104 D205 4.7nF 4.7nF C102 47nF 10 External Sync R104 470 C110 C109 47nF L205 + + 3T 47uF/50V + C209 1000uF/16V C210 1000uF/16V 9 C9 6.5V 600mA C10 C101 TNR 4.7nF 4.7nF 0 F101 FUSE 3 2 R205 33k R206 2.7k R207 4.7K C211 47n 1 Sw201 Switch 0 IC201 KA431(LM431) D206 IC202 KA7805 1 VIN GND R204 1k 1 3 R203 1k IC301 HC11A817A 4 VOUT 2 + C212 100u/16V R210 39 5V 130mA Q201 8 6 R208 4.7K Figure 5.1 Fairchild Power Switch Flyback Converter DEMO BOARD for a Monitor Application ©2002 Fairchild Semiconductor Corporation 11 AN4108 APPLICATION NOTE 5.2 Part List for Fairchild Power Switch Flyback Converter DEMO BOARD for a Monitor Application Part Name Value Part Name Value LF101 BSF-1925 R206 33K, 1/4W IC101 FS6S0965RCB R207 2.7K, 1/4W BD101 KBL407 R208 4.7K, 1/4W RT101 NTC R209 4.7K, 1/4W R101 68K,3W R210 39, 1/4W R102 15, 1/4W C201 22µF/400V R103 150K, 1W C202 22µF/400V R104 470, 1/4W C203 47µF/160V C101 TNR C204 47µF/160V C102 BOX CAP, 47nF C205 1000µF/35V C103, C104 EMI FILTER CAP, 47nF C206 1000µF/35V C105 BOX CAP, 47nF C207 1000µF/50V C106 220µF/400V C208 1000µF/50V C107 47nF/630V C209 1000µF/16V C108 47µF/50V C210 1000µF/16V C109 47nF/50V C211 47nF / 50V C110 1µF/50V C212 100µF/16V D101 UF4007 D201 RG4C D102 TVR10G D202 SUF15J - - D203 UG4D IC201 KA431(LM431) D204 UF1G IC202 KA7805/LM7805/MC7805 D205 UG4D R201 120K, 1/4W D206 TVR10G R202 1.8K, 1/4W - - R203 33K, 1/4W IC301 QT817A R204 1K, 1/4W C301 4.7nF/2KV R205 1K, 1/4W C302 4.7nF/2KV Parts in Boldface are available from Fairchild Semiconductor. 12 ©2002 Fairchild Semiconductor Corporation APPLICATION NOTE AN4108 5.3 Transformer Specification 1 16 (8)17T φ = 0.3mm (3-ply) 170V 15 (2)33T φ = 0.3mm (2-ply) Lm = 330µH 2 Vin 14 75V GND2 13 3 (1)18T φ = 0.3mm (3-ply) 12 11V 4 11 15V (6)27T φ = 0.3mm (2-ply) (5)6T φ = 0.3mm (4)9T φ = 0.2mm 10 6 (7)9T φ = 0.3mm 6.3V Bias Winding Core: EER4044 Bobbin: EER4044 1: (4) → (3) 18T 2: (16) → (15) 33T 3: (10) → (9) 3T 4: (11) → (9) 9T 5: (12) → (9) 6T 6: (14) → (13) 27T 7: (6) → (7) 9T 8: (2) → (1) 17T φ = 0.3mm (3 ply-wire) φ = 0.3mm (2 ply-wire) φ = 0.45mm φ = 0.2mm φ = 0.3mm (3 ply-wire) φ = 0.3mm (2 ply-wire) φ = 0.3mm φ = 0.3mm (3 ply-wire) (3)3T φ = 0.45mm GND1 9 7 Figure 5-2 FS6S0965RCB Transformer Specification for a 95W Monitor Application. 1 18 190V (8) 15T φ = 0.25mm (9-ply) 17 (2) 60T φ = 0.45mm Lm = 230µH 2 16 Vin 85V GND2 3 (1) 16T φ = 0.25mm (9-ply) 15 14 15V 4 13 25V 12 6.5V 6 GND1 (5) 5T φ = 0.45mm (4) 8T φ = 0.3mm (3-ply wire) Core: EER4445 Bobbin: EER4445 1: (4) → (3) 16T 2: (18) → (15) 60T 3: (12) → (11) 2T 4: (13) → (11) 8T 5: (14) → (11) 5T 6: (16) → (15) 27T 7: (6) → (7) 8T 8: (2) → (1) 15T φ = 0.25mm (9 ply-wire) φ = 0.45mm φ = 0.45mm φ = 0.3mm (3 ply-wire) φ = 0.45mm φ = 0.45mm φ = 0.3mm φ = 0.3mm (9 ply-wire) (3) 2T φ = 0.45mm Bias Winding (7) 8T φ = 0.3mm (6) 27T φ = 0.45mm 11 7 Figure 5-3. FS6S0965RCB Transformer Specification for a 120W Monitor Application. ©2002 Fairchild Semiconductor Corporation 13 AN4108 APPLICATION NOTE - FS6SXX65R Comparison Table of Electrical Characteristics FS6S-series Content KA5S-series KA2S-series Unit Min Typ Max Min Typ Max Min Typ Max Start-up Current - 100 170 - 100 170 100 300 550 uA Operating Current - 10 15 - 7 12 6 12 18 mA Initial Frequency 22 25 28 18 20 22 18 20 22 Khz Burst Mode Frequency 40 50 60 - - - - - - Khz Over Current Protection 0.9 1.0 1.1 - 1.1 - - - - V Burst Mode Ipeak 0.6 0.85 1.1 - - - - - - A Burst Mode Range 11.0 - 12.0 - - - - - - V Over Voltage Protection 27 30 33 23 25 28 23 25 28 V Shutdown Delay Current 1.6 2.4 2.4 3.0 4.0 5.0 1.4 1.8 2.2 uA Table 3. FS6S-Series Comparison with Previous KA5S and KA2S - Series Author: Keuneui Hong (FAIRCHILD) Experience: Participated in the development of Fairchild Power Switch in 1995. Presently, responsible for the development and application of IC for the monitor. E-mail: [email protected] Tel: 82-32-680-1834 Fax: 82-32-680-1317 ©2002 Fairchild Semiconductor Corporation 14 APPLICATION NOTE AN4108 ©2002 Fairchild Semiconductor Corporation 15 AN4108 APPLICATION NOTE DISCLAIMER FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. LIFE SUPPORT POLICY FAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user. 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness. www.fairchildsemi.com 5/10/02 0.0m 002 Stock#ANxxxxxxxxx 2002 Fairchild Semiconductor Corporation