* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download The Wire - WSU EECS

Survey

Document related concepts

Transcript

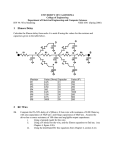

Wire Indctance • Consequences of on-chip inductance include: – Signal ringing – Over-shoot – Signal reflection due to impedance mismatch – Inductive coupling between lines – Switching noise due to Ldi/dt voltage drops. • • The inductance of a section of a circuit can be evaluated as V = Ldi/dt Inductance per unit length of wire and capacitance C are related by the expression CL=ε. • • • • • An ideal wire assumes that a voltage change at one end of the wire propagates immediately to the wire’s other end. The wire becomes equipotential. This ideal approach still holds for short wires, also designers interested only in circuit behavior can use this ideal model. Circuit parasitics of a wire are distributed along its length instead of being lumped at a single position. With low to medium switching frequencies and small resistive components we can consider only a lumped capacitive component of wire. Lumped C Wire Model Vout Cwire Driver Vout RDriver Source CLumpe d • This is a simple but yet effective model and widely used in digital design. • There is a need to include the resistive as well as the capacitive components. • We can lump the total wire resistance into a single R and the global capacitance into a single C. • The lumped RC model is inaccurate for long interconnects. • The RC network can enhance understanding of a distributed RC network. • In order to evaluate the RC model we use the RC tree which has: – Has a single input node S. – Has all capacitors between a node and ground. – Has no resistive loops The Lumped RC Model • The resistive-capacitive (RC) model.R 2 2 1 S C2 R3 R1 3 C1 R1 C1 4 C4 Ri C3 R2 R4 i Ci C2 R3 C3 td 2 C1R1 C2 R1 R2 C3R1 • R1 is the common resistance in the path. • There is a unique resistive path between the source node S and any node i on the network • A shared path resistance from the root node to nodes k and i is: Rik R j R j pathS i paths k • The equation describes the common resistance from input to nodes i and k. • The Elmore Delay Model • If we have a step input and if we assume that all nodes are initially at logic 0 we have: di N C k 1 k Rik • The Elmore Delay Model offers designers a quick estimate of the delay. • To compute the time constant of a wire of length L, we partition the wire into N identical segments. • Each segment has a length of L/N. • The segment resistance becomes r(L/N). • The segment’s capacitance becomes c(L/N). 2 DN L rc 2 rc Nrc N N N 1 N 1 rcL2 RC 2 2N 2N • The above equation calculates the time constant of the wire using the Elmore Delay Model. • For rL = R and cL = C we have the Lumped R and C. • If there are numerous segments (N Large) the RC model approaches that of a distributed rcL RC line with: RC 2 2 2 DN The Elmore Delay Model • The delay of a wire is a quadratic function of its length i.e. doubling the length of a wire quadruples its delay. • The lumped RC model underestimates the delay by 0.5 times. • The Elmore Delay model only estimates the value of the dominant component. • We have discussed briefly that the Elmore Model can be used to estimate the delay complex transistor netwworks. Vin rL Vj-1 rL Vj rL Vj+1 rL cL cL Ij-1 Ij cL Vout cL Ij+1 • Find the voltage at node i? • Find the response at node i with respect to time? C V V j V j V j 1 dVi I j 1 I j j 1 dt R R cL V j t V j 1 V j V j 1 V j rL • As the number of segments in the network becomes large with sections becoming smaller we dV have: rc dV dt dx 2 2