* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Document

Thermal runaway wikipedia , lookup

Josephson voltage standard wikipedia , lookup

Schmitt trigger wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Integrated circuit wikipedia , lookup

Galvanometer wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Valve RF amplifier wikipedia , lookup

Power electronics wikipedia , lookup

Surge protector wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Two-port network wikipedia , lookup

Operational amplifier wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Current source wikipedia , lookup

Rectiverter wikipedia , lookup

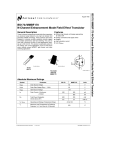

Power MOSFET wikipedia , lookup

Opto-isolator wikipedia , lookup

EE 338L CMOS Analog Integrated Circuit Design Lecture 7, Current Mirrors/Sources Current mirrors/sources are widely used in analog integrated circuits. They can work as (i) Bias circuit, and/or, (ii) Signal processing circuit, such as, current source load for common source amplifiers, tail current source for differential pairs, bias currents for folded cascode amplifier. VDD IB M1 vin VDD M2 M3 vout M1 M2 vin1 vin2 VP ISS vb Fig. a Fig. b vDD vDD vin1 M1 M2 vin1 VP vout M1 IB vin vin2 M1 M2 vb1 vin1 M1 M2 vb1 VP VP vb2 ISS Fig. c The current sources can be copied from a reference master current source, which usually comes from a band-gap reference circuit. How could we generate copies of currents from a reference current source? The answer is to use – current mirrors! The basically principles of current mirrors are very simple, as shown in the next page. S. Yan, EE 338L 1 Lecture 7 IREF Iout=ID2 ~ IREF + W/L M1 ID1=IREF - W/L M2 VGS M1 M2 IREF VGS ID2 Basic Current Mirror For a MOSFET, if ID=f(VGS), then VGS=f-1(ID), Iout=f[f-1(IREF)]=IREF. Here we assume M1 and M2 have the same size and VDS. Iout IREF Vdsat As VDS1=VGS, when VDS2=VGS, we have VGS VDS2 VGS1=VGS2= VGS, VDS1=VDS2=VGS. If M1 and M2 have the same size, their drain currents are equal. (Why?) Note that for a MOS transistor in saturation, ID 1 W KP (VGS VT )2 (1 VDS ) 2 L We have I D1 1 W K P (VGS VT ) 2 (1 VDS1 ) , and 2 L 1 I D2 1 W K P (VGS VT ) 2 (1 VDS 2 ) 2 L 2 Thus, S. Yan, EE 338L 2 Lecture 7 I OUT I D 2 I REF I D1 W L 2 1 VDS 2 W 1 VDS1 L 1 Note that IOUT is well defined, mainly determined by the geometries of the transistors, and 1 VDS 2 . For simplicity, we assume two transistors have identical size. If two 1 VDS1 transistors have different VDS, the mirroring is not prefect. But usually is small (such as 0.05 V-1), thus the error (say, a few percent) is usually tolerable. We will also study ways to improve the current mirror accuracy. IREF VGS OR VT VT VGS IREF Fig. VGS as a function of IREF in the basic current mirror Note that the correct operation of current does not rely on square law. As low as the I D f (VGS ) is monotonous, the IREF current mirror will work. Thus we also have bipolar transistor current mirror as shown in right figure. S. Yan, EE 338L Iout Q1 3 Q2 Lecture 7 Example: Find the current of M4 if all transistors are in saturation (the geometry ratio of W Mi is ). L i VDD IREF M1 M3 M4 M2 Iout Solution: We have I D 2 I REF W W L 4 L 2 , I D3 I D 2 , and I D 4 I D 3 , W W L 3 L 1 So I D 4 I REF W L 2 W L 1 W W W L 4 L 2 L 4 I REF , where , W W W L 3 L 1 L 3 Proper choice of α and β can give large and small ratios between I D4 and IREF. S. Yan, EE 338L 4 Lecture 7 Example: Calculate the small-signal voltage gain of the circuits shown in right figure. Assume (W/L)3/(W/L)2=α, and all transistors are in saturation. Please ignore λ effect (λ=0). The transconductance of M1 is gm1. VDD M2 Vin M3 Vx Vout M1 RL Solution: The small signal equivalent circuit is vx vin gm1vin gm2vx vout vx vin RL gm3vx OR gm1vin 1 gm2 vout gm3vx RL Node equations g m1vin g m 2 v x 0 (1) g m3 v x vout 0 RL (2) From above equations, we can get Av S. Yan, EE 338L vout g g m1 m3 vin g m2 5 W L 3 RL g m1 RL W L 2 Lecture 7 Current Mirror Error Assume M1 and M2 are in the saturation. IREF ID1 ID2 M1 M2 I D1 1 W K P (VGS VT ) 2 (1 VDS1 ) 2 L 1 I D2 1 W K P (VGS VT ) 2 (1 VDS 2 ) 2 L 2 So, I D2 I D1 W )2 1 VDS 2 L W 1 VDS1 ( )1 L ( Note that VDS1=VGS, thus when VDS2=VGS, the current mirror is “accurate”. Note for small channel transistors, VT of MOSFET changes with transistor size, especially L. To have better mirror accuracy, M1 and M2 should have the same L. W L 2 For current mirror ratio other than 1, multiple unit transistors should be W L 1 used. Each unit transistor has the same W and L. S. Yan, EE 338L 6 Lecture 7 Cascode Current Mirrors To suppress the error introduced by channel length modulation effect, cascode current mirrors can be used. The key idea of cascode current mirror is to match the VDS of two bottom transistors, M1 and M2. VDD IREF VN M0 VGS0 VO VX VGS0+VGS1 M1 VGS1 Cascode current mirror, note that IOUT M3 VGS3=VGS0 VY M2 VDS2=VGS1 (W / L) M 2 (W / L) M 3 (W / L) M 1 (W / L) M 0 Shown in the above Figure, M0 and M1 are diode connected MOS transistors. For M0 and M1, we have VGS0=VDS0, and VGS1=VDS1. The potential at the drain/gate of M1 is VGS1, and the potential at the drain/gate of M0 is VGS1+VGS0, as shown in Fig. 1. Note that if we ignore channel length modulation effect, (W / L) M 2 (W / L) M 3 , we (W / L) M 1 (W / L) M 0 have IOUT=IREF, and VGS3=VGS0, VGS2=VGS1. If we consider channel length modulation effect, 1) if VO=VN, due to the symmetry, IOUT=IREF. 2) if VO changes from VN to a higher value, we have, VO>VN. Note that ID 1 W 2 K p VGS VT (1 VDS ) . If we assume IOUT does not change, 2 L S. Yan, EE 338L 7 Lecture 7 I OUT I D 3 1 W 2 K p VGS 3 VT (1 VDS 3 ) , VDS3 will be larger because VO is higher 2 L compared to the case 1), (1 VDS 3 ) is larger, to keep IOUT unchanged, VGS 3 VT will 2 be smaller, hence VGS3 will be smaller, thus VY (or VDS2) will increase as VN keeps constant. Note that I OUT I D 2 1 W 2 K p VGS 2 VT 2 (1 VDS 2 ) , other terms keep 2 L unchanged, while (1 VDS 2 ) increases, thus IOUT will increase. Note that because VDS2 (=-VGS3) is much smaller than VO, the IOUT of cascode current mirror is much smaller than the IOUT of non-cascode simple current mirror. VO VN M3 gm3vgs3=-gm3vy IOUT i21 i22 vg3=0 vo i23 gds3 VY gmb3vbs3=-gmb3vy vb3=0 vy VX M2 i1 (a) (b) gds2 Output branch of the cascode current mirror From the small signal model as shown in Fig. 2(b), according to KCL, we have i21 i22 i23 i1 (1a) i21 g m 3v y (1b) i22 g ds3 (vo v y ) (1c) i23 g mb3v y (1d) i1 g ds 2 v y (1e) Combine and rearrange the above derivations, we have vy vo g ds3 g m3 g mb3 g ds3 g ds 2 (2) According to the definition of small signal analysis, S. Yan, EE 338L 8 VY VY v y , we have VO VO vo Lecture 7 VY v y g ds3 1 1 VO vo g m3 g mb3 g ds3 g ds 2 g m3 g mb3 1 Ait 1 g ds3 where Ait (3) g m 3 g mb3 , which is the gain of the top transistor. g ds3 Eq. (3) shows that VY is much smaller than VO, or VY 1 VO . Thus VY is very Ait 1 close to VX, even if VO is different from VN. S. Yan, EE 338L 9 Lecture 7 Example: In the following figure, assuming (W / L)M1 (W / L)M 0 , sketch Vx and Vy as a (W / L)M 2 (W / L)M 3 function of IREF. If IREF requires 0.5V to operate as a current source, what is the maximum value of IREF? Note that the VT of M1 and M2 is VT,M1 and the VT of M0 and M3 is VT,M0, the transconductance coefficient of M1 and M2 is KP. Solution: When VN reaches its maximum value, IREF reaches its maximum value. Since M2 and M3 are properly ratioed with respect to M1 and M0, we have VY=VX≈ 2 I REF VTH 1 . K P (W / L)1 The behavior is plotted in the figure b. We note that V N VGS 0 VGS1 2 I REF L L VTH 0 VTH 1 K P W 0 W 1 Thus, VN ,max 2 I REF ,max L L VTH 0 VTH 1 VDD 0.5V K P W 0 W 1 and hence I REF ,max K P (VDD 0.5V VTH 0 VTH 1 ) 2 2 2 L L W 0 W 1 S. Yan, EE 338L 10 Lecture 7 Low Voltage Cascode Current Mirrors Previously discussed current mirrors have relatively large voltage drop. VDD IOUT IREF M0 VGS0 2VGS 2VT+2Vdsat M1 VGS1 M3 M2 Vdrop,min =VGS2+Vdsat3 VT+2Vdsat VDS2 VDS1 =VGS1=VGS2 The left side has a voltage drop of 2VGS (note that in reality, VGS1 and VGS0 are not necessarily equal). The right side has a minimum voltage drop of VGS2+Vdsat3. Otherwise, M3 will enter triode region. One way to reduce the voltage headroom requirement is shown in the following: 1) Remove M0 in the above figure. 2) Bias the gate terminal of M3 with a bias voltage Vcas, which is chosen to keep M2 and M3 in saturation with minimum voltage headroom requirement at the output terminal. VDD IOUT What is the value of Vcas in the right figure? IREF Vcas = VDS2+VGS3=Vdsat2+VGAP+VGS3 VCAS M3 Note that in above figure, M1 and M2 have different VDS values, VDS1=VGS1, while, VDS2=Vdsat+VGAP, where VGAP is the voltage safe margin to keep M2 in saturation. Thus, M1 M2 I OUT (W / L) 2 1 VDS 2 I REF (W / L)1 1 VDS1 S. Yan, EE 338L 11 Lecture 7 The term 1 VDS 2 is not unity, as VDS1 VDS 2 . Thus large current ratio error will result. 1 VDS1 How to solve the VDS mismatch problem? VDD IOUT1 IREF IOUT2 IOUTn VCAS M0 M1 M3 M5 M2 M4 M2n+1 M2n Key features: 1) Input voltage drop: VGS (half of the input voltage drop of the folded cascode current mirror in previous page) 2) Minimum output voltage: 2Vdsat+VGAP, where Vdsat is VGS-VT, and VGAP is VDS-Vdsat of bottom transistors. 3) Output resistance: Rout [1 ( g m 2n1 g mb2 n1 )ro 2 n1 ]ro 2n ro 2 n1 ( g m 2 n1 g mb2n1 )ro 2 n1ro 2n where n=1,2,3… 4) Very WIDELY used in modern analog integrated circuits. Must be grasped firmly! How to generate VCAS (1) Use additional current source and transistor S. Yan, EE 338L 12 Lecture 7 VDD VDD IREF IREF IOUT MCAS M0 M3 M1 M2 VGS,MCAS = VT+Vdsat0+Vdsat1+VGAP. Example: If (W/L)0=(W/L)1=(W/L)2=(W/L)3=(W/L)T, and VGAP=0, what is the (W/L) of MCAS? Solution: Since (W/L)0=(W/L)1=(W/L)2=(W/L)3=(W/L)T, if we ignore the channel length modulation and body effect, we have VGS0 = VGS1= VGS2= VGS3= VGS, Thus Vdsat0= Vdsat1= Vdsat2= Vdsat3= Vdsat VGS,MCAS = VT+Vdsat0+Vdsat1+VGAP= VT+2Vdsat 1 1 W W K P (VGS ,MCAS VT ) 2 I REF K P (VGS VT ) 2 2 L CAS 2 L T W W 2 So (2Vdsat ) 2 Vdsat L CAS L T 1 W W L CAS 4 L T 1 Example: If (W/L)0=(W/L)1=(W/L)2=(W/L)3=(W/L)T, and VGAP= VdsatT, VdsatT is the Vdsat 2 of M0 to M3, what is the (W/L) of MCAS? S. Yan, EE 338L 13 Lecture 7 Solution: VGS,MCAS = VT+Vdsat0+Vdsat1+VGAP= VT+2.5VdsatT 1 1 W W K P (VGS ,MCAS VT ) 2 I REF K P (VGS VT ) 2 2 L CAS 2 L T W W 2 So (2.5VdsatT )2 VdsatT L CAS L T 1 W W L CAS 6.25 L T (2) Use additional current source, transistors and resistor VDD VDD IREF IREF IOUT Rb 2VGS MC0 M0 M3 M1 M2 VCAS MC1 VCAS 2VGS I REF Rb If we choose Rb to have a voltage drop on Rb as VT-VGAP, we have VCAS 2VGS (VT VGAP ) VGS Vdsat VGAP Thus, Rb should be Rb VT VGAP I REF Example: In above figure, all transistors have a (W/L) of 16, K PN=100uA/V2, VTN=0.7V, IREF=50uA, what is the value of Rb to yield a VGAP of 180 mV? (Assume square law applies, and 0 ) S. Yan, EE 338L 14 Lecture 7 Solution: Rb VTN VGAP 0.7V 0.18V 10.4 K I REF 50uA (3) Use one additional resistor VDD IREF IOUT Rb M1 VCAS M0 M3 M2 Note that VCAS should be VCAS= VT+2Vdsat+VGAP=VGS+Vdsat+VGAP= VGS+ VRb Thus the voltage drop on Rb is VRb= Vdsat+VGAP=IREFRb We have Rb Vdsat VGAP I REF Example: In above figure, all transistors have a (W/L) of 16, K PN=100uA/V2, VTN=0.7V, IREF=50uA, what is the value of Rb to yield a VGAP of 180 mV? (Assume square law applies, and 0 ) Solution: S. Yan, EE 338L 15 Lecture 7 2 I REF 2 50uA 0.25V 100uA / V 2 16 W K PN L Vdsat So Rb Vdsat VGAP 0.25V 0.18V 8.6K I REF 50uA Iin Current mirrors that process signals Iout Current mirrors could be used in circuitry that provides the DC bias current to the active circuits. They can also be actively involved in processing the signal. In M1 M2 the textbook, these current mirrors are called active current mirrors. S. Yan, EE 338L 16 Lecture 7