* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download EE316_5

Josephson voltage standard wikipedia , lookup

Radio transmitter design wikipedia , lookup

Power MOSFET wikipedia , lookup

Oscilloscope history wikipedia , lookup

Index of electronics articles wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Surge protector wikipedia , lookup

Phase-locked loop wikipedia , lookup

Regenerative circuit wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Two-port network wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Voltage regulator wikipedia , lookup

Negative feedback wikipedia , lookup

Power electronics wikipedia , lookup

Wien bridge oscillator wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Valve audio amplifier technical specification wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Negative-feedback amplifier wikipedia , lookup

Integrating ADC wikipedia , lookup

Wilson current mirror wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Current mirror wikipedia , lookup

Schmitt trigger wikipedia , lookup

Opto-isolator wikipedia , lookup

Valve RF amplifier wikipedia , lookup

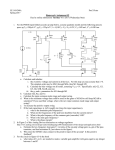

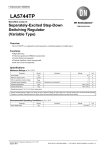

Non-ideal behaviour of op-amps: Input bias and offset current Op-amps sink or source a small current at each input –these are the bias currents for the transistors within the op-amp. Op-amps require a series dc path through which currents can flow. The bias currents are never actually matched as the two input stages of the op-amp are in general mismatched. So we model both input bias currents as follows: In Ideal Op-amp Vn IB IOS /2 Ip Vp Define: IB Vo IB I p In 2 and I OS I p I n IOS is the input offset current. Usually IOS < 0.1 IB The polarity of IB is determined by the type of the input transistor. For npn BJT and p-channel JFETs, the input currents and hence IB are positive. For pnp BJT and n-channel JFETs, the input currents and hence IB are negative The polarity of IOS is determined by the direction of the mismatch. IB and IOS produce errors Negative Feedback does not reduce these We measure IB and IOS by seeing what is the output for zero (signal) input Then, non-inverting and inverting amplifiers are the same R2 R1 Rp In Ip Eo 0V R E o 1 2 R1 / / R2 I n R p I p R1 An (unwanted) input is amplified by a gain “noise” “noise gain” R Noise gain 1 2 R1 Same for both inverting and non-inverting configurations! Obvious effect on signal to noise ratio at output! (Remember superposition) Effect on an Integrator (with zero I/P signal) C R Rp In Ip t Rp 1 Eo I n I p dt E o (0) C 0 R t 1 I OS dt E o (0) when R p R C0 Eo How to reduce effects of IB and IOS? Choose devices with low IB and IOS Superbeta BJTs – Superbeta BJTs have very thin base regions and hence the recombination component of the base current is reduced. IB Cancellation methods – special circuitry is used to provide the bias currents and thus cancel the bias currents required from outside the device. FET input op-amps – have low bias currents Choose Rp = R1 // R2 , then R E o 1 2 R1 / / R2 I OS R1 Temperature effects on IB and IOS : For BJTs, the temperature effects are often negligible for normal temp ranges For FET types, IB doubles every 10C Op-amps with very low IB require guarding to counteract PCB surface leakage currents. CF R2 2 R1 3 2 3 Vi Vo Rp CF R2 R1 2 3 Rp Vi Vo Input Offset Voltage When the inputs of the op-amp are shorted together, we should get zero OutPut We don’t ( due to mismatches / manufacturing tolerances) We model this with an input offset voltage (the voltage shift required at the input to correct the VTC) Vo [V] VSATH Vd [V] VOS Voltage Transfer Char. (VTC) VSATL Ideal Op-amp Vn Vd VOS Vp Vo Now require Vd Vp VOS Vn 0 Vp Vn VOS Errors due to VOS (Inverting or non-inverting configurations.) R2 R1 VOS R E o 1 2 VOS R1 Eo dc “noise” with noise gain Error in Integrator circuit C R VOS t 1 Eo VOS dt E o ( 0) RC 0 Eo Combination of Input offset voltage and input bias currents Example – inverting amplifier Practical Op-amp R2 In Vn Ideal Op-amp R1 IB Ip Vp vo vi IOS /2 Rp Vo IB (a) (b) Fig Q6 Equivalent circuit: R1//R2 In R1 Eo R1 R2 Rp Ip VOS 0V Eo V V R1 Eo R1 //R2 I n R p I p VOS R1 R2 R R EO 1 2 VOS R1 // R2 I n R p I p 1 2 VOS R p I OS R1 R1 since Rp = R1 //R2 Temperature effects Mismatch can get worse as T changes VOS (Average) temperature coefficient of VOS , T usually in VC1 quoted at “room temp” 25C VOS VOS ( T ) VOS ( 25 C ) ( T 25) T VOS Devices with low VOS also have low T Power Supply Rejection Ratio (PSRR) Changes in supply voltage(s) affect biassing and hence VOS Defined as: VOS PSRR = V supply specified in VV1 i.e. PSRR or dB = 20 log 10 VOS Vsupply dB with Vsupply = 1V Common-Mode Rejection Ratio (CMRR) important in Non-Inverting or Differential configurations. Common-mode voltage affects VOS Example (Non-Inverting configuration) R2 R1 VOS Vo Vi Normally: Vd V p Vn 0 V p Vn But the fact that Vp = Vi means that both I/Ps are at a potential other than zero and this affects the bias conditions and hence VOS Define the Common-mode voltage as: VCM V p Vn 2 Vi then CMRR VOS VCM i.e. CMRR = 20 log 10 specified in VV1 or dB VOS dB with VCM = 1V VCM Offset Error Compensation By superposition, the combined effect of IOS and VOS is: R E o 1 2 VOS R1 / / R2 I OS R1 (Since polarity of both is uncertain must consider the worst case – hence we use the absolute values) Some op-amps have pins for “internal” offset nulling (correction) In other cases, an adjustable dc voltage is injected to compensate for the existing offset error (as detected by instruments) In circuits with more than one op-amp, it is (generally) sufficient to null the overall error by adjustment of just one device. (Superposition) Frequency Response a ( jf ) ao where ao is the dc open loop gain f 1 j fa fa is the open-loop corner (or break, or 3dB, or cut-off) frequency. In this case, it is also the openloop BANDWIDTH. With negative feedback (Non-Inverting configuration) V Vi Vfb As before: R1 b R1 R 2 Closed-loop gain is: A( jf ) Ao f 1 j fA a(jf) b Vo ao 1 1 1 aob b 1 1 aob f A f a (1 aob ) Ao fA is the closed-loop corner (or break, or 3dB, or cut-off) frequency. In this case, it is also the closed-loop BANDWIDTH. a 20 log10 ao ab A 20 log10 Ao f fa Still 1st order Since f t ao f a and fA ft Ao 1 b f A f a a0 f a b f a bf t bf t Hence , Ao f A f t Constant gain-bandwidth product (GBP) This is an important specification of an op-amp For the Inverting configuration, there is a reduction in Ao and fA (and GBP) Remember: Vi V b 1 Fictitious point in circuit Vfb Closed Loop Gain , A( jf ) b 1 Ao 1 R 1 2 b R1 a(jf) b a ( jf ) 1 a ( jf )b Vo fA R1 ft R1 R2 GBP R2 ft R1 R2 f t a0 f a Input and output impedances are also affected by frequency For example: For Non-Inverting configuration, Zin decreases and Zo increases. Time-domain considerations Since an op-amp behaves as a 1st order system in both open- or closed loop connection, then the transient (step) response has a non-zero RISETIME If we define the rise-time tr as the time to go from 10% to 90% of final value, then we can show 0.35 tr ft Important relation between time-domain and frequency-domain specification So far we have confined ourselves to our standard model that assumes linear behaviour and therefore assumes small signals. For large step amplitudes, the device operates in non-linear mode and the slope of the time response “saturates” at a max value known as the SLEW RATE the maximum rate at which the output can change dV (t ) SR o dt max