* Your assessment is very important for improving the workof artificial intelligence, which forms the content of this project

Download 32_Channel_Pres1

Survey

Document related concepts

Buck converter wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Dynamic range compression wikipedia , lookup

Flip-flop (electronics) wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Integrated circuit wikipedia , lookup

Oscilloscope wikipedia , lookup

Immunity-aware programming wikipedia , lookup

Rectiverter wikipedia , lookup

Schmitt trigger wikipedia , lookup

Oscilloscope history wikipedia , lookup

Time-to-digital converter wikipedia , lookup

Transcript

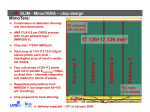

The designers of the Bari chip A.G.Argenteri, F.Corsi, M. Foresta, F.Marzocca, G.Matarrese [ Polytecncio di Bari ] The old guard in Bld. 28 E.Chesi, J.Seguinot, A.Rudge, P.Weilhammer For the Ax-Pet Collaboration The 8 channel Bari chip The 8 channel chip has been used at CERN for the readout of the LYSO/MPPC with photomultiplier assembly in Jacques’s lab. The following results were obtained. The histogram of the 22 Na peak in coincidence with the p.m. with a chip threshold of 450 Kev. The FWHM resolution is 11.5% (no correction) The multiplexer output for 2 simultaneous hits on channel 1 and channel 6 Ref. 2009 IEEE NSSMIC Coincidence Timing of 4.5ns between the Fast_OR and the p.m. was measured to be 4.5ns FWHM.(high threshold. not a limit) whereas pulse generator timing was 170 ps. do not be fooled. The first 3 bits 101 are the preamble The next 3 give the address in this case 011, and the next are data 00110101. The 32 channel Bari chip This 32 channel chip was the precursor of the new 32 channel chip. It was tested at CERN in September 2010 . This photo shows the p.c.board with two 32 channel chips, and the p.c. board with the dedicated FPGA readout into the USB port Enrico interfaced the USB output into the CERN readout system , and was able to take pedestal runs and data from Jacques’s setup of with an internal trigger from the LYSO radioactivity and a 22Na source. Ref. Front end Electronics for silicon Photo-Multipliers Coupled to fast Scintillators F.Corsi et al. Overall block diagram of the new 32 channel chip and readout system Single Bias Supply MPPCs 512K Byte RAM [ 4M Byte] 32 Ch. Chip FPGA P.C USB ADC The fine bias adjustment per channel is incorporated in the chip. The internal ADC is non functional therefor an external ADC is used. All operations are controlled by a Cyclone II FPGA, the data being buffered into external RAM. Many thousand events may be stored and then transferred to the P.C. thus avoiding the USB overhead. This system was used for the readout of the 8 channel chip. Data formats are yet to be agreed. The unchanging front end of the Bari chip Structure of the analog channel From configuration register To analog multiplexer To current sum and threshold circuits From configuration register From internal logic Or external pins To fast OR Much of the above is controlled by the config. register. The bias adjustment- 8bits The Charge Sensitive Amplifier gain and shaping time- 3 + 3 bits. Trigger source and type ie. Voltage or current- 4 bits The bias and threshold of the current trigger comparator- 10 +4 bits The threshold of the voltage comparator 4bits Channel masking- 32 bits CONFIGURATION OF THE CHIP The 524 configuration bits enter the configuration register in this order: Q[523:514] dac_idc[9:0] Q[505:503] gate[2:0] Q[502] sel_tr_int sel_tr_int=0-> sel_tr_int=1-> DAC used to compensate the DC current at the input of the current discriminator. setting for time window A; selection of the source of the internal trigger: OR of the voltage comparators (signal “or_comp”); current discriminator (signal “discr”) Channel configuration bits There now follows 448 bits configuring all 32 channels. Channel 0 Q[500:493] Vbias_ch_0[7:0] tuning of the detector bias (internal DAC) Q[492:490] gain_ch_0[2:0] gain of the CSA (1÷6) Q[489:487] sha_ch_0[2:0] shaping time of the CSA (1÷6)) End of channel configuration bits Q[52] ex_let Q[51] Ser_Spa Q[50] ADC_ext Q[49:46] Q[45:42] Q[41:10] Q[8] tr external (ex_let=1) or internal (ex_let=0) read-out serial (Ser_Spa =1) or sparse (Ser_Spa =0) read-out external (ADC_ext=1 or only internal (ADC_ext=0) ADC threshold[3:0] threshold of the current discriminator delay_pd[3:0] setting for time window B en_ch[31:0] channel masking (en_ch[i]=1 channel use internal(tr=0) or external (tr=1) trigger Q[7:0] V_treshold[7:0] threshold of the voltage discriminators The first configuration bit to be applied to the SDI input and shifted into the chip is Q[523], the last one is Q[0]. The chip configuration is complex involving 3 internal registers. Interface, Configuration and Local. The control pads are SSN, SDI and SDO the output pad. All controlled by the system clock. The apparent complexity greatly simplifies the chip design. Structure of the peak detector. The circuit combines that of a track and hold, with that of a peak detector The peak detector has three different modes of operation, depending on the values of “test_pd_n” and “hold” digital signals. A) Normally, “test_pd_n” is high and “hold” is low: the circuit behaves like a follower, and the input voltage (output of the CSA) is repeated on capacitor C_peak; the output line is floating. B) With “hold” low, “test_pd_n” goes low: the circuit becomes a peak detector and the peak of the input voltage is stored on C_peak; the output line is floating. C) With “test_pd_n” low, “hold” goes high: the circuit becomes a buffer of the voltage stored on the capacitor C_peak, which is repeated on capacitor C_hold and transferred on the output line. Hold and test_pd are available as external inputs clock SRQ Trigger acq. trigger Coinc. Time window A Internal trigger. coinc. is high. Time window B CSA hold Multiplexer out Two hits are read out, total readout time is 400ns with a 20MHz clock Address stable bfc reset SETTING OF THE TIME WINDOW A TWA has been previously set in config. bits Q[505:503] The TWA starts when the selected source of the internal trigger fires. When TWA ends, the trigger register is frozen and no more channels can be added to the list of the ones to be read-out. (can be 25ns). a) Internal read-out with internal trigger When the trigger source is internal (i.e. tr=0), the first falling edge of the master clock following the activation of the internal trigger enables a counter: this counter is increased at each following clock edge (both rising and falling). As soon as the number of counted clock edges is equal to the content of gate[2:0], no more triggers are accepted, i.e. TWA is closed. Thus, in this case, the clock can be sent to the chip after an internal trigger is detected, since this event is identified by the signal on the SRQ pad which goes active (low). Any delay in sending the first falling edge of the clock after the activation of the internal trigger contributes to the duration of TWA. clock SRQ Trigger acq. Trigger Coinc. Coincidence trigger Time window A Time window B CSA hold Multiplexer out Address stable bfc reset Time Window B has a double function: TWB has been previously set in config. bits [45:42] a) First, the read-out operation goes on only if a pulse is put on the "coinc" external pad during TWB. If TWB expires and no coincidence pulse arrives, an internal reset signal is generated to both the internal logic and to the peak detectors (by means of the internal "lch_rst" signal). Otherwise, if a coincidence pulse is put on the "coinc" pad during TWB, the read-out procedure goes on. Thus, TWB works as a window to wait for a coincidence signal. b) Second, the other function of TWB is to give time to the CSA output and to the PD's to reach their peak: as soon as TWB expires, the "hold" signal is generated. The counter is increased at every rising edge of the master clock after the trigger. At the end of the counting, TWB is closed and the "hold" signal is generated. The read-out starts, i.e. the multiplexing of the above threshold channels starts. The peak detector (which now work as analog memories storing the peak of the CSA outputs) of the channels with the respective trigger bit activated are multiplexed and sent, one at each master clock cycle, to the output analog pad (ADC_ext=1). Start-of-conversion and end-of-conversion bits internally generated manage the multiplexing and the conversion of the channels, synchronously with the master clock. clock SRQ Trigger acq. trigger Coinc. No coincidence signal received total time 200ns. Time window A Time window B CSA reset The number of counted clock edges matches the content of TWB and no external trigger is sent. In this case we are not interested to read-out the event which caused the internal trigger, so an internal reset is sent to the peak detectors and to the logic, to restore the initial situation. Then, the chip waits for another event. Rates and readout times Count rate v. activity (see notes) 0.8 Count rate in Mhz 150 ns dead time 0.6 Trigger on Photopeak 0.4 1us dead time 0.2 Trigger on sum 0.0 0 20 40 60 80 100 120 Activity in MBq The above shows rates in a single module of 8*6 crystals 15cm long with a point source in the center between 2 modules spaced 15cm apart. The 1us dead time curve assumes a trigger threshold on individual crystals of 450 Kev, a 20MHz clock and an average word count of 6 words. The trigger on the sum curve assumes a trigger similar to the Ax-Pet system to include Compton events. Ongoing module development with Bari Present status and the immediate future p.c.b for chip p.c.b to interface to FPGA which Includes 2 ADCs and NIM-TTL and TTL-NIM converters. Bari have provided me with 3 new chips. The chip p.c.b. is (hopefully) already at CERN and will be got working next week. The first task will be the configuration registers and then the current sum output. I hope to receive the interface p.c.b. in about 2 weeks, and to proceed with the analog multiplexer output, managing the ADC timing and then the digital readout. Conclusions The new Bari chip promises an increase in readout speed of more than an order of magnitude, and several orders of magnitude in miniaturization. To prove this, construction is under way to produce a new module(s) to also be MRI compatible. We will continue the two pronged approach with Bari where we both work in parallel in proving and understanding the chip and associated readout system. For example coincidence measurements and WLS readout are easier using Jacques’s apparatus here at CERN. The existing practice of our visits to Bari, and their visits here will continue. Bari expects to be able to make another chip submission using the same CMOS 0.35 um process in the future to correct the now understood ADC problem. Other groups at Bari are working with the deep sub-micron process and have found a low cost foundry in Germany. Block data transfer formats have to be agreed between the experts (Viviana), Bari and ourselvs A discussion within the collaboration is required regarding photoelectric only, or including Compton events if only for chip design and readout considerations.