* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Common-Mode Feedback Circuits

Control theory wikipedia , lookup

Power inverter wikipedia , lookup

Three-phase electric power wikipedia , lookup

Signal-flow graph wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Transmission line loudspeaker wikipedia , lookup

Integrated circuit wikipedia , lookup

Power electronics wikipedia , lookup

Electronic engineering wikipedia , lookup

Buck converter wikipedia , lookup

Control system wikipedia , lookup

Two-port network wikipedia , lookup

Current source wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Negative feedback wikipedia , lookup

Regenerative circuit wikipedia , lookup

Current mirror wikipedia , lookup

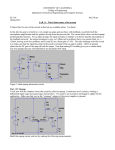

Analog Electronics — 9 • Example: If v on is picked to be 0.2 V, V DS set to V on + 0.2V = 0.4V , V TN = 0.8V , V TP = – 0.9 V , power supply rails at 3.0 V, (bias voltages shown below) then swing from about 0.6 V to 2.4 V. 3V ∆i = g m v d ⁄ 2 2I I –∆ i 1.9V I –∆ i 1.5V gm vd 1.4V 1.5V 2I 1V 2∆i + gm CL I + ∆i 1.4V I –∆ i 1V I –∆ i gm vd 1.5V 0.5V 0V 1.5V - vo I + ∆i 0V single stage (output current is directly g m v d ) high frequency capability • vo gain = ----- = g m R o , typical gain about 1000 or 60 vd dB. R o is high due to cascodes • Dominant pole, UGBW is set by load capacitance thus larger load results in more stability • Set current by desired slew rate and known capacitor load. 2∆i vo CL I –∆ i 1V I –∆ i • I + ∆i 0.4V vd gm vd 1.5V - 1.9V 1.5V I + ∆i I + ∆i 3V 2I 1.9V I + ∆i + 2I 2I 2I Common-Mode Feedback Circuits • • Circuit and feedback often define difference mode Common mode can drift, potentially putting circuit into bad region of operation • Need common-mode correction circuit to provide low A c , with minimal reduction of A d • Can sum outputs to obtain v oc . If this is not zero, feed back a correcting signal. If output is purely differential, v op = – v on and the sum will be zero. An example below uses resistors for summing Opamp Design: C. Plett Analog Electronics — 10 Example of Common-Mode Feedback Circuit for Folded-Cascode Amplifier v bias v op M4 M5 v bias v on R bias von + vop vin - R v ref vc CL M3 M 11 M 10 • Capacitor C across resistor R improves highfrequency performance • Operation: • summing: use resistors, switched capacitors, transistors in linear region, or differential pair. • resistors across output, or SC can reduce DC gain, however, equivalent R can be very high. - If both outputs are high, v c will go high with respect to v ref . • - Note: feedback of the appropriate polarity could instead be fed back to M 3 or to M 10 and M 11 . v bias will also go high, since the extra amplifier is non-inverting • Things to watch out for: - M 4 and M 5 will have their current reduced - The output voltage will be reduced (overall negative feedback) Stability of CM loop (Tests open loop, or with common-mode step) - If summing with SC, restricted to timedomain simulations (or replace with R eq ) - linearity of sum for large diff voltage Opamp Design: C. Plett Analog Electronics — 11 Two-stage opamp with pole splitting compensation M4 M5 M1 v1 v2 x Cc CL I3 VB v1 M1 x M2 vi Cc v2 vz Rz gmivi M6 vo Cc CL vz M4 M7 M3 Small Signal Model M7 IB M6 vo M2 M3 VB vz Cz gmovz Ro CL M5 vo ω p2 ω p2 (– s + z) Transfer function: ----- ≈ A o -------------------- ----------------------------------------------vi z ( s + ω p1 ) ( s + ω p2 ) vo vo vz Low Freq. gain: ----- = ----- ⋅ ---- = A o = g mo R o ⋅ g mi R z vi vz vi g mi UGBW = -------- , Slew Rate = Cc I3 ------ , Cc Stability • g mo next pole: ω p2 ≈ – --------CL A normal (LHP) zero would add phase lead to improve stability, but RHP zero adds phase lag which reduces stability (45o at ω z ). • g mo RHP zero: ω z ≈ --------Cc Increased load capacitance reduces stability since p 2 moves to lower frequency. • p 2 and z must be beyond UGBW enough so total 1 dominant pole: ω p1 ≈ – -----------------------------R z g mo R o C c Where: v i = ( v 1 – v 2 ) , g mo = g m6 , g mi = g m1 = g m2 , R z = r o2 || r o5 , R o = r o6 || r o7 , C z = parasitic (small) , C L = load capacitance phase shift due to p 2 and z < 45° . Rules of thumb: Gregorian and Temes p 2 = z = 3 UGBW → 53° phase margin Allen and Holberg z = 10 UGBW , p 2 = 2.2 UGBW → 60° phase margin Opamp Design: C. Plett Analog Electronics — 12 Additions to Pole Splitting, Offsets, Gain Errors, Buffers Calculation of Gain Error The zero in the RHP can result in instability. Can remove, or compensate for with the following techniques: 1. Buffer, typically source follower, to allow feedback only (removing feed forward) source follower vo vz Cc Vbias current source This removes the zero, and the system is left with two poles. These should be separated by the DC gain, or more for stability. vi + + - A B Cc Rc vo 1 Closed loop gain is --- in dB B Buffers 1 adds ω p3 = – ------------- , changes Rc C c vin Level Shift 1 ω z to ω z = ---------------------------------- , this allows one to move 1 --------– R c C c g m6 (or vin) Source Followers ω z → ∞ , or bring it into the LHP where it can cancel out ω p2 approximately • Offsets + Vo,off Output referred Valid for high A. 1 1 Here, desired gain ≈ --- , Gain error ------B AB where AB = loop gain → Open loop gain in dB, 2. Series Resistance vz vo 1⁄B 1 1 ----- = ----------------------------- ≈ --- 1 – ------- 1 + 1 ⁄ ( AB ) B vi AB vo + Vi,off - + Input referred V o, off V i, off = ---------------A Level Shifts vi vo Drain Outputs Source output has low inpedance, limited swing, can only get within V T from the rails, (assuming v in can go all the way to the rails). For gain A , 0V vo • Drain output is a current output, i.e., higher impedance compared to source output, but good swing, can get essentially all the way to the rails. Opamp Design: C. Plett Analog Electronics — 13 Layout and Cross Sections of CMOS Transistors (Source - Substrate Connected) VIN VSS VDD schematic VOUT VIN VDD VSS top view n+ mask NMOS B S p+ n+ VOUT p+ mask G n+ cross section PMOS G D D S p+ p+ B n+ n- well p- substrate Opamp Design: C. Plett Analog Electronics — 14 Other Components Resistors L T L L - = R ⋅ ---L = ρ -------R = ρ --S WTW A W • ρ design information documents often give R S , the sheet resistance in ohms per square R S = --- . e.g., if T 60µ 100Ω ⁄ then R = 100 × --------- = 600Ω which we see as 6 squares 10µ 60µ 10µ • a typical resistor: - 1 in counting total length, corner square is about 0.5 square. Result 57 • 5 Absolute tolerance: - ≈ ± 20% for wide resistors > 10 µm ± 30% for W = 5µm • → 1 1 1 3 matching: W = 5µ ± 3 % , W = 10µ ± 1.2 % , W = 25µ ± 0.8 % , W = 50µ ± 0.2 % Opamp Design: C. Plett Analog Electronics — 15 Capacitors • • Transistors Parallel plates of Area A, capacitance per area Co • ε R εo ε C = C o A where C ox = ------- = ----------- . t ox t ox Often W/L >> 1, so can use multiple contacts for minimal source or drain series resistance • Diagram same for p or n. If PMOS, then in n-well with p+ mask, NMOS in p-substrate with n+. • can have multiple stripes. This can reduce total drain or source area to minimize capacitance. • two gate poly stripes, could be common source, e.g., diff pair, or common connection or since we often cannot tell source and drain apart, it might be a series circuit (for Nand, or cascode). if t ox = 0.017µm , ε R for SiO2 is 3.9 then – 12 fF 3.9 × 8.854 ×10 ( F ⁄ m ) C ox = -------------------------------------------------------------- ≈ 2 ---------------- example: –6 2 0.017 ×10 ( m ) ( µm ) transistor estimate C gs ≈ 2--- C ox WL , with W ----- = 150µ -----------L 1µ 3 2 has C gs = ( 2 ⁄ 3 ) × 150 × 2 ( fF ⁄ µm ) = 0.2 pF . • • • capacitors can be metal-metal (MIM), poly-poly or poly-diffusion. (poly-poly shown below) L typically design as multiples of a unit capacitor for best matching, e.g., unit could be 0.5 pF, then could get accurate 1.5 pF match to 2.5 pF. D1 D2 D G S D ly de oxi ap po c D1 G1 S G2 D2 metal y pla top te contacts W Otherwise, need to keep area to perimeter ratio the same. pol poly S W/L or G S G G1 G2 W/L S D or Opamp Design: C. Plett Analog Electronics — 16 Transistor layout: G1 D1 G1 D2 G2 D2 G2 D2 G2 Drain connections are not all shown. These missing connections are shown dashed on the schematic below G1 S D1 D1 S D1 S D2 D1 G1 D1 G1 D2 4(W/L) G2 D2 2(W/L) G1 G2 G2 S S Differential Pair • can minimize drain area and perimeter of diff pair to minimize capacitance. • In an opamp, the second (parasitic) pole may be at the drain, so minimum capacitance here can help to increase freq response. S Common Centroid Differential Pair • Can interleave two transistors, as in the example above, where there are a total of eight transistors of which four form M1 and four form M2. • This minimizes the effect of process variations and temperature variations across the chip, thus resulting in better matching, and lower offset. This is called the common-centroid topology. • Note: the same interleaving technique can be used for two resistors which need to be matched. Opamp Design: C. Plett