* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download E6-12 - Stanford University

Electronic engineering wikipedia , lookup

Electrical ballast wikipedia , lookup

Stray voltage wikipedia , lookup

Signal-flow graph wikipedia , lookup

Dynamic range compression wikipedia , lookup

Variable-frequency drive wikipedia , lookup

Voltage optimisation wikipedia , lookup

Mains electricity wikipedia , lookup

Pulse-width modulation wikipedia , lookup

Current source wikipedia , lookup

Analog-to-digital converter wikipedia , lookup

Voltage regulator wikipedia , lookup

Potentiometer wikipedia , lookup

Power inverter wikipedia , lookup

Regenerative circuit wikipedia , lookup

Power MOSFET wikipedia , lookup

Power electronics wikipedia , lookup

Buck converter wikipedia , lookup

Two-port network wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Oscilloscope history wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Schmitt trigger wikipedia , lookup

Current mirror wikipedia , lookup

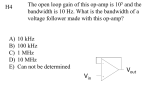

Department of Physics, Stanford University Physics 105, Intermediate Laboratory Seminar: Analog Electronics Lab 6.12 Page 1 Lab 6: Differential Amplifier, JFET’s Read: Day 1: Meyer Section 5.2.4, 5.4.4, 5.4.5 Day 2: Meyer Section 5.5 (all) PRELAB Part 2.1: For the differential amplifier in Figure 1, calculate the following: Differential Gain, Gdiff (express as a ratio, and in dB) Common Mode Gain, Gcm “ CMRR (Common Mode Rejection Ratio), Gdiff/Gcm “ Quiescent voltage at point “A” VB, Quiescent for both transistors IC, Quiescent for both transistors VOUT, Quiescent Part 2.6: Calculate the output of the current source in Fig 3. Remember that the output is sinking current. Part 3: For the variable resistor JFET circuit in Figure 2, check if the 100k potentiometer can adjust the gate voltage (VGS) from 0 volts all the way to the pinch off, or threshold, voltage VP (VGS (OFF) on the datasheet). Use the datasheet for the 2N5485 JFET in Coursework. Make sure you account for the entire range of variability in VP. If the entire range is not available, resize the 330k potentiometer (a potentiometer is the resistor with an arrow pointing at it, and is just a voltage divider). Note on terminology: VP = pinch off voltage, the voltage at which a depletion mode JFET stops conducting. VT = threshold voltage, the voltage at which an enhancement mode MOSFET starts conducting. The two terms are sometimes used interchangeably Department of Physics, Stanford University Physics 105, Intermediate Laboratory Seminar: Analog Electronics Lab 6.12 Page 2 LAB: 1st Day: Part 1. Push Pull Follower: (20 pts) Vcc (+15V) Make sure you understand why it’s a follower that requires no DC bias, and why it’s called a “push-pull”. Note on transistor pinout; the 2N3904(npn) and 2N3906(pnp) have the same pinout: EBC from LR. See 2N3904 spec sheet on Coursework. If you melt things immediately, you probably got the pinout wrong. Welcome to the club. 1. 2. 3. 4. In Build the circuit of Fig 1 and test it with a 1V peak sine wave. Submit a waveform plot showing crossover distortion (input and output waveforms). See Fig 5.39 in Meyer for an example. Explain the crossover distortion Explain why DC offset is not needed at the base. Change the function generator offset from zero to +1V. Show the output waveform and explain what’s going on. Out 470* 1k *only if needed for parasitic oscillations Vee (-15V) Figure 1 Part 2: Differential Amplifier (40 pts) (express gains as both a ratio and in dB; show prelab calculations where applicable) Vcc (+15V) 7.5k Vout 1. 2. 3. 4. 5. Build the circuit of Figure 2. Important: use 1% precision resistors Vin (1) for the matched emitter resistors RE . Measure quiescent voltages and compare w/ prelab Measure differential gain—connect a sine wave to Vin(1)--and compare w/ prelab. Specify the input amplitude you use. (no waveform plots required—just present input and output AC amplitude data). Switch the input – connect the sine wave to Vin(2). Explain the difference at the output compared to #2, above. Connect the same sine wave simultaneously to both inputs. Measure common mode gain and compare w/ prelab Calculate CMRR and compare w/ prelab. 1uF 1uF 100 Vin (2) 100 A 10k 10k 7.5k Vee (-15V) Figure 2 Department of Physics, Stanford University Physics 105, Intermediate Laboratory Seminar: Analog Electronics Lab 6.12 Page 3 Out 6. 7. 8. Build the current source shown in Fig 3 and use it to replace the large 7.5k resistor in the “tail”. Measure common-mode gain again and report the CMRR. Estimate output impedance of the current source based on your data from #6. Should be a high number. What is the function of the 10k resistor on each base? LAB: 2nd Day 12k 2N3904 2.7k Figure 3 1k PART 3.1 (10 pts) -15V Note: use a 2N5485 JFET for all of Part 3 of the lab. The spec sheet for this transistor is on Coursework under Materials/Datasheets. The JFET is physically symmetric, with the Drain and Source being interchangeable. +15V A Build the circuit of Fig 4a. Note where to place an ammeter and a voltmeter. a. D G 10k Measure IDSS and VP. Compare with spec sheet ranges for these parameters. S 0.01uF V 20k -15V Figure 4a PART 3.2 (25 pts) Vin Rebuild your circuit per figure 4b. To operate the JFET as a variable resistor, drive it with a small triangle wave, 0.2V peak @1kHz. Adjust the potentiometer on the gate and observe the change in gain and distortion at the output. a. Submit a printout of input/output waveforms demonstrating the distortion. Use Eq 5.48 in Meyer to explain the distorted shape: ID ~ [(VGS – VP)VDS – VDS2/2] 10k Vout D G 100k 1M 330k -15V Figure 4b S Department of Physics, Stanford University Physics 105, Intermediate Laboratory Seminar: Analog Electronics Lab 6.12 Page 4 To fix the distortion, add a 1M resistor and a 0.01uF cap per Figure 4c. Vin 10k b. c. Drive the circuit as before. Submit a printout of input/output waveforms demonstrating that the distortion is eliminated. Explain i) how the fix adds 1/2VDS to the gate, and ii) why this eliminates the distortion (use Eq 5.48 again). 0.01uF 1M D G 100k Vout 1M S 330k -15V Add a modulating signal to the gate circuit as in Figure 4d. You will need a second function generator for this. vin is now called the carrier signal. This circuit effectively multiplies the two signals, where vmod modulates the amplitude of vcarrier ; this is known as “amplitude modulation” (AM). Use a 0.2Vpeak sine wave for both inputs. Drive vin at 1 MHz, vmod at ~400Hz. Trigger the scope on the vmod signal. d. Submit a printout of waveform clearly showing the modulated carrier. Indicate the carrier and modulation frequencies on the plot. Figure 4c Vcarrier 1uF 10k Vmod 0.01uF 1M D G 100k 1M Vout S 330k -15V Add a length of wire to the output, and wrap around the antenna of an AM radio in the lab. Tune the radio to 1MHz (1000 kHz on the AM dial). Fine tune the radio until you hear the 400 Hz tone through the radio. e. Figure 4d Have your TA check off that you get the AM radio to work. FOR FUN: Use the spectrum analyzer to view your signal (0-10MHz “vector signal analyzer”). This device measures amplitude vs. frequency, instead of the amplitude vs. time you see on a scope. Measure the frequency and relative amplitude of the carrier and the “sidebands”.