* Your assessment is very important for improving the work of artificial intelligence, which forms the content of this project

Download Solution - University of California, Berkeley

Opto-isolator wikipedia , lookup

Switched-mode power supply wikipedia , lookup

Resistive opto-isolator wikipedia , lookup

Inertial navigation system wikipedia , lookup

Nanofluidic circuitry wikipedia , lookup

Rectiverter wikipedia , lookup

Current source wikipedia , lookup

Wilson current mirror wikipedia , lookup

Transistor–transistor logic wikipedia , lookup

Network analysis (electrical circuits) wikipedia , lookup

Power MOSFET wikipedia , lookup

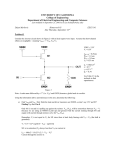

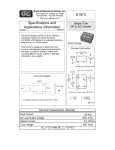

UNIVERSITY OF CALIFORNIA College of Engineering Department of Electrical Engineering and Computer Sciences Last modified on January 31, 2006, by Zhengya Zhang (zyzhang@eecs) Borivoje Nikolic Homework #3 Due Thursday, February 9th EECS 141 Problem #1 Signals on nodes X and Y reach VDD – VT = 2 – 0.5 = 1.5 V. The waveforms are shown below. Conducting devices are also labeled in the plot. The dotted lines represent more accurate waveforms. (Do not need to calculate the numerical values of the time constants.) Problem #2 a) Find Voh, set Vin=0 Only M1 is on and it is pulling up against the resistor. V out (Voh), will be somewhere between Vdd – Vt (because we are using an NMOS to pull up) and ground. Find the current running through M1 and equate with current through resistor; solve for Vout (Voh). Remember, Vt is not equal to Vto for M1 since there is back body biasing with Vsb = Voh (the bulk is grounded) Vt = 0.5 + 0.2*( sqrt(0.6 + Voh) – sqrt(0.6)) M1 is in saturation (Vgt always less than Vds) so current is: Im1 = 100u/2 * 1/0.25 * (2.5 – Voh – Vt)2 Current through the resistor is Iload = Voh/100K Set Im1 = Iload and substitute in for Vt. Only unknown is Voh. Using your favorite equation solver, we get Voh = 1.5787 V Find Vol, set Vin=2.5V When IN is high, both M2 and the resistor are pulling against M1. Repeat the same process for V oh except there is now we have 3 current branches. Im1 = Im2 + Iload Iml and Iload is the same as before except we use Vol instead of Voh. For Im2, we make the assumption that the device will be in triode (reasonable since we expect the output to be low meaning V ds (Vol) to be small compared to Vgt). We will check this assumption at the end. Im2 = 100u * 2/0.25 * ((2.5 - 0 - 0.5) * Vol – Vol2/2) This time, only unknown is Vol so again using any equation solver (or you can guess and iterate), you get Vol = 0.3577 V Does this value check for our original assumption? Yes it does. Vgt = 2 and Vds = 0.786 V so this is an acceptable answer. b) In measuring tp, you must choose Vdd/2 instead of (Voh+Vol)/2. Therefore the H → L transition begins at Vout = Voh and ends at Vout = Vdd/2 = 1.25. Similarly, the L → H transition begins at Vout=Vol and ends at Vout=Vdd/2. Let’s find the equivalent resistance at the start and end points respectively. For this transition, there are 3 components that come into play. There’s an equivalent resistance R M1/M2 looking back into the inverter from the load, and then there’s the resistive load R L in parallel with it. Find ReqHL: RM1/M2: For M1, VDS @ beginning = VDD -VOH = 0.9213 V IDS @ beginning = ½ k’ (W/L) 1(VDD-VOH-Vt)2 =15.793uA, notice that due to body effect, Vt>Vt0 VDS @ end = 1.25V IDS @ end = ½ k’ (W/L)1(VDD-VOH-Vt)2 = 80.12 uA For M2, VDS @ beginning = VOH = 1.5787 V IDS @ beginning = k’(W/L)2[(VDD-Vt)VOH-VOH2/2] = 1.529 mA VDS @ end = 1.25 V IDS @ end = k’(W/L)2[(VDD-Vt)VDD/2-(VDD/2)2/2] = 1.375 mA ReqHL @ beginning = [VOH / (IDS,M2- IDS,M1)]@beginning // 100K = 1.033 KOhm ReqHL @ end = [(VDD/2)/ (IDS,M2- IDS,M1)]@end // 100K = 956.1 Ohm ReqHL = (ReqHL@beginning+ ReqHL@end )/2= 994.55 Ohm Find ReqLH Thankfully, tPLH is easier to calculate because RM2 = ∞ at the start and end of the transition because VGS,M2 = 0V < Vt, meaning it is always off. What are the start and end points of the transition? VOL and Vdd/2 RM1/M2: For M1, VDS @ beginning = VDD -VOL = 2.1423 V IDS @ beginning = ½ k’ (W/L) 1 (VDD-VOL-Vt)2 =512.96 uA, notice that due to body effect, Vt>Vt0 VDS @ end = 1.25V IDS @ end = ½ k’ (W/L)1 (VDD-VOL-Vt)2 = 80.12 uA ReqLH @ beginning = [VOL/ IDS,M1]@beginning // 100K = 4.009 KOhm ReqLH @ end = [(VDD/2) / IDS,M1]@end // 100K = 13.5 KOhm ReqLH = (ReqLH@beginning+ ReqLH@end )/2= 8.753 KOhm Find Ceq: By observation, the loading capacitance CL is much larger than the transistor intrinsic capacitances. Therefore, Ceq ≈ CL = 1pF. Find delay: To calculate both tpLH and tpHL, we cannot simply use the equation t = 0.69ReqCeq because that would imply we were swinging from a rail to half the supply voltage. We’ll have to actually use the exponential to find the constant * RC to find this delay. In the high-low case, the output travels from VOH to Vdd/2; low to high case, output travels from Vol to Vdd/2. The decaying exponentials are: (high-low) V = 0.3577 + 1.221 * exp(-t/RC) (low-high) V = 1.5787 – 1.221 * exp(-t/RC) Subbing in V = Vdd/2, and solving for t, we arrive at the constants: (high-low) 0.3136 (low-high) 1.31 Therefore: tHL = 0.3136 * 994.55 * 1p = 312 ps tLH = 1.31 * 8.753k * 1p = 11.47 ns c) i. When Vin = 0.0V, M2 is off. Current running through circuit = current through resistor. We know Vout = Voh so I = 15.793 uA P = IV = 15.793u * 2.5V = 39.48 uW ii. M1 and M2 are both on. Use current through M1 from above when the input is 2.5V so Vout = Vol. I = 512.96 uA. P = IV = 512.96u * 2.5V = 1.28 mW Problem #3 a) Rules are: i) Poly minimum width = 0.24um ii) Minimum active width = 0.36um iii) Minimum contact size = 0.24um*0.24um iv) Minimum spacing from contact to gate = 0.24um v) Active enclosure of contact = 0.12um Use these values a. L = 0.24um b. W = 0.36um (0.48um ok – just add or subtract a 0.12um*0.12um diffusion area at the next-to-thegate corner of each of the diffusion regions (Source/Drain), this also means add/subtract a diffusion area under the poly (gate) in order to form a channel) c. Ldrain = 0.24um+0.24um+0.12um = 0.6um (Some people figured out how to draw a Ldrain of 0.48 um. It is also correct.) AD, AS, PD, PS below showed one solution, but not the only solution, as long as the calculations are consistent with the L, W values above. AD=AS= 0.48 * 0.6um – 0.12um*0.12um = 0.2736um2 (0.288 um2 ok) d. PD=PS =0.6um*2+0.48um+0.12um = 1.8um (1.68um ok) b) We will use equation 5.5 from the text book, note the NMOS is in velocity saturation and the PMOS is in saturation. (W / L) p kn'VDSAT , n(VM Vt , n 12 VDSAT , n) 1 (W / L)n kp' (VDD VM Vt , p) 2 2 The gate lengths will be identical and thus we can calculate Wp = 1.2154 µm, AD = 0.3809 µm2, and PD = 2.4544 µm. c) We are using Keq =1. (Ok if you calculate Keq) PMOS: Cgc saturated = 2/3 (CoxLpWp) = 1.204 fF triode = CoxLpWp = 1.806 fF Cgb cutoff = CoxLpWp = 1.806 fF Cgdo = COWP = 0.34 fF Cgso = COWP = 0.34 fF NMOS: Cgc Cgb Cgdo saturated = 2/3 (CoxLnWn) = 0.346 fF triode = CoxLnWn = 0.518 fF cutoff = CoxLnWn = 0.518 fF = COWn = 0.112 fF Cgso = COWn = 0.112 fF When output transitions from VDD to VDD/2, PMOS is OFF and assume NMOS stays in SATURATION (at least initially). (It is also ok if you assume NMOS is in linear.) Cin = Cgbp + 2*Cgdop + 2*Cgdon + Cgsn = 1.806 fF + 2*0.34 fF + 2*0.112 fF + 0.346 fF = 3.056 fF Similarly, when output transitions from 0 to VDD/2, NMOS is OFF and assume PMOS stays in SATURATION. (It is also ok if you assume PMOS is in linear.) Cin = Cgbn + 2*Cgdon + 2*Cgdop + Cgsp = 0.518 fF + 2*0.112 fF + 2*0.34 fF + 1.204 fF = 2.626 fF. d) Hw3 Prob3d .lib'g25.mod' TT .param vddp=2.5 .param ln_min=0.24u .param lp_min=0.24u .param l_drain=0.6 .param arean(w)='(w*l_drain*1p)' .param areap(w)='(w*l_drain*1p)' .param perin(w)='((w*1u)+(l_drain*2u))' .param perip(w)='((w*1u)+(l_drain*2u))' VDD vdd 0 'vddp' IIN 0 in 1u M1 out in vdd vdd pmos l='lp_min' w=1.204u M2 out in 0 0 nmos l='ln_min' w=0.36u .ic v(in)=0 .meas t1 trig v(in) val=0.0001 cross=1 targ v(in) val=1.25 cross=1 .meas t2 trig v(in) val=1.25 cross=1 targ v(in) val=2.5 cross=1 .options post=2 nomod .op .tran 0.1ns 10ns .end e) Follow Example 5.2 in the textbook (Note: various formulas can be used to solve this. Credit should be given as long as the results are reasonable.) ID(VM) = 59 uA and g = -28.1 Then use equations 5.7 to solve: VIH = VM - VM/g = 1.294V VIL = VM + (VDD-VM)/g = 1.206V NMH = VDD – VIH = 1.206 V NML = VIL = 1.206 V Problem #4 a) Assume the NMOS transistor operates in the velocity saturation region. (We will verify this later.) VOUT = ID * R i.e., VOUT = R * k’ * W/L * [(VDD – VT – VOUT) VDSAT – VDSAT2/2] Solve the above equation, get VOUT = 1.458 V. VGT = VGS – VT = 0.542 V > VDSAT VDS = 1.042 V > VDSAT Therefore, the assumption is correct. b) In the velocity saturation region, we will have a constant current ID. Then VOUT = ID * R = 1.458 V, which is also constant. Velocity saturation is maintained as long as VDS = VIN – VOUT > VDSAT. When VDS < VDSAT, i.e., VIN – VOUT < VDSAT, VIN < VOUT + VDSAT = 1.958 V, the NMOS transistor enters linear region. Therefore, the NMOS transistor operates in two regions, linear when V IN < 1.958 V and velocity saturation when VIN > 1.958 V. Assume the transistor has a constant resistance R M over the linear region, VOUT = VIN * R / (R + RM). (Do not need to draw a straight line, as long as the region is labeled or indicated as the linear operation.) VOUT Velocity Saturation 1.458 V Linear 1.958V 2.5 V VIN