Design and Simulation of Frequency Divider by Negative Differential

... We studied the novel frequency divider discuss this problem based on numerical using the chaotic circuit with respect to simulation using a test circuit consisting of input signal distortions and the variations in discrete devices. the current-voltage characteristics of the MOS-BJT-NDR. The MOS-BJT- ...

... We studied the novel frequency divider discuss this problem based on numerical using the chaotic circuit with respect to simulation using a test circuit consisting of input signal distortions and the variations in discrete devices. the current-voltage characteristics of the MOS-BJT-NDR. The MOS-BJT- ...

Current-Transformer Phase-Shift Compensation

... In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represe ...

... In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards. TI assumes no liability for applications assistance or customer product design. TI does not warrant or represe ...

OA-13 - Circuits and Systems

... somewhere in the neighborhood of a 60˚ phase margin. This is Comlinear’s targeted phase margin at the gain and Rf used to specify any particular current feedback part. This phase margin, for simple 2 pole Z(s), yields a maximally flat Butterworth filter shape for the closed loop amplifier response ( ...

... somewhere in the neighborhood of a 60˚ phase margin. This is Comlinear’s targeted phase margin at the gain and Rf used to specify any particular current feedback part. This phase margin, for simple 2 pole Z(s), yields a maximally flat Butterworth filter shape for the closed loop amplifier response ( ...

a matrix converter producing two phase supply from single

... devoid of any energy storage element. This output is used for running two phase induction motor. Keywords— two phase matrix converter, Control strategies, Modulation schemes. ...

... devoid of any energy storage element. This output is used for running two phase induction motor. Keywords— two phase matrix converter, Control strategies, Modulation schemes. ...

26_AP1-CATV_AMP

... If you want to distribute the CATV feed to two to four TV sets, you will need a 2-way or 4-way splitter and, if the CATV signal level drops below 55dBuV, an amplifier to boost the signal before it is split. Although the AP1-1xx is a 10dB amplifier, it has a real gain of 11 to 12dB. This is to provid ...

... If you want to distribute the CATV feed to two to four TV sets, you will need a 2-way or 4-way splitter and, if the CATV signal level drops below 55dBuV, an amplifier to boost the signal before it is split. Although the AP1-1xx is a 10dB amplifier, it has a real gain of 11 to 12dB. This is to provid ...

PLL applications The phase-lock-loop

... When the output of the XOR is a pulse with 50% duty cycle, the pll is in lock, or in other words the clock out of pll is sync with the incoming clock (or data..). Let’s start with data consist of string of zeros and clk divide by 2 (N=2): The XOR output is just a replica of the dclock, thus if dclco ...

... When the output of the XOR is a pulse with 50% duty cycle, the pll is in lock, or in other words the clock out of pll is sync with the incoming clock (or data..). Let’s start with data consist of string of zeros and clk divide by 2 (N=2): The XOR output is just a replica of the dclock, thus if dclco ...

232PspiceLecture

... N1, N2, N3 are the external nodes of the subcircuit. The external nodes cannot be 0. The node numbers used inside a subcircuit are strictly local, except for node 0 which is always global. ...

... N1, N2, N3 are the external nodes of the subcircuit. The external nodes cannot be 0. The node numbers used inside a subcircuit are strictly local, except for node 0 which is always global. ...

chapter 7 - Purdue Engineering

... c 1/ , increases. If RS increases from zero, the static sensitivity decreases and the cut-off frequency also decreases. Thus the conclusion is that when inserting an intermediate stage of a signal processing circuit, one must be cognizant of both the preceding stage output impedance as well as the s ...

... c 1/ , increases. If RS increases from zero, the static sensitivity decreases and the cut-off frequency also decreases. Thus the conclusion is that when inserting an intermediate stage of a signal processing circuit, one must be cognizant of both the preceding stage output impedance as well as the s ...

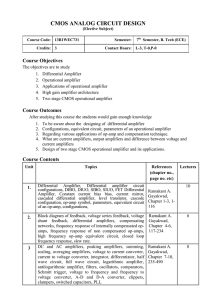

CMOS ANALOG CIRCUIT DESIGN

... Course Outcomes After studying this course the students would gain enough knowledge ...

... Course Outcomes After studying this course the students would gain enough knowledge ...

Harmonic Balance Simulation on ADS

... Intermodulation distortion occurs when more than one input frequency is present in the circuit under evaluation. Therefore, additional frequencies need to be specified when setting up for this type of simulation. Two-tone simulations are generally performed with two closely spaced input frequencies ...

... Intermodulation distortion occurs when more than one input frequency is present in the circuit under evaluation. Therefore, additional frequencies need to be specified when setting up for this type of simulation. Two-tone simulations are generally performed with two closely spaced input frequencies ...

doc - EECS @ UMich

... In this section, include a schematic of your final circuit showing the nominal values of the components (as opposed to measured values). This should be the one and only circuit that you use for all of your hand calculations, simulations, and what was built in the lab. If you changed component values ...

... In this section, include a schematic of your final circuit showing the nominal values of the components (as opposed to measured values). This should be the one and only circuit that you use for all of your hand calculations, simulations, and what was built in the lab. If you changed component values ...

Bode plot

In electrical engineering and control theory, a Bode plot /ˈboʊdi/ is a graph of the frequency response of a system. It is usually a combination of a Bode magnitude plot, expressing the magnitude of the frequency response, and a Bode phase plot, expressing the phase shift. Both quantities are plotted against a horizontal axis proportional to the logarithm of frequency.