Optimizing Clock Synthesis in Small Cells and

... clock reappears. During this holdover period, the accuracy of a cascaded PLL’s output clock is largely a function of how tightly the VCXO can be held. Cascaded PLLs typically use an on-chip digital-to-analog converter (DAC) to drive the VCXO with its last known control voltage setting. It can be dif ...

... clock reappears. During this holdover period, the accuracy of a cascaded PLL’s output clock is largely a function of how tightly the VCXO can be held. Cascaded PLLs typically use an on-chip digital-to-analog converter (DAC) to drive the VCXO with its last known control voltage setting. It can be dif ...

AD8235 英文数据手册DataSheet 下载

... The AD8235 can operate on supply voltages as low as 1.8 V. The input stage allows for wide rail-to-rail input voltage range without the crossover distortion, common in other designs. The rail-torail output enables easy interfacing to ADCs. ...

... The AD8235 can operate on supply voltages as low as 1.8 V. The input stage allows for wide rail-to-rail input voltage range without the crossover distortion, common in other designs. The rail-torail output enables easy interfacing to ADCs. ...

A multiple-crystal interface pll with vco

... sum of a series of phase steps and (b) shown as the result of passing an impulse train through a hold operation. ...

... sum of a series of phase steps and (b) shown as the result of passing an impulse train through a hold operation. ...

Raavi Swapna thesis 2015

... dominated by solid state amplifiers except for the use of high power applications. Solid state devices are being classified into two types: 1) two terminal negative resistance diode devices 2) transistors. Nowadays we are using three terminal device transistors since it can control and amplify in an ...

... dominated by solid state amplifiers except for the use of high power applications. Solid state devices are being classified into two types: 1) two terminal negative resistance diode devices 2) transistors. Nowadays we are using three terminal device transistors since it can control and amplify in an ...

Further Development of a High Gain Microphone

... introduced in the first section of this thesis work. Most recording chain components are briefly explained and signal level ranges are investigated. The main design focus was put on improving the analog circuit design, although, for the sake of clarity the basic structure of the digital control syst ...

... introduced in the first section of this thesis work. Most recording chain components are briefly explained and signal level ranges are investigated. The main design focus was put on improving the analog circuit design, although, for the sake of clarity the basic structure of the digital control syst ...

Contrast

... combination of the incident wave and a π/2 phase shifted wave • Scattered waves from several atoms may interact constructively or destructively to form an amplitude difference (=diffraction pattern). This is too weak to observe except for crystals. • The phase distribution pattern also carries infor ...

... combination of the incident wave and a π/2 phase shifted wave • Scattered waves from several atoms may interact constructively or destructively to form an amplitude difference (=diffraction pattern). This is too weak to observe except for crystals. • The phase distribution pattern also carries infor ...

Voltage-Controlled Oscillators and Frequency Dividers

... accomplish the frequency tuning. At resonance, all the components oscillate at the same frequency ωosc , including the drain current of M1 . That allows us to place a loading RD at drain and take the voltage output from this node. Inductive peaking could be an option here if the output needs to driv ...

... accomplish the frequency tuning. At resonance, all the components oscillate at the same frequency ωosc , including the drain current of M1 . That allows us to place a loading RD at drain and take the voltage output from this node. Inductive peaking could be an option here if the output needs to driv ...

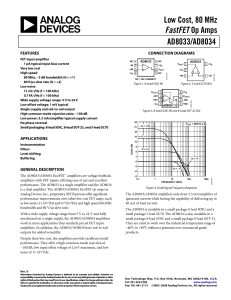

AD8033/AD8034 Low Cost, 80 MHz FastFET Op Amps Data Sheet

... The quiescent power is the voltage between the supply pins (VS) times the quiescent current (IS). Assuming the load (RL) is referenced to midsupply, the total drive power is VS/2 × IOUT, some of which is dissipated in the package and some in the load (VOUT × IOUT). The difference between the total d ...

... The quiescent power is the voltage between the supply pins (VS) times the quiescent current (IS). Assuming the load (RL) is referenced to midsupply, the total drive power is VS/2 × IOUT, some of which is dissipated in the package and some in the load (VOUT × IOUT). The difference between the total d ...

Student Biographies

... Simple but effective. Input resistance accounts for the power drawn from the signal source a the output resistance accounts for changes in output voltage as current is supplied to the load. The model might internally represent from one to to 20 or more transistors Model values determined by analysis ...

... Simple but effective. Input resistance accounts for the power drawn from the signal source a the output resistance accounts for changes in output voltage as current is supplied to the load. The model might internally represent from one to to 20 or more transistors Model values determined by analysis ...

A high conversion-gain Q-band InP DHBT subharmonic

... in front of a mixing stage in order to obtain the wanted subharmonic mixing functionality has also recently been demonstrated in 0.18- m CMOS technology [6]. The design of SHMs is complicated due to the consecutive nonlinear processes of frequency doubling and frequency mixing in one circuit. At -ba ...

... in front of a mixing stage in order to obtain the wanted subharmonic mixing functionality has also recently been demonstrated in 0.18- m CMOS technology [6]. The design of SHMs is complicated due to the consecutive nonlinear processes of frequency doubling and frequency mixing in one circuit. At -ba ...

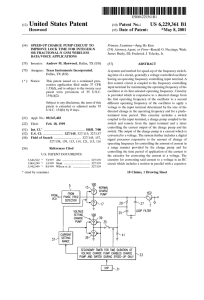

Speed-up charge pump circuit to improve lock time for integer

... is divided doWn by a predetermined factor N in a divider circuit 3 and fed to one input of a comparator 5. A voltage controlled oscillator (VCO) 7 having a knoWn tuning or ...

... is divided doWn by a predetermined factor N in a divider circuit 3 and fed to one input of a comparator 5. A voltage controlled oscillator (VCO) 7 having a knoWn tuning or ...

unit 5 PPT

... synchronously tuned circuits (tuned to same resonant frequencies). Fig. 3.23 shows the relationship of amplification characteristics of individual stages in a staggered pair to the overall amplification of the two stages. ...

... synchronously tuned circuits (tuned to same resonant frequencies). Fig. 3.23 shows the relationship of amplification characteristics of individual stages in a staggered pair to the overall amplification of the two stages. ...

Optimizing High Level Micro Stepping of

... TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguar ...

... TI assumes no liability for applications assistance or the design of Buyers’ products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers’ products and applications, Buyers should provide adequate design and operating safeguar ...

Bode plot

In electrical engineering and control theory, a Bode plot /ˈboʊdi/ is a graph of the frequency response of a system. It is usually a combination of a Bode magnitude plot, expressing the magnitude of the frequency response, and a Bode phase plot, expressing the phase shift. Both quantities are plotted against a horizontal axis proportional to the logarithm of frequency.