AD7841 数据手册DataSheet 下载

... The eight DAC outputs are buffered by op amps that share common VDD and VSS power supplies. If the dc load current changes in one channel (due to an update), this can result in a further dc change in one or another of the channel outputs. This effect is most obvious at high load currents and reduces ...

... The eight DAC outputs are buffered by op amps that share common VDD and VSS power supplies. If the dc load current changes in one channel (due to an update), this can result in a further dc change in one or another of the channel outputs. This effect is most obvious at high load currents and reduces ...

BQ24312 数据资料 dataSheet 下载

... protection against turning power off due to transient overvoltage spikes while still protecting the system. However, if the input voltage remains above VOVP for more than tBLANK(OVP), the internal FET is turned off, removing power from the circuit (see Figure 5). When the input voltage comes back to ...

... protection against turning power off due to transient overvoltage spikes while still protecting the system. However, if the input voltage remains above VOVP for more than tBLANK(OVP), the internal FET is turned off, removing power from the circuit (see Figure 5). When the input voltage comes back to ...

超低功耗、负轨输入、 轨至轨输出、全差分放大器 THS4521-HT 特性

... Test levels: (A) 100% tested. (B) Limits set by characterization and simulation. (C) Typical value only for information. Not directly measureable; calculated using noise gain of 101. Input Offset Voltage Drift, Input Bias Current Drift and Input Offset Current Drift are average values calculated by ...

... Test levels: (A) 100% tested. (B) Limits set by characterization and simulation. (C) Typical value only for information. Not directly measureable; calculated using noise gain of 101. Input Offset Voltage Drift, Input Bias Current Drift and Input Offset Current Drift are average values calculated by ...

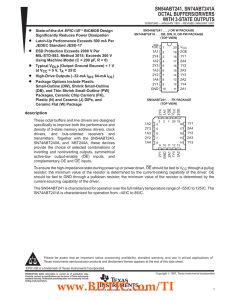

SN54ABT241, SN74ABT241A OCTAL BUFFERS/DRIVERS WITH 3-STATE OUTPUTS

... † Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

... † Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to ...

ADM8696 数据手册DataSheet 下载

... RAM. Connect VOUT to VCC if VOUT and VBATT are not used. 0 V. Ground reference for all signals. Logic Output. RESET goes low whenever LLIN falls below 1.3 V and remains low for 50 ms after LLIN goes above 1.3 V. RESET also goes low for 50 ms if the watchdog timer is enabled but not serviced within i ...

... RAM. Connect VOUT to VCC if VOUT and VBATT are not used. 0 V. Ground reference for all signals. Logic Output. RESET goes low whenever LLIN falls below 1.3 V and remains low for 50 ms after LLIN goes above 1.3 V. RESET also goes low for 50 ms if the watchdog timer is enabled but not serviced within i ...

RF2705G LOW NOISE, MULTI-MODE, QUAD-BAND, QUADRATURE MODULATOR AND PA DRIVER Features

... The RF2705 is a low noise, multi-mode, quad-band direct I/Q to RF modulator and PA driver designed for handset applications where multiple modes of operation are required. Frequency doublers, dividers and LO buffers are included to support a variety of LO generation options. Dynamic power control is ...

... The RF2705 is a low noise, multi-mode, quad-band direct I/Q to RF modulator and PA driver designed for handset applications where multiple modes of operation are required. Frequency doublers, dividers and LO buffers are included to support a variety of LO generation options. Dynamic power control is ...

J322X Replacement Seismic Telemetry System Rev B 08/2014 VLF

... The 100Hz signal drives the cal clock circuits U8,U9 and U10 which produce a one pulse per day signal used to activate the daily calibration signals. The 100Hz signal also provides a reference to a PLL consisting of U5,U6 and U7. This PLL translates the 100Hz to 3.4KHZ which is used as a reference b ...

... The 100Hz signal drives the cal clock circuits U8,U9 and U10 which produce a one pulse per day signal used to activate the daily calibration signals. The 100Hz signal also provides a reference to a PLL consisting of U5,U6 and U7. This PLL translates the 100Hz to 3.4KHZ which is used as a reference b ...

a Complete 14-Bit, 3.0 MSPS Monolithic A/D Converter AD9243*

... suited for both multiplexed systems that switch full-scale voltage levels in successive channels as well as sampling single-channel inputs at frequencies up to and beyond the Nyquist rate. Also, the AD9243 performs well in communication systems employing Direct-IF Down Conversion since the SHA in th ...

... suited for both multiplexed systems that switch full-scale voltage levels in successive channels as well as sampling single-channel inputs at frequencies up to and beyond the Nyquist rate. Also, the AD9243 performs well in communication systems employing Direct-IF Down Conversion since the SHA in th ...

MAX1693/(MAX1693H)/MAX1694 USB Current-Limited Switches with Fault Blanking General Description

... A fault signal notifies the microprocessor that the internal current limit has been reached. A 10ms fault-blanking feature allows momentary faults (such as those caused when hot-swapping into a capacitive load) to be ignored, thus preventing false alarms to the host system. This fault blanking also ...

... A fault signal notifies the microprocessor that the internal current limit has been reached. A 10ms fault-blanking feature allows momentary faults (such as those caused when hot-swapping into a capacitive load) to be ignored, thus preventing false alarms to the host system. This fault blanking also ...

Project 4 - RPI ECSE - Rensselaer Polytechnic Institute

... sampling frequency for your circuit. It is hard to determine exactly what this frequency is by looking at the pulses because the frequency of the pulses changes with the input signal. You can get a reasonable average by averaging over several samples in Figure 7 or by calculating the frequency of th ...

... sampling frequency for your circuit. It is hard to determine exactly what this frequency is by looking at the pulses because the frequency of the pulses changes with the input signal. You can get a reasonable average by averaging over several samples in Figure 7 or by calculating the frequency of th ...

$doc.title

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

... 1. Stresses beyond those listed may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute-maximum-rated condition ...

GTL/BTL: A Low-Swing Solution for High

... tolerant 3.3-V CMOS inverter that can interface with 5-V TTL signals. Bus hold is also provided on the TTL port to eliminate the need for external resistors when the inputs and outputs are unused or floating. The TTL output is a bipolar output. It is similar to the LVT output structure.1 At this tim ...

... tolerant 3.3-V CMOS inverter that can interface with 5-V TTL signals. Bus hold is also provided on the TTL port to eliminate the need for external resistors when the inputs and outputs are unused or floating. The TTL output is a bipolar output. It is similar to the LVT output structure.1 At this tim ...

AD7452 数据手册DataSheet下载

... Analog Ground. Ground reference point for all circuitry on the AD7452. All analog input signals and any external reference signal should be referred to this GND voltage. Chip Select. Active low logic input. This input provides the dual function of initiating a conversion on the AD7452 and framing th ...

... Analog Ground. Ground reference point for all circuitry on the AD7452. All analog input signals and any external reference signal should be referred to this GND voltage. Chip Select. Active low logic input. This input provides the dual function of initiating a conversion on the AD7452 and framing th ...

Signal processors - Scheme of work and lesson plan booklet

... Sets of cards for sentence-ordering to test understanding. ...

... Sets of cards for sentence-ordering to test understanding. ...

I-jet - IAR Systems

... legacy ARM-20 adapter is being used. Other adapters will have different resistors so that I-jet can identify them if needed. A solid GND on this pin means no adapter is being used and the MIPI cable is connected directly between the I-jet and the target board. ...

... legacy ARM-20 adapter is being used. Other adapters will have different resistors so that I-jet can identify them if needed. A solid GND on this pin means no adapter is being used and the MIPI cable is connected directly between the I-jet and the target board. ...

GE Application Guidelines for Non-isolated Converters Application Note

... probe can yield inaccurate results because of their inability to make measurements in the low millivolt range as can be typically encountered when measuring ripple and noise. When making such measurements, it is important to consider oscilloscope sensitivity, system noise, probe grounding and probe ...

... probe can yield inaccurate results because of their inability to make measurements in the low millivolt range as can be typically encountered when measuring ripple and noise. When making such measurements, it is important to consider oscilloscope sensitivity, system noise, probe grounding and probe ...

Si597 Data Sheet

... 2. OE pin includes an internal 17 k pullup resistor to VDD for output enable active high or a 17 k pull-down resistor to GND for output enable active low. See 3. "Ordering Information" on page 7. FS[1:0] includes internal 17 kpull-up to VDD. ...

... 2. OE pin includes an internal 17 k pullup resistor to VDD for output enable active high or a 17 k pull-down resistor to GND for output enable active low. See 3. "Ordering Information" on page 7. FS[1:0] includes internal 17 kpull-up to VDD. ...

MODEL 3101B-TJ101 DELAY EGRESS SYSTEM WIRING

... The sensor and armature assembly are designed for use on a door with existing mechanical latching hardware. If used on a door without a latch, false alarms are possible. In these cases, we suggest using an external trigger such as our 6451 Exit Sensor Bar - connect using terminals 11&12 and disable ...

... The sensor and armature assembly are designed for use on a door with existing mechanical latching hardware. If used on a door without a latch, false alarms are possible. In these cases, we suggest using an external trigger such as our 6451 Exit Sensor Bar - connect using terminals 11&12 and disable ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.