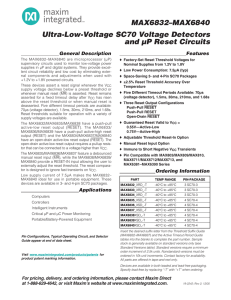

MAX6832–MAX6840 Ultra-Low-Voltage SC70 Voltage Detectors and µP Reset Circuits General Description

... external resistive-divider network can be used to set voltage monitoring thresholds as shown in Figure 1. As the monitored voltage falls, the voltage at RESET-IN decreases and asserts a reset when it falls below the RESET-IN threshold (VRSTIN). The low-leakage current ...

... external resistive-divider network can be used to set voltage monitoring thresholds as shown in Figure 1. As the monitored voltage falls, the voltage at RESET-IN decreases and asserts a reset when it falls below the RESET-IN threshold (VRSTIN). The low-leakage current ...

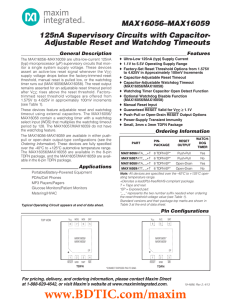

MAX16056–MAX16059 125nA Supervisory Circuits with Capacitor- Adjustable Reset and Watchdog Timeouts General Description

... mode and extended mode. In normal mode (Figure 2), the watchdog timeout period is determined by the value of the capacitor connected between SWT and ground. In extended mode (Figure 3), the watchdog timeout period is multiplied by 128. For example, in extended mode, a 0.33µF capacitor gives a watchd ...

... mode and extended mode. In normal mode (Figure 2), the watchdog timeout period is determined by the value of the capacitor connected between SWT and ground. In extended mode (Figure 3), the watchdog timeout period is multiplied by 128. For example, in extended mode, a 0.33µF capacitor gives a watchd ...

SYSMAC CQM1H Series CQM1H-CPUjj Programmable Controllers

... Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment th ...

... Before using the product under conditions which are not described in the manual or applying the product to nuclear control systems, railroad systems, aviation systems, vehicles, combustion systems, medical equipment, amusement machines, safety equipment, and other systems, machines, and equipment th ...

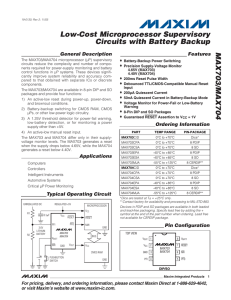

MAX703/MAX704 Low-Cost Microprocessor Supervisory Circuits with Battery Backup General Description

... Resistor R3 adds hysteresis. It will typically be an order of magnitude greater than R1 or R2. The current through R1 and R2 should be at least 1µA to ensure that the 25nA (max) PFI input current does not shift the trip point. R3 should be larger than 10kΩ to prevent it from loading down the PFO pin ...

... Resistor R3 adds hysteresis. It will typically be an order of magnitude greater than R1 or R2. The current through R1 and R2 should be at least 1µA to ensure that the 25nA (max) PFI input current does not shift the trip point. R3 should be larger than 10kΩ to prevent it from loading down the PFO pin ...

Mobile Intel Pentium 4 Processor-M

... Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Information con ...

... Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products. Information con ...

Leakage Power and Circuit Aging Cooptimization by Gate Replacement Techniques

... either high or low, but with gate replacement method, only certain output value can be forced. However, gate replacement does not destroy gate structure, the standard cell library can be directly used; On the other hand, with “control point insertion”, it may introduce extra stacking effect [20], [3 ...

... either high or low, but with gate replacement method, only certain output value can be forced. However, gate replacement does not destroy gate structure, the standard cell library can be directly used; On the other hand, with “control point insertion”, it may introduce extra stacking effect [20], [3 ...

synchro/resolver conversion handbook

... • Synchro Control Transformer (Figure 1.10b) Accepts, at its 3-wire stator terminals (S1, S2, and S3), a set of carrier-frequency signals of the type produced by a synchro control transmitter (or CX), corresponding electrically to some shaft angle θ. It produces, at its rotor terminals (R1 and R2), ...

... • Synchro Control Transformer (Figure 1.10b) Accepts, at its 3-wire stator terminals (S1, S2, and S3), a set of carrier-frequency signals of the type produced by a synchro control transmitter (or CX), corresponding electrically to some shaft angle θ. It produces, at its rotor terminals (R1 and R2), ...

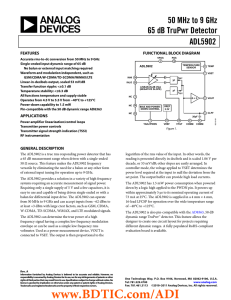

50 MHz to 9 GHz 65 dB TruPwr Detector ADL5902

... logarithm of the rms value of the input. In other words, the reading is presented directly in decibels and is scaled 1.06 V per decade, or 53 mV/dB; other slopes are easily arranged. In controller mode, the voltage applied to VSET determines the power level required at the input to null the deviatio ...

... logarithm of the rms value of the input. In other words, the reading is presented directly in decibels and is scaled 1.06 V per decade, or 53 mV/dB; other slopes are easily arranged. In controller mode, the voltage applied to VSET determines the power level required at the input to null the deviatio ...

Design Considerations For Logic Products

... High-speed switching environments generate noise on power lines (or planes) due to the charging and discharging of internal and external capacitors of an integrated circuit. The instantaneous current generated with the rising and falling edges of the outputs causes the power line (or plane) to ring. ...

... High-speed switching environments generate noise on power lines (or planes) due to the charging and discharging of internal and external capacitors of an integrated circuit. The instantaneous current generated with the rising and falling edges of the outputs causes the power line (or plane) to ring. ...

EE6303 Click here to

... region to the collector contact C. In effect, the buried layer provides a low resistance shunt path for the flow of current. For fabricating an NPN transistor, we begin with a P-type silicon substrate having a resistivity of typically 1Ω-cm, corresponding to an acceptor ion concentration of 1.4 * 1 ...

... region to the collector contact C. In effect, the buried layer provides a low resistance shunt path for the flow of current. For fabricating an NPN transistor, we begin with a P-type silicon substrate having a resistivity of typically 1Ω-cm, corresponding to an acceptor ion concentration of 1.4 * 1 ...

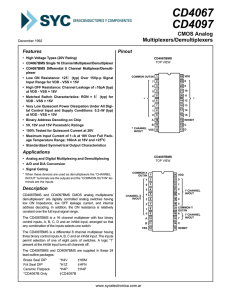

CD4067 CD4097

... channel will lose 3 to 4% of its voltage at the moment the channel turns on or off. This loss of voltage is essentially independent of the address or inhibit signal transition time, if the transition time is less than 1 - 2µs. When the inhibit signal turns a channel off, there is no charge dumping t ...

... channel will lose 3 to 4% of its voltage at the moment the channel turns on or off. This loss of voltage is essentially independent of the address or inhibit signal transition time, if the transition time is less than 1 - 2µs. When the inhibit signal turns a channel off, there is no charge dumping t ...

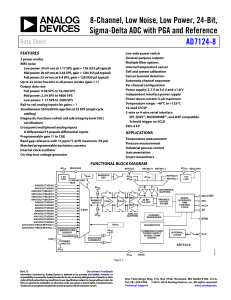

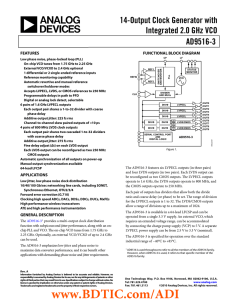

14-Output Clock Generator with Integrated 2.0 GHz VCO AD9516-3

... The AD9516-3 features six LVPECL outputs (in three pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz. Each pair of outputs has divi ...

... The AD9516-3 features six LVPECL outputs (in three pairs) and four LVDS outputs (in two pairs). Each LVDS output can be reconfigured as two CMOS outputs. The LVPECL outputs operate to 1.6 GHz, the LVDS outputs operate to 800 MHz, and the CMOS outputs operate to 250 MHz. Each pair of outputs has divi ...

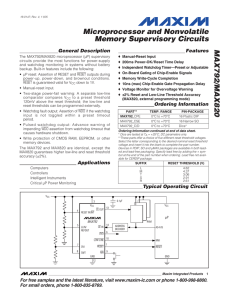

MAX792/MAX820 Microprocessor and Nonvolatile Memory Supervisory Circuits General Description

... switch without an external pull-up resistor or debouncing network. MR internally connects to a 1.30V comparator, and has a high-impedance pull-up to VCC, as shown in Figure 1. The propagation delay from asserting MR to reset asserted is typically 12µs. Pulsing MR low for a minimum of 25µs asserts th ...

... switch without an external pull-up resistor or debouncing network. MR internally connects to a 1.30V comparator, and has a high-impedance pull-up to VCC, as shown in Figure 1. The propagation delay from asserting MR to reset asserted is typically 12µs. Pulsing MR low for a minimum of 25µs asserts th ...

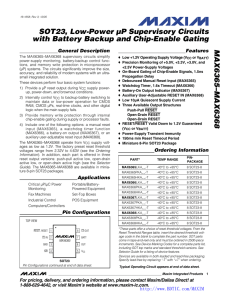

MAX6365–MAX6368 SOT23, Low-Power µP Supervisory Circuits with Battery Backup and Chip-Enable Gating

... CMOS RAM in the event of a power failure. During normal operation, the CE gate is enabled and passes all CE transitions. When reset asserts, this path becomes disabled, preventing erroneous data from corrupting the CMOS RAM. All of these devices use a series transmission gate from CE IN to CE OUT. T ...

... CMOS RAM in the event of a power failure. During normal operation, the CE gate is enabled and passes all CE transitions. When reset asserts, this path becomes disabled, preventing erroneous data from corrupting the CMOS RAM. All of these devices use a series transmission gate from CE IN to CE OUT. T ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.