ATE32CutSheet - Actuation Test Equipment Company

... Volt. Special hysteresis levels may be provided if requested when ordering the module to meet installation-specific requirements. This small-signal de-sensitization of the Model ATE-32 will improve the measurement of the frequency output of a generator operating at low speed without the application ...

... Volt. Special hysteresis levels may be provided if requested when ordering the module to meet installation-specific requirements. This small-signal de-sensitization of the Model ATE-32 will improve the measurement of the frequency output of a generator operating at low speed without the application ...

lecture7

... Is the system given by y[n] x[-n] causal or not? If n 0 , e.g n 4, y[4] x[-4]. This says that at n 4, the output y[n] depend on past value of x[n]. However n 0, e.g n -3, y[-3] x[-(-3)], y[-3] x[3], i.e. the output y[n] depends on future value of input x[ 3]. System is not causal. ...

... Is the system given by y[n] x[-n] causal or not? If n 0 , e.g n 4, y[4] x[-4]. This says that at n 4, the output y[n] depend on past value of x[n]. However n 0, e.g n -3, y[-3] x[-(-3)], y[-3] x[3], i.e. the output y[n] depends on future value of input x[ 3]. System is not causal. ...

Test No 1 Physics Semi Conductor

... 9. Draw the circuit diagram of a common emitter amplifier using n-p-n transistor. What is the phase difference between input signal and output voltage? Draw the input and output waveforms of the signal. ...

... 9. Draw the circuit diagram of a common emitter amplifier using n-p-n transistor. What is the phase difference between input signal and output voltage? Draw the input and output waveforms of the signal. ...

Circuit Timing

... A timing table may specify a range of values for each delay for a device. Maximum: longest possible delay Typical: under near-ideal condition Minimum: smallest. Many manufactures don’t specify this values in most moderate-speed logic families (74LS,74S TTL). Set to zero or 1/4~1/3 of typical ...

... A timing table may specify a range of values for each delay for a device. Maximum: longest possible delay Typical: under near-ideal condition Minimum: smallest. Many manufactures don’t specify this values in most moderate-speed logic families (74LS,74S TTL). Set to zero or 1/4~1/3 of typical ...

Jun 1999 LTC2400 Differential Bridge Digitizers

... LTC2400 Differential Bridge Digitizers by Kevin R. Hoskins and Derek Redmayne This Design Idea covers two circuits that convert differential signals to single-ended, ground referred signals for input to the LTC2400 delta-sigma ADC. These circuits were designed to have a minimal effect on the LTC2400 ...

... LTC2400 Differential Bridge Digitizers by Kevin R. Hoskins and Derek Redmayne This Design Idea covers two circuits that convert differential signals to single-ended, ground referred signals for input to the LTC2400 delta-sigma ADC. These circuits were designed to have a minimal effect on the LTC2400 ...

PAR Grace Design m906 Review

... days I feel a first-class piece of hardware is required to control both monitor speakers and headphones with great precision and the m906 totally fills that role. The m906 consists of three components, the heart lives in a 2U rack mounted brushed stainless steel mainframe with only a single 1/4-inch ...

... days I feel a first-class piece of hardware is required to control both monitor speakers and headphones with great precision and the m906 totally fills that role. The m906 consists of three components, the heart lives in a 2U rack mounted brushed stainless steel mainframe with only a single 1/4-inch ...

JLS Signal Generator

... products notation. • This time we will look at Project 3, which covers JLS, sum of products notation, and logic gates. ...

... products notation. • This time we will look at Project 3, which covers JLS, sum of products notation, and logic gates. ...

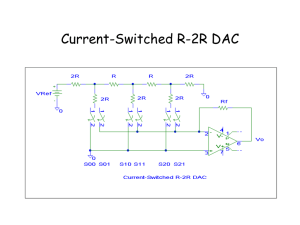

Current-Switched R-2R DAC

... continuously I0 = VREF/R then VIN = VREF.Count/CountMax Reduces integrator capacitor error of DualSlope Capable of 10-8 (26-bit) performance, if you can wait - speed v resolution DVM type ADC ...

... continuously I0 = VREF/R then VIN = VREF.Count/CountMax Reduces integrator capacitor error of DualSlope Capable of 10-8 (26-bit) performance, if you can wait - speed v resolution DVM type ADC ...

Clocking-Strategies - KIT

... clk signal may be passed through a transmission gate to equalize delay with respect to - clk Dynamic single clock latches Dynamic latches storing data on gate capacitance of inverter (or logic gate) Can be clocked at high frequency since very little delay in latch elements Examples: (a) or ...

... clk signal may be passed through a transmission gate to equalize delay with respect to - clk Dynamic single clock latches Dynamic latches storing data on gate capacitance of inverter (or logic gate) Can be clocked at high frequency since very little delay in latch elements Examples: (a) or ...

Test Procedure for the NCP1083WIRGEVB Evaluation Board

... to connector P1, pin 7, 8 for the positive node and pin 9, 10 for ground. 4) The DC/DC converter shall start working as soon as detection and classification is completed in PoE powered mode or as soon as power is applied on the auxiliary input. 5) Measure the output voltage to be 12V and that ripple ...

... to connector P1, pin 7, 8 for the positive node and pin 9, 10 for ground. 4) The DC/DC converter shall start working as soon as detection and classification is completed in PoE powered mode or as soon as power is applied on the auxiliary input. 5) Measure the output voltage to be 12V and that ripple ...

AK8111 - Asahi Kasei Microdevices

... tariffs, currency exchange, or strategic materials. z AKEMD products are neither intended nor authorized for use as critical componentsNote1) in any safety, life support, or other hazard related device or systemNote2), and AKEMD assumes no responsibility for such use, except for the use approved wit ...

... tariffs, currency exchange, or strategic materials. z AKEMD products are neither intended nor authorized for use as critical componentsNote1) in any safety, life support, or other hazard related device or systemNote2), and AKEMD assumes no responsibility for such use, except for the use approved wit ...

VC Divider Operation manual — 1 —

... becomes inactive. All 16 division factor values are available when voltage control is used. The voltage range of each option is about 0.4 volts. 4. In1 Jack. Clock input of the upper channel. The threshold level is about +1v. 5. Out1 Jack. Clock output of the upper channel. The logic levels are 0v ...

... becomes inactive. All 16 division factor values are available when voltage control is used. The voltage range of each option is about 0.4 volts. 4. In1 Jack. Clock input of the upper channel. The threshold level is about +1v. 5. Out1 Jack. Clock output of the upper channel. The logic levels are 0v ...

Use the proportionality property of linear circuits to find the voltage Vx

... Find k by analysis of that circuit. We can then use k to find the output when given any input. So set Vx = 1 V and let the input be unknown. There is no current flowing through either the 22 Ω resistor or the 81 Ω resistor. This means that the voltage across each element is 0V. So we can replace the ...

... Find k by analysis of that circuit. We can then use k to find the output when given any input. So set Vx = 1 V and let the input be unknown. There is no current flowing through either the 22 Ω resistor or the 81 Ω resistor. This means that the voltage across each element is 0V. So we can replace the ...

Digital Electronics - Test bank of Questions and Problems In order to

... flip-flop operates in step with the clock. Another term for this is: a. Synchronously b. Asynchronously c. Latched d. Unilaterally ...

... flip-flop operates in step with the clock. Another term for this is: a. Synchronously b. Asynchronously c. Latched d. Unilaterally ...

HCPL3700, An optocoupler with a difference

... see that they operate as expected. This is one parameter they would likely check. At a set input current they should get a known output current at a predictable output voltage. Speed We have a limitation on speed of these devices. This is a question of how fast we can get the LED to turn on and off. ...

... see that they operate as expected. This is one parameter they would likely check. At a set input current they should get a known output current at a predictable output voltage. Speed We have a limitation on speed of these devices. This is a question of how fast we can get the LED to turn on and off. ...

debug0

... Check rise and fall times Inputs and Outputs Understand system behaviour Start with small portion of system Select as simple an input or set of inputs as possible Ideally DC Steady Known transient - 3 of 8 - ...

... Check rise and fall times Inputs and Outputs Understand system behaviour Start with small portion of system Select as simple an input or set of inputs as possible Ideally DC Steady Known transient - 3 of 8 - ...

On the same wavelength – The frequency inverters e

... SycoTec is adding two new high-frequency inverters to its product range. The table version e@syDrive® TV 4504 is the perfect combination of safety and performance. With the galvanic separation, it enables the safe operation of spindles without protective conductor, such as our best-sellers of type 4 ...

... SycoTec is adding two new high-frequency inverters to its product range. The table version e@syDrive® TV 4504 is the perfect combination of safety and performance. With the galvanic separation, it enables the safe operation of spindles without protective conductor, such as our best-sellers of type 4 ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.