DC to DC Square Root Transmitters, Isolated API 4440 G

... span) for the corresponding square root value at the output, rather than zero, to avoid calibrating on the very large input slope near zero. 7. Set the input to the high end of the input range. 8. Adjust the module Span control for the specified high (100%) output level. 9. The zero and span contr ...

... span) for the corresponding square root value at the output, rather than zero, to avoid calibrating on the very large input slope near zero. 7. Set the input to the high end of the input range. 8. Adjust the module Span control for the specified high (100%) output level. 9. The zero and span contr ...

DS1265W 3.3V 8Mb Nonvolatile SRAM FEATURES PIN ASSIGNMENT

... before another cycle can be initiated. The OE control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output drivers are enabled ( CE and OE active), then WE will disable the outputs in tODW from its falling edge. ...

... before another cycle can be initiated. The OE control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output drivers are enabled ( CE and OE active), then WE will disable the outputs in tODW from its falling edge. ...

High 5 Casino Game On Facebook List Of Casino Card Games

... EMEA Tel/Fax: +44 .1767.312632 | Asia Hong Kong Tel: +852.2854.4285 Fax +852.2854.4282 | Japan Tel: +81.3.3374.2079 Fax: +81.3.3374.5221 © 2010 FOX ELECTRONICS | ISO9001:2000 Certified ...

... EMEA Tel/Fax: +44 .1767.312632 | Asia Hong Kong Tel: +852.2854.4285 Fax +852.2854.4282 | Japan Tel: +81.3.3374.2079 Fax: +81.3.3374.5221 © 2010 FOX ELECTRONICS | ISO9001:2000 Certified ...

AD7893 美国模拟器件公司ADI英文数据手册

... conventional successive-approximation converter based on an R-2R ladder structure. The signal scaling on the AD7893-10, AD7893-5 and AD7893-3 allows the part to handle ± 10 V, 0 V to +5 V and ± 2.5 V input signals, respectively, while operating from a single +5 V supply. The AD7893-2 accepts an anal ...

... conventional successive-approximation converter based on an R-2R ladder structure. The signal scaling on the AD7893-10, AD7893-5 and AD7893-3 allows the part to handle ± 10 V, 0 V to +5 V and ± 2.5 V input signals, respectively, while operating from a single +5 V supply. The AD7893-2 accepts an anal ...

L23-Clock Tree Synthe..

... information will be used). All that's needed in addition for power optimization is to set a power constraint and supply switching activity - the same switching activity used with power analysis. What you get out of power optimization is a gate-level netlist, optimized to meet all of your constraints ...

... information will be used). All that's needed in addition for power optimization is to set a power constraint and supply switching activity - the same switching activity used with power analysis. What you get out of power optimization is a gate-level netlist, optimized to meet all of your constraints ...

doc - AState.edu

... % Get the number of points to input. n = input('Enter number of points: '); % Check to see if we have enough input data. if n < 2 % Insufficient data disp ('At least 2 values must be entered.'); else % we will have enough data, so let's get it. % Loop to read input values. for ii = 1:n ...

... % Get the number of points to input. n = input('Enter number of points: '); % Check to see if we have enough input data. if n < 2 % Insufficient data disp ('At least 2 values must be entered.'); else % we will have enough data, so let's get it. % Loop to read input values. for ii = 1:n ...

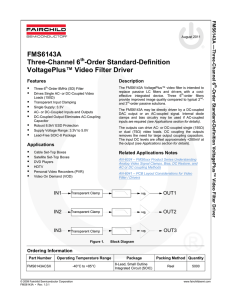

FMS6143A Three-Channel 6 -Order Standard-Definition VoltagePlus™ Video Filter Driver

... Since the interior of most systems; such as set-top boxes, TVs, and DVD players; are at TA=+70ºC; consideration must be given to providing an adequate heat sink for the device package for maximum heat dissipation. When designing a system board, determine how much power each device dissipates. Ensure ...

... Since the interior of most systems; such as set-top boxes, TVs, and DVD players; are at TA=+70ºC; consideration must be given to providing an adequate heat sink for the device package for maximum heat dissipation. When designing a system board, determine how much power each device dissipates. Ensure ...

DAC-ADC CW-1 - WordPress.com

... required • The analog sample is simultaneously applied to one input (non-inverting) of all the comparators • Other input to the comparator is a DC voltage derived from the potential divider. ...

... required • The analog sample is simultaneously applied to one input (non-inverting) of all the comparators • Other input to the comparator is a DC voltage derived from the potential divider. ...

Analysis and Simulation of an Analog Guitar Compressor

... the system matrices we have to solve these equations for v̇Ci . After this the discretization has to be operated and non-linear equations have to be solved. Since there are two output voltages, V− and V+ , the discrete output y(n) consists of two entries. 4.2. Output Stage The simulation of the outp ...

... the system matrices we have to solve these equations for v̇Ci . After this the discretization has to be operated and non-linear equations have to be solved. Since there are two output voltages, V− and V+ , the discrete output y(n) consists of two entries. 4.2. Output Stage The simulation of the outp ...

ics85401.pdf

... The aforementioned trademark, HiPerClockS™ is a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) ass ...

... The aforementioned trademark, HiPerClockS™ is a trademark of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorporated (ICS) ass ...

EE121Lec02 - My FIT (my.fit.edu)

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

... • VOLmax and VOHmin are specified for certain output-current values, IOLmax and IOHmax. – No need to know details about the output circuit, only the load. ...

ARM-based Flash MCU SAM G53 Series Description SUMMARY DATASHEET

... The Atmel® SAM G53 series is a member of the SAM G family of Flash microcontrollers based on the high-performance 32-bit ARM® Cortex®-M4 RISC processor. It operates at a maximum speed of 48 MHz and features up to 512 Kbytes of Flash and 96 Kbytes of SRAM. The peripheral set includes one USART, two U ...

... The Atmel® SAM G53 series is a member of the SAM G family of Flash microcontrollers based on the high-performance 32-bit ARM® Cortex®-M4 RISC processor. It operates at a maximum speed of 48 MHz and features up to 512 Kbytes of Flash and 96 Kbytes of SRAM. The peripheral set includes one USART, two U ...

a Wideband, High Output Current, Fast Settling Op Amp AD842*

... in a gain-of-2 follower configuration. The AD842 maintains a typical slew rate of 375 V/µs, which means it can drive a ± 10 V, 6.0 MHz signal or a ± 3 V, 19.9 MHz signal. The termination resistor, RT, (when equal to the characteristic impedance of the cable) minimizes reflections from the far end of ...

... in a gain-of-2 follower configuration. The AD842 maintains a typical slew rate of 375 V/µs, which means it can drive a ± 10 V, 6.0 MHz signal or a ± 3 V, 19.9 MHz signal. The termination resistor, RT, (when equal to the characteristic impedance of the cable) minimizes reflections from the far end of ...

SN74SSTV32867-EP - Texas Instruments

... The SN74SSTV32867-EP operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low. The device supports low-power standby operation. When RESET is low, the differential input receivers are disabled, and undriven (floating) data, clock, and ...

... The SN74SSTV32867-EP operates from a differential clock (CLK and CLK). Data are registered at the crossing of CLK going high and CLK going low. The device supports low-power standby operation. When RESET is low, the differential input receivers are disabled, and undriven (floating) data, clock, and ...

Evaluates: MAX3665 MAX3665 Evaluation Kit General Description Features

... The connector at INPUT is terminated with 50Ω to ground. This voltage is then AC-coupled to a resistance in series with the MAX3665’s input, creating an input current. U2 and U3 form a simple DC current source that is used to apply a DC offset to the input signal. The values of the series resistive ...

... The connector at INPUT is terminated with 50Ω to ground. This voltage is then AC-coupled to a resistance in series with the MAX3665’s input, creating an input current. U2 and U3 form a simple DC current source that is used to apply a DC offset to the input signal. The values of the series resistive ...

ics844071i.pdf

... The aforementioned trademarks, HiPerClockS and FemtoClocks are trademarks of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorp ...

... The aforementioned trademarks, HiPerClockS and FemtoClocks are trademarks of Integrated Circuit Systems, Inc. or its subsidiaries in the United States and/or other countries. While the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems, Incorp ...

DACs

... • A symbol that assumed a bipolar output would have a positive and negative input reference • The chart shown in Figure 14-1(b) graphically shows the relationship between digital inputs and analog outputs for a Unipolar output 3-bit DAC » With a 000 input the output ~ common » With a binary 4 input ...

... • A symbol that assumed a bipolar output would have a positive and negative input reference • The chart shown in Figure 14-1(b) graphically shows the relationship between digital inputs and analog outputs for a Unipolar output 3-bit DAC » With a 000 input the output ~ common » With a binary 4 input ...

ADS808: 12-Bit, 70MHz Sampling Analog-to

... Input Biasing (VCM) The ADS808 operates from a single +5V supply, and requires each of the analog inputs to be externally biased to a common-mode voltage of typically +2.5V. This allows a symmetrical signal swing while maintaining sufficient headroom to either supply rail. Communication systems are ...

... Input Biasing (VCM) The ADS808 operates from a single +5V supply, and requires each of the analog inputs to be externally biased to a common-mode voltage of typically +2.5V. This allows a symmetrical signal swing while maintaining sufficient headroom to either supply rail. Communication systems are ...

NB3L8533 - 2.5V/3.3V Differential 2:1 MUX to 4 LVPECL Fanout Buffer

... at www.onsemi.com/site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability ari ...

... at www.onsemi.com/site/pdf/Patent−Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability ari ...

NB4L52 - 2.5 V/3.3 V/5.0 V Differential Data/Clock D Flip

... 2.5 V/3.3 V/5.0 V Differential Data/Clock D Flip-Flop with Reset Multi−Level Inputs to LVPECL Translator w/ Internal Termination The NB4L52 is a differential Data and Clock D flip−flop with a differential asynchronous Reset. The differential inputs incorporate internal 50 W termination resistors and ...

... 2.5 V/3.3 V/5.0 V Differential Data/Clock D Flip-Flop with Reset Multi−Level Inputs to LVPECL Translator w/ Internal Termination The NB4L52 is a differential Data and Clock D flip−flop with a differential asynchronous Reset. The differential inputs incorporate internal 50 W termination resistors and ...

Design and Simulation of High Speed Low Power CMOS

... In other words, unlike conventional double-tail dynamic comparator, in which Vfn/fp is just a function of input transistor trans-conductance and input voltage difference ,in the proposed structure as soon as the comparator detects that for instance node fn discharges faster, a pMOS transistor (Mc1) ...

... In other words, unlike conventional double-tail dynamic comparator, in which Vfn/fp is just a function of input transistor trans-conductance and input voltage difference ,in the proposed structure as soon as the comparator detects that for instance node fn discharges faster, a pMOS transistor (Mc1) ...

Novalog, Inc. Preliminary SIRF SIRFIR™ 4Mbps IrDA

... be placed as close as possible to this input and separated by ground from both SIRF receive data outputs. VSS (Analog), VSS (Digital) Analog and Digital Ground (Power). Connect to ground of the power supply. A solid ground plane is essential for proper operation. IRRX* IR Receive Data (Output, activ ...

... be placed as close as possible to this input and separated by ground from both SIRF receive data outputs. VSS (Analog), VSS (Digital) Analog and Digital Ground (Power). Connect to ground of the power supply. A solid ground plane is essential for proper operation. IRRX* IR Receive Data (Output, activ ...

NB6L239MNEVB NB6L239MNEVB Evaluation Board User's Manual •

... to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, ...

... to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.