CDCM1802: Clock Buffer w/Programmable Divider, LVPECL I/O +

... Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for example, with 100-Ω across input). The input can also I be driven by a single-ended sign ...

... Therefore, almost any type of differential signal can drive this input (LVPECL, LVDS, CML, HSTL). Since the input is high-impedance, it is recommended to terminate the PCB transmission line before the input (for example, with 100-Ω across input). The input can also I be driven by a single-ended sign ...

MAX11212 18-Bit, Single-Channel, Ultra-Low Power, Delta- Sigma ADC with 2-Wire Serial Interface

... and the analog supply (AVDD). The POR circuitry ensures proper device default conditions after either a digital or analog power-sequencing event. The MAX11212 performs a self-calibration operation as part of the startup initialization sequence whenever a digital POR is triggered. It is important to ...

... and the analog supply (AVDD). The POR circuitry ensures proper device default conditions after either a digital or analog power-sequencing event. The MAX11212 performs a self-calibration operation as part of the startup initialization sequence whenever a digital POR is triggered. It is important to ...

MAX1202/MAX1203 5V, 8-Channel, Serial, 12-Bit ADCs with 3V Digital Interface General Description

... and a serial strobe output allows direct connection to TMS320-family digital signal processors. The MAX1202/MAX1203 use either the internal clock or an external serial-interface clock to perform successiveapproximation analog-to-digital conversions. The serial interface operates at up to 2MHz. The M ...

... and a serial strobe output allows direct connection to TMS320-family digital signal processors. The MAX1202/MAX1203 use either the internal clock or an external serial-interface clock to perform successiveapproximation analog-to-digital conversions. The serial interface operates at up to 2MHz. The M ...

Evaluate: MAX4444/MAX4445 MAX4444 Evaluation Kit General Description Features

... The MAX4444 EV kit is fully assembled and tested. Follow these steps to verify board operation. Do not turn on the power supply until all connections are completed. 1) Connect a +5V power supply to the VCC pin and a -5V power supply to the VEE pin. Connect power-supply ground to the GND pads. 2) Ens ...

... The MAX4444 EV kit is fully assembled and tested. Follow these steps to verify board operation. Do not turn on the power supply until all connections are completed. 1) Connect a +5V power supply to the VCC pin and a -5V power supply to the VEE pin. Connect power-supply ground to the GND pads. 2) Ens ...

AD633 (Rev. K)

... inputs are converted to differential currents by voltage-to-current converters. The product of these currents is generated by the multiplying core. A buried Zener reference provides an overall scale factor of 10 V. The sum of (X × Y)/10 + Z is then applied to the output amplifier. The amplifier summ ...

... inputs are converted to differential currents by voltage-to-current converters. The product of these currents is generated by the multiplying core. A buried Zener reference provides an overall scale factor of 10 V. The sum of (X × Y)/10 + Z is then applied to the output amplifier. The amplifier summ ...

AD7352 数据手册DataSheet下载

... Chip Select. Active low, logic input. This input provides the dual functions of initiating conversions on the AD7352 and framing the serial data transfer. Digital Ground. This is the ground reference point for all digital circuitry on the AD7352. Connect this pin to the DGND plane of a system. The D ...

... Chip Select. Active low, logic input. This input provides the dual functions of initiating conversions on the AD7352 and framing the serial data transfer. Digital Ground. This is the ground reference point for all digital circuitry on the AD7352. Connect this pin to the DGND plane of a system. The D ...

Probes-Fact

... dominant effect on probe loading. Probe capacitance increases the rise and fall times on fast transition waveforms and decreasesthe amplitude of high frequency details in waveforms. ...

... dominant effect on probe loading. Probe capacitance increases the rise and fall times on fast transition waveforms and decreasesthe amplitude of high frequency details in waveforms. ...

MAX3188/MAX3189 1Mbps, 1µA RS-232 Transmitters in SOT23-6 General Description Features

... from ±4.5V to ±6V supplies. RS-232 data transmission is guaranteed up to 250kbps with the MAX3188 and up to 1Mbps with the MAX3189. The MAX3188/MAX3189 transmitters are inverting level translators that convert CMOS-logic levels to 5V EIA/TIA-232 levels. They feature a shutdown input that reduces cur ...

... from ±4.5V to ±6V supplies. RS-232 data transmission is guaranteed up to 250kbps with the MAX3188 and up to 1Mbps with the MAX3189. The MAX3188/MAX3189 transmitters are inverting level translators that convert CMOS-logic levels to 5V EIA/TIA-232 levels. They feature a shutdown input that reduces cur ...

RAIL TO RAIL OP AMP AMPLIFIER WITH UNIPOLAR SUPPLY

... amplitude, frequency of 1kHz and a 0V DC component value. Which part of the input voltage does the circuit amplify? Explain. Draw vO(t) for vI(t) - triangular signal with 1.5V amplitude, frequency of 1kHz and a 0V DC component value. Draw the VTC vO(vI) for vI(t) of amplitude 1.5V. b) For the ...

... amplitude, frequency of 1kHz and a 0V DC component value. Which part of the input voltage does the circuit amplify? Explain. Draw vO(t) for vI(t) - triangular signal with 1.5V amplitude, frequency of 1kHz and a 0V DC component value. Draw the VTC vO(vI) for vI(t) of amplitude 1.5V. b) For the ...

PI6LC4840

... Crystal to LVDS/LVCMOS Frequency Synthesizer Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested) Note: Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation o ...

... Crystal to LVDS/LVCMOS Frequency Synthesizer Maximum Ratings (Above which the useful life may be impaired. For user guidelines, not tested) Note: Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation o ...

DAC7715 数据资料 dataSheet 下载

... DACs (the two remaining bits are unused). The converter can be powered from a single +15V supply or a dual ±15V supply. Each device offers a reset function which immediately sets all DAC output voltages and internal registers to either zero-scale (code 000H) or mid-scale (code 800H). The reset code ...

... DACs (the two remaining bits are unused). The converter can be powered from a single +15V supply or a dual ±15V supply. Each device offers a reset function which immediately sets all DAC output voltages and internal registers to either zero-scale (code 000H) or mid-scale (code 800H). The reset code ...

Low Power Compensation Technique for Process Variations in Sub

... current in the LNA. However, the large transistor used in the design makes the scheme unsuitable for low supply voltage processes. Sivonenet al. [14] identified that the variation in gain of an LNA is a function of its load impedance and, by replacing the load resistor with a parallel combination of ...

... current in the LNA. However, the large transistor used in the design makes the scheme unsuitable for low supply voltage processes. Sivonenet al. [14] identified that the variation in gain of an LNA is a function of its load impedance and, by replacing the load resistor with a parallel combination of ...

LT5506

... differential AC input impedance of the LT5506 is about 200Ω, thus a 1:4 (impedance ratio) RF transformer with central tap can be used. In Figure 6, the evaluation board schematic is shown using a 1:4 transformer. The measured input sensitivity of this board is about –82.6dBm for a 10dB signal-to-noi ...

... differential AC input impedance of the LT5506 is about 200Ω, thus a 1:4 (impedance ratio) RF transformer with central tap can be used. In Figure 6, the evaluation board schematic is shown using a 1:4 transformer. The measured input sensitivity of this board is about –82.6dBm for a 10dB signal-to-noi ...

High-Speed ADC Sets Input Common-Mode Range

... track each other to ensure a proper matching of dc voltage levels. The COM pin sources 5mA, and can be used as needed to set the dc level of other circuit elements in the system. Because the COM internal buffers are powered down during ADC shutdown, this level-setting approach saves more power than ...

... track each other to ensure a proper matching of dc voltage levels. The COM pin sources 5mA, and can be used as needed to set the dc level of other circuit elements in the system. Because the COM internal buffers are powered down during ADC shutdown, this level-setting approach saves more power than ...

MAX3430 ±80V Fault-Protected, Fail-Safe, 1/4-Unit Load, +3.3V RS-485 Transceiver General Description

... Inserting circuit boards into a hot, or powered backplane may cause voltage transients on DE, RE, and receiver inputs A and B that can lead to data errors. For example, upon initial circuit board insertion, the processor undergoes a power-up sequence. During this period, the highimpedance state of t ...

... Inserting circuit boards into a hot, or powered backplane may cause voltage transients on DE, RE, and receiver inputs A and B that can lead to data errors. For example, upon initial circuit board insertion, the processor undergoes a power-up sequence. During this period, the highimpedance state of t ...

LM111/LM211/LM311 Voltage Comparator

... positive input will cause about 3 mV of hysteresis. However, if RS is larger than 100Ω, such as 50 kΩ, it would not be reasonable to simply increase the value of the positive feedback resistor above 510 kΩ. The circuit of Figure 3 could be used, but it is rather awkward. See the notes in paragraph 7 ...

... positive input will cause about 3 mV of hysteresis. However, if RS is larger than 100Ω, such as 50 kΩ, it would not be reasonable to simply increase the value of the positive feedback resistor above 510 kΩ. The circuit of Figure 3 could be used, but it is rather awkward. See the notes in paragraph 7 ...

a LC MOS 16-Bit Voltage Output DAC

... This is the readback function which is useful in ATE applications. LDAC allows simultaneous updating of DACs in a multiDAC system and the CLR line will reset the contents of the DAC latch to 00 . . . 000 or 10 . . . 000 depending on the state of R/W. This means that the DAC output can be reset to 0 ...

... This is the readback function which is useful in ATE applications. LDAC allows simultaneous updating of DACs in a multiDAC system and the CLR line will reset the contents of the DAC latch to 00 . . . 000 or 10 . . . 000 depending on the state of R/W. This means that the DAC output can be reset to 0 ...

ISD4004 Series

... 3. Data is clocked in on the rising edge of the SCLK signal and clocked out on the falling edge of the SCLK signal, with LSB first. 4. Playback and record operations are initiated when the device is enabled by asserting the SS pin LOW, shifting in an opcode and an address data to the ISD4004 device ...

... 3. Data is clocked in on the rising edge of the SCLK signal and clocked out on the falling edge of the SCLK signal, with LSB first. 4. Playback and record operations are initiated when the device is enabled by asserting the SS pin LOW, shifting in an opcode and an address data to the ISD4004 device ...

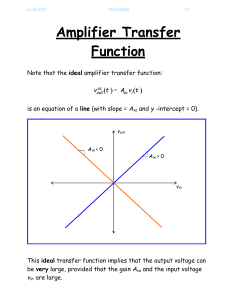

Amplifier Transfer F..

... For example, the output limits of an amplifier might be L+ = 15 V and L- = -15 V. However, we find that these limits are also often asymmetric (e.g., L+ = +15 V and L- = +5 V). ...

... For example, the output limits of an amplifier might be L+ = 15 V and L- = -15 V. However, we find that these limits are also often asymmetric (e.g., L+ = +15 V and L- = +5 V). ...

Flip-flop (electronics)

In electronics, a flip-flop or latch is a circuit that has two stable states and can be used to store state information. A flip-flop is a bistable multivibrator. The circuit can be made to change state by signals applied to one or more control inputs and will have one or two outputs. It is the basic storage element in sequential logic. Flip-flops and latches are a fundamental building block of digital electronics systems used in computers, communications, and many other types of systems.Flip-flops and latches are used as data storage elements. A flip-flop stores a single bit (binary digit) of data; one of its two states represents a ""one"" and the other represents a ""zero"". Such data storage can be used for storage of state, and such a circuit is described as sequential logic. When used in a finite-state machine, the output and next state depend not only on its current input, but also on its current state (and hence, previous inputs). It can also be used for counting of pulses, and for synchronizing variably-timed input signals to some reference timing signal.Flip-flops can be either simple (transparent or opaque) or clocked (synchronous or edge-triggered). Although the term flip-flop has historically referred generically to both simple and clocked circuits, in modern usage it is common to reserve the term flip-flop exclusively for discussing clocked circuits; the simple ones are commonly called latches.Using this terminology, a latch is level-sensitive, whereas a flip-flop is edge-sensitive. That is, when a latch is enabled it becomes transparent, while a flip flop's output only changes on a single type (positive going or negative going) of clock edge.