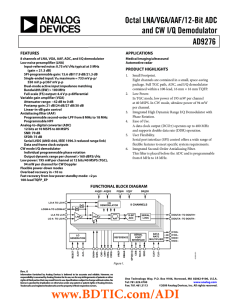

Octal LNA/VGA/AAF/12-Bit ADC and CW I/Q Demodulator AD9276

... sample rate clock for full performance operation. No external reference or driver components are required for many applications. The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock (DCO±) for capturing data on the output and a frame clock (F ...

... sample rate clock for full performance operation. No external reference or driver components are required for many applications. The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock (DCO±) for capturing data on the output and a frame clock (F ...

... In this work, a fully differential Operational Amplifier (OpAmp) with high GainBandwidth (GBW), high linearity and Signal-to-Noise ratio (SNR) has been designed in 65nm CMOS technology with 1.1v supply voltage. The performance of the OpAmp is evaluated using Cadence and Matlab simulations and it sat ...

MAX9320/MAX9320A 1:2 Differential LVPECL/LVECL/HSTL Clock and Data Drivers General Description

... The MAX9320/MAX9320A are low-skew, 1-to-2 differential drivers designed for clock and data distribution. The input is reproduced at two differential outputs. The differential input can be adapted to accept single-ended inputs by applying an external reference voltage. The MAX9320/MAX9320A feature ul ...

... The MAX9320/MAX9320A are low-skew, 1-to-2 differential drivers designed for clock and data distribution. The input is reproduced at two differential outputs. The differential input can be adapted to accept single-ended inputs by applying an external reference voltage. The MAX9320/MAX9320A feature ul ...

Upgrading Coaxial Distribution Networks with Amplified Taps

... coaxial distribution plant as the weak point in these networks. This paper presents an approach to distribution architecture, and to tap design, which addresses this issue. This approach greatly reduces or eliminates the use of in-line amplification in distribution plant, and introduces the use of " ...

... coaxial distribution plant as the weak point in these networks. This paper presents an approach to distribution architecture, and to tap design, which addresses this issue. This approach greatly reduces or eliminates the use of in-line amplification in distribution plant, and introduces the use of " ...

Changes to the FADC buffer circuits and ASIC mux out buffer/ADC

... Despite the huge improvement over AD8031, there is still a small risk of channel to channel crosstalk caused by a channel loading Vref heavily and dragging down neighbours- the extra current significantly reduces this effect (see simulation plots). The only way to avoid the risk entirely is to have ...

... Despite the huge improvement over AD8031, there is still a small risk of channel to channel crosstalk caused by a channel loading Vref heavily and dragging down neighbours- the extra current significantly reduces this effect (see simulation plots). The only way to avoid the risk entirely is to have ...

[External Circuit] Package Models with

... discussion, the IBIS circuit block is called a “model unit” in Figure 22 and Figure 23 and the document text below. The multi-lingual modeling extensions maintain and expand this approach, assuming that both digital signals and/or analog signals can move to and from the model unit. All VHDL-AMS and ...

... discussion, the IBIS circuit block is called a “model unit” in Figure 22 and Figure 23 and the document text below. The multi-lingual modeling extensions maintain and expand this approach, assuming that both digital signals and/or analog signals can move to and from the model unit. All VHDL-AMS and ...

MAX3984 1Gbps to 10Gbps Preemphasis Driver with Receive Equalizer General Description

... Supply voltage to reach 90% of final value in less than 100µs, but not less than 10µs. Power-on delay interval measured from the 50% level of the final voltage at the filter’s device side to 50% level of final current. The supply is to remain at or above 3V for at least 100ms. Only one full-scale tr ...

... Supply voltage to reach 90% of final value in less than 100µs, but not less than 10µs. Power-on delay interval measured from the 50% level of the final voltage at the filter’s device side to 50% level of final current. The supply is to remain at or above 3V for at least 100ms. Only one full-scale tr ...

HANDBOOK OF OPERATIONAL AMPLIFIER APPLICATIONS Application Report

... helpful to the experienced user of operational amplifiers, as well as the new user, in extending the range of potential applications in which these devices can be used to advantage. It is assumed that the reader will have a basic knowledge of electronics, but no particular knowledge of operational a ...

... helpful to the experienced user of operational amplifiers, as well as the new user, in extending the range of potential applications in which these devices can be used to advantage. It is assumed that the reader will have a basic knowledge of electronics, but no particular knowledge of operational a ...

Programmable Gain Amplifier (PGA)

... The PGA is used when an input signal has insufficient amplitude. You can put a PGA in front of a comparator, ADC, or mixer to increase the amplitude of the signal to these components. The PGA can be used as a unity gain amplifier to buffer the inputs of lower impedance blocks, including Mixers or in ...

... The PGA is used when an input signal has insufficient amplitude. You can put a PGA in front of a comparator, ADC, or mixer to increase the amplitude of the signal to these components. The PGA can be used as a unity gain amplifier to buffer the inputs of lower impedance blocks, including Mixers or in ...

Programmable Gain Amplifier (PGA)

... The PGA is used when an input signal has insufficient amplitude. You can put a PGA in front of a comparator, ADC, or mixer to increase the amplitude of the signal to these components. The PGA can be used as a unity gain amplifier to buffer the inputs of lower impedance blocks, including Mixers or in ...

... The PGA is used when an input signal has insufficient amplitude. You can put a PGA in front of a comparator, ADC, or mixer to increase the amplitude of the signal to these components. The PGA can be used as a unity gain amplifier to buffer the inputs of lower impedance blocks, including Mixers or in ...

RTH050.pdf

... The differential pedestal error is proportional to the input signal. For TH1 it corresponds to a track to hold gain ~ -0.17 dB. This gain loss may be observed at the DTH output if TH2 is in track mode during the TH1 track to hold transition. The variance of the hold noise is proportional to the hold ...

... The differential pedestal error is proportional to the input signal. For TH1 it corresponds to a track to hold gain ~ -0.17 dB. This gain loss may be observed at the DTH output if TH2 is in track mode during the TH1 track to hold transition. The variance of the hold noise is proportional to the hold ...

a 14-Bit 333 kSPS Serial A/D Converter AD7851

... Delay from SYNC↓ until DOUT Three-State Disabled Delay from SYNC↓ until DIN Three-State Disabled Data Access Time after SCLK↓ Data Setup Time prior to SCLK↑ Data Valid to SCLK Hold Time SCLK High Pulse Width (Interface Modes 4 and 5) SCLK Low Pulse Width (Interface Modes 4 and 5) SCLK↑ to SYNC↑ Hold ...

... Delay from SYNC↓ until DOUT Three-State Disabled Delay from SYNC↓ until DIN Three-State Disabled Data Access Time after SCLK↓ Data Setup Time prior to SCLK↑ Data Valid to SCLK Hold Time SCLK High Pulse Width (Interface Modes 4 and 5) SCLK Low Pulse Width (Interface Modes 4 and 5) SCLK↑ to SYNC↑ Hold ...

Chaper 5 - cs.csubak.edu

... As RC goes to infinity, the voltage gain reaches the product of gm and rO, which represents the maximum voltage gain the amplifier can have. The intrinsic gain is independent of the bias current. CH5 Bipolar Amplifiers ...

... As RC goes to infinity, the voltage gain reaches the product of gm and rO, which represents the maximum voltage gain the amplifier can have. The intrinsic gain is independent of the bias current. CH5 Bipolar Amplifiers ...

MAX9381 Lowest Power 3.0GHz ECL/PECL Differential Data and Clock D Flip-Flop General Description

... Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. ...

... Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. ...

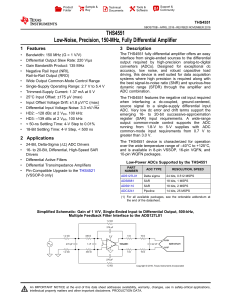

THS4551 Low-Noise, Precision, 150

... Added Input offset current drift parameter test conditions, minimum and maximum specifications, and test level value to second row................................................................................................................................................................ 7 ...

... Added Input offset current drift parameter test conditions, minimum and maximum specifications, and test level value to second row................................................................................................................................................................ 7 ...

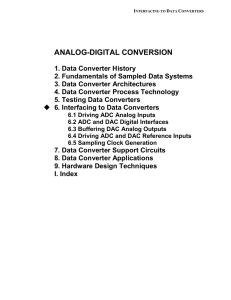

Chapter 6: Interfacing to Data Converters

... negative supply to within about 1 V of the positive supply. Over this common-mode range, amplifier input offset voltage, input bias current, CMR, input noise voltage/current are primarily determined by the characteristics of the PNP differential pair. At the crossover threshold, however, amplifier i ...

... negative supply to within about 1 V of the positive supply. Over this common-mode range, amplifier input offset voltage, input bias current, CMR, input noise voltage/current are primarily determined by the characteristics of the PNP differential pair. At the crossover threshold, however, amplifier i ...

MAX9320B 1:2 Differential PECL/ECL/LVPECL/LVECL Clock and Data Driver General Description

... systems with a nominal 3.3V or 5V supply. For differential ECL and LVECL operation, this device operates from a -3.0V to -5.5V supply. The MAX9320B is offered in industry-standard 8-pin TSSOP and SO packages. ...

... systems with a nominal 3.3V or 5V supply. For differential ECL and LVECL operation, this device operates from a -3.0V to -5.5V supply. The MAX9320B is offered in industry-standard 8-pin TSSOP and SO packages. ...

54006A Application Note

... Selecting the right probe for your application is the first step toward making reliable oscilloscope measurements. Although you can choose from a number of different types of oscilloscope probes, they fall into two major categories: passive and active. Passive probes do not require external probe po ...

... Selecting the right probe for your application is the first step toward making reliable oscilloscope measurements. Although you can choose from a number of different types of oscilloscope probes, they fall into two major categories: passive and active. Passive probes do not require external probe po ...

![[External Circuit] Package Models with](http://s1.studyres.com/store/data/001975732_1-25bfb7f424a2e0fe71cce5ca60376610-300x300.png)