Labham Gupta

... solve the system for the angles and to obtain the data set for the Artificial Neural Network training powered by five varying dc input sources. The output angles returned by the Artificial Neural Network may not provide a satisfactory result, or harmonic elimination, at some points as it generalizes ...

... solve the system for the angles and to obtain the data set for the Artificial Neural Network training powered by five varying dc input sources. The output angles returned by the Artificial Neural Network may not provide a satisfactory result, or harmonic elimination, at some points as it generalizes ...

POWER DEVICES AND INTEGRATED CIRCUITS

... required for implanting into SiC due to the higher density of SiC than Si. [12] While 3 to 500keV energy can implant boron, phosphorus or arsenic dopants into silicon by 100A to 1μm below the surface [10], creating μm-range implant depth in SiC often require energies in the MeV range. The masking la ...

... required for implanting into SiC due to the higher density of SiC than Si. [12] While 3 to 500keV energy can implant boron, phosphorus or arsenic dopants into silicon by 100A to 1μm below the surface [10], creating μm-range implant depth in SiC often require energies in the MeV range. The masking la ...

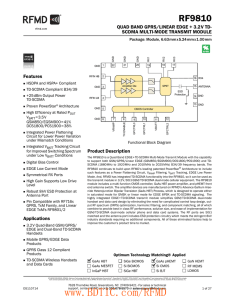

RF9810 QUAD BAND GPRS/LINEAR EDGE + 3.2V TD- SCDMA MULTI-MODE TRANSMIT MODULE

... RF9810 continues to build upon RFMD’s leading patented PowerStar® Architecture to include such features as a Power Flattening Circuit, VRAMP Filtering, VBATT Tracking, EDGE Low Power Mode. And, RFMD has integrated TD-SCDMA functionality into the RF9810, so it can be used as the transmit module in 3. ...

... RF9810 continues to build upon RFMD’s leading patented PowerStar® Architecture to include such features as a Power Flattening Circuit, VRAMP Filtering, VBATT Tracking, EDGE Low Power Mode. And, RFMD has integrated TD-SCDMA functionality into the RF9810, so it can be used as the transmit module in 3. ...

Planar Mosaic Architectural Displays

... Off-board, rack-mountable units can be located at a distance from the video wall. Power cables can be daisy-chained through a group of tiles, eliminating the need for power outlets behind each tile. Each power supply module can support up to 16 tiles, depending on the mix of tile sizes. A redundant ...

... Off-board, rack-mountable units can be located at a distance from the video wall. Power cables can be daisy-chained through a group of tiles, eliminating the need for power outlets behind each tile. Each power supply module can support up to 16 tiles, depending on the mix of tile sizes. A redundant ...

ETRX358x ZIGBEE® MODULES PRODUCT MANUAL

... ETRX358X OEM Responsibilities The ETRX358x and ETRX358x families of module have been certified for integration into products only by OEM integrators under the following condition: 1. The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter. As ...

... ETRX358X OEM Responsibilities The ETRX358x and ETRX358x families of module have been certified for integration into products only by OEM integrators under the following condition: 1. The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter. As ...

ES_LPC2103 Errata sheet LPC2103 Rev. 2 — 1 March 2011 Errata sheet

... From the Vdd1V8 pin to the ARM7 core, there is a voltage drop. This voltage drop increases with higher currents (or higher power consumption). Higher system frequency and/or faster peripherals increase power consumption thereby increasing the voltage drop from the Vdd1V8 pin to the core. Problem: Un ...

... From the Vdd1V8 pin to the ARM7 core, there is a voltage drop. This voltage drop increases with higher currents (or higher power consumption). Higher system frequency and/or faster peripherals increase power consumption thereby increasing the voltage drop from the Vdd1V8 pin to the core. Problem: Un ...

Electrical Installations Level 2 - Pearson Schools and FE Colleges

... vital that from the start of your career you are able to put together basic circuitry. This requires knowledge of all parts of the electrical circuit, from the source of supply to the load. This chapter will cover the various wiring systems, enclosures and equipment you will need to become familiar ...

... vital that from the start of your career you are able to put together basic circuitry. This requires knowledge of all parts of the electrical circuit, from the source of supply to the load. This chapter will cover the various wiring systems, enclosures and equipment you will need to become familiar ...

FDMS3664S PowerTrench Power Stage

... 3. Output inductor location should be as close as possible to the Power Stage device for lower power loss due to copper trace resistance. A shorter and wider PHASE trace to the inductor reduces the conduction loss. Preferably the Power Stage should be directly in line (as shown in figure 31) with th ...

... 3. Output inductor location should be as close as possible to the Power Stage device for lower power loss due to copper trace resistance. A shorter and wider PHASE trace to the inductor reduces the conduction loss. Preferably the Power Stage should be directly in line (as shown in figure 31) with th ...

EL2001 Tech Sheet - Balboa Water Group

... Persistent Memory is not used for Time of Day. Time of Day needs to be “kept running” (not just stored) while the power is off, so a separate Real Time Clock feature (on all models except the EL1000) keeps track of Time of Day while the unit is off. Time of Day Retention, and Time of Day Retention a ...

... Persistent Memory is not used for Time of Day. Time of Day needs to be “kept running” (not just stored) while the power is off, so a separate Real Time Clock feature (on all models except the EL1000) keeps track of Time of Day while the unit is off. Time of Day Retention, and Time of Day Retention a ...

PDF - This Chapter

... the bonding and grounding receptacles on the router chassis. Six chassis grounding points are provided at the rear (MSC) side of the chassis. Each side of the chassis has one pair of threaded ground studs located on the inside of the chassis and two sets of grounding receptacles located on the outsi ...

... the bonding and grounding receptacles on the router chassis. Six chassis grounding points are provided at the rear (MSC) side of the chassis. Each side of the chassis has one pair of threaded ground studs located on the inside of the chassis and two sets of grounding receptacles located on the outsi ...

Balboa EL2001 Mach 3 v30 Hot Sheet

... Persistent Memory is not used for Time of Day. Time of Day needs to be “kept running” (not just stored) while the power is off, so a separate Real Time Clock feature (on all models except the EL1000) keeps track of Time of Day while the unit is off. Time of Day Retention, and Time of Day Retention a ...

... Persistent Memory is not used for Time of Day. Time of Day needs to be “kept running” (not just stored) while the power is off, so a separate Real Time Clock feature (on all models except the EL1000) keeps track of Time of Day while the unit is off. Time of Day Retention, and Time of Day Retention a ...

2002 NEC Code Changes

... Secondary conductors considered protected if calculations made under engineering supervision determine that the system overcurrent devices will protect the conductors within the recognized time-current limits for ALL shortcircuit and ground-fault conditions. Secondary conductor length ...

... Secondary conductors considered protected if calculations made under engineering supervision determine that the system overcurrent devices will protect the conductors within the recognized time-current limits for ALL shortcircuit and ground-fault conditions. Secondary conductor length ...

Cmos Scaling Into The Nanometer Regime

... scaling, as can be seen in a plot of the normalized inverter delay versus in Fig. 9 [16]. Since cannot be reduced below 0.3 V and since CMOS delay increases rapidly when , there is very little performance to gain by scaling the power supply voltage to significantly below 1 V. Another problem that go ...

... scaling, as can be seen in a plot of the normalized inverter delay versus in Fig. 9 [16]. Since cannot be reduced below 0.3 V and since CMOS delay increases rapidly when , there is very little performance to gain by scaling the power supply voltage to significantly below 1 V. Another problem that go ...

A Low-Impedance, Sub-Bandgap 0.6μm CMOS Reference with 0.84

... variations, can be a considerable source of error because it translates directly into an error in the reference voltage. The substrate PNP-based CMOS references proposed in [12]-[15] employ DEM to eliminate the effect of device mismatch and consequently leave a residual error in VREF of 3-10mV that ...

... variations, can be a considerable source of error because it translates directly into an error in the reference voltage. The substrate PNP-based CMOS references proposed in [12]-[15] employ DEM to eliminate the effect of device mismatch and consequently leave a residual error in VREF of 3-10mV that ...

FDMS3669S PowerTrench Power Stage

... 3. Output inductor location should be as close as possible to the Power Stage device for lower power loss due to copper trace resistance. A shorter and wider PHASE trace to the inductor reduces the conduction loss. Preferably the Power Stage should be directly in line (as shown in figure 31) with th ...

... 3. Output inductor location should be as close as possible to the Power Stage device for lower power loss due to copper trace resistance. A shorter and wider PHASE trace to the inductor reduces the conduction loss. Preferably the Power Stage should be directly in line (as shown in figure 31) with th ...

Expl_Sw_chapter_02_Switches_Part_I

... • Auto-negotiation of duplex mode. The two ports communicate to determine the best mode. • Auto-negotiation can produce unpredictable results. • If auto-negotiation fails because the attached device does not support it, the Catalyst switch defaults the switch port to half-duplex mode. • Half-duplex ...

... • Auto-negotiation of duplex mode. The two ports communicate to determine the best mode. • Auto-negotiation can produce unpredictable results. • If auto-negotiation fails because the attached device does not support it, the Catalyst switch defaults the switch port to half-duplex mode. • Half-duplex ...

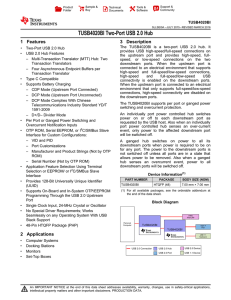

TUSB4020BI Two-Port USB 2.0 Hub (Rev. A)

... TUSB4020BI using PWRCTL[2:1]/BATEN[2:1]. When SMBus mode is enabled using SMBUSz, this terminal sets the value of the SMBus slave address bit 1. SMBus slave address bit 3 is always 1 for the TUSB4020BI. Can be left unconnected if full power management and SMBus are not implemented. After reset, this ...

... TUSB4020BI using PWRCTL[2:1]/BATEN[2:1]. When SMBus mode is enabled using SMBUSz, this terminal sets the value of the SMBus slave address bit 1. SMBus slave address bit 3 is always 1 for the TUSB4020BI. Can be left unconnected if full power management and SMBus are not implemented. After reset, this ...

Fieldbus Non-Incendive Concept takes FISCO into Zone 2 and

... introduction of FISCO – the Fieldbus Intrinsic Safety Concept. When compared with intrinsically safe fieldbus systems installed according to the conventional, “Entity” concept, FISCO simplifies the rules that govern energy storage in field cables, and makes more power available to the fieldbus trunk ...

... introduction of FISCO – the Fieldbus Intrinsic Safety Concept. When compared with intrinsically safe fieldbus systems installed according to the conventional, “Entity” concept, FISCO simplifies the rules that govern energy storage in field cables, and makes more power available to the fieldbus trunk ...

7050SX Data Sheet

... 1/10G SFP+ based ports and 10/40G ports using QSFP+ for flexible configurations supporting migration from 1/10G to 10/40G networks. All models in the 7050SX Series delivers rich layer 2 and layer 3 features with wire speed performance up to a maximum performance of 2.56Tbps. The Arista 7050SX switch ...

... 1/10G SFP+ based ports and 10/40G ports using QSFP+ for flexible configurations supporting migration from 1/10G to 10/40G networks. All models in the 7050SX Series delivers rich layer 2 and layer 3 features with wire speed performance up to a maximum performance of 2.56Tbps. The Arista 7050SX switch ...

Power over Ethernet

Power over Ethernet or PoE describes any of several standardized or ad-hoc systems which pass electrical power along with data on Ethernet cabling. This allows a single cable to provide both data connection and electrical power to devices such as wireless access points or IP cameras. Unlike standards such as Universal Serial Bus which also power devices over the data cables, PoE allows long cable lengths. Power may be carried on the same conductors as the data, or it may be carried on dedicated conductors in the same cable.There are several common techniques for transmitting power over Ethernet cabling. Two of them have been standardized by IEEE 802.3. Since only two of the four pairs are needed for 10BASE-T or 100BASE-TX, power may be transmitted on the unused conductors of a cable. In the IEEE standards, this is referred to as Alternative B. Power may also be transmitted on the data conductors by applying a common-mode voltage to each pair. Because twisted-pair Ethernet uses differential signalling, this does not interfere with data transmission. The common mode voltage is easily extracted using the center tap of the standard Ethernet pulse transformer. This is similar to the phantom power technique commonly used for powering audio microphones. In the IEEE standards, this is referred to as Alternative A.In addition to standardizing existing practice for spare-pair and common-mode data pair power transmission, the IEEE PoE standards provide for signalling between the power sourcing equipment (PSE) and powered device (PD). This signaling allows the presence of a conformant device to be detected by the power source, and allows the device and source to negotiate the amount of power required or available. Up to a 25.5 watts is available for a device.