MAX5550 Dual, 10-Bit, Programmable, 30mA High-Output-Current DAC General Description

... data into or out of the DAC register. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are read as control signals (see the START and STOP Conditions section). Both SDA and SCL idle high. START and STOP Conditions The master initiates ...

... data into or out of the DAC register. The data on SDA must remain stable during the high period of the SCL clock pulse. Changes in SDA while SCL is high are read as control signals (see the START and STOP Conditions section). Both SDA and SCL idle high. START and STOP Conditions The master initiates ...

A Modified Control Method For A Dual Unified Power Quality

... The Current loop transfer function is represented as ...

... The Current loop transfer function is represented as ...

SP232A 数据资料DataSheet下载

... capacitors should be mounted as close as possible to the IC and have a low ESR (equivalent series resistance). Inexpensive, surface mount ceramic capacitors are ideal for use on charge pump. If polarized capacitors are used the positive and negative terminals should be connected as shown on the typi ...

... capacitors should be mounted as close as possible to the IC and have a low ESR (equivalent series resistance). Inexpensive, surface mount ceramic capacitors are ideal for use on charge pump. If polarized capacitors are used the positive and negative terminals should be connected as shown on the typi ...

ICS552-02 L S 2 I

... External Components A minimum number of external components are required for proper operation. Decoupling capacitors of 0.01 µF should be connected between VDD on pin 2 and GND on pin 7, and between VDD on pin 15 and GND on pin 10, as close to the device as possible. A 33 Ω series terminating resist ...

... External Components A minimum number of external components are required for proper operation. Decoupling capacitors of 0.01 µF should be connected between VDD on pin 2 and GND on pin 7, and between VDD on pin 15 and GND on pin 10, as close to the device as possible. A 33 Ω series terminating resist ...

Design Solutions 10 - Active Voltage Positioning Reduces Output Capacitors

... is 0.8V and VOUT is set for 1.6V, so ∆VOUT = 2 • ∆VFB = 116mV. The peak-to-peak ripple voltage will add to this. The resulting transient response is shown in Figure 1b. The transient performance has been improved, while using fewer output capacitors. The optimal amount of AVP offset is equal to ∆I • ...

... is 0.8V and VOUT is set for 1.6V, so ∆VOUT = 2 • ∆VFB = 116mV. The peak-to-peak ripple voltage will add to this. The resulting transient response is shown in Figure 1b. The transient performance has been improved, while using fewer output capacitors. The optimal amount of AVP offset is equal to ∆I • ...

Chapter 3 VOLTAGE CONTROL

... In DC excitation system, the field of the main synchronous generator is fed from a DC generator, called exciter. Since the field of the synchronous generator is in the rotor, the required field current is supplied to it through slip rings and brushes. The DC generator is driven from the same turbine ...

... In DC excitation system, the field of the main synchronous generator is fed from a DC generator, called exciter. Since the field of the synchronous generator is in the rotor, the required field current is supplied to it through slip rings and brushes. The DC generator is driven from the same turbine ...

fault diagnosis of vsi fed induction motor drive using fuzzy

... are unavoidable. Early detection of these abnormal disturbances helps in avoiding the severe failures in the system. This helps the electrical drive system to reduce maintenance cost and unscheduled downtimes which impact more on the production and financial income loss. Modern industry has widely u ...

... are unavoidable. Early detection of these abnormal disturbances helps in avoiding the severe failures in the system. This helps the electrical drive system to reduce maintenance cost and unscheduled downtimes which impact more on the production and financial income loss. Modern industry has widely u ...

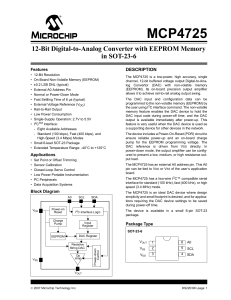

12-Bit DAC with EEPROM Memory in SOT-23-6

... programmed to the non-volatile memory (EEPROM) by the user using I2C interface command. The non-volatile memory feature enables the DAC device to hold the DAC input code during power-off time, and the DAC output is available immediately after power-up. This feature is very useful when the DAC device ...

... programmed to the non-volatile memory (EEPROM) by the user using I2C interface command. The non-volatile memory feature enables the DAC device to hold the DAC input code during power-off time, and the DAC output is available immediately after power-up. This feature is very useful when the DAC device ...

2 3 Relay Module SAFETY MANUAL SIL

... It is assumed that any safe failures that occur (e.g., output in safe condition) will be corrected within eight hours (e.g., correction of a sensor fault). While the device is being repaired, measures must be taken to maintain the safety function (e.g., by using a replacement device). The indication ...

... It is assumed that any safe failures that occur (e.g., output in safe condition) will be corrected within eight hours (e.g., correction of a sensor fault). While the device is being repaired, measures must be taken to maintain the safety function (e.g., by using a replacement device). The indication ...

TB67S105FTG Usage considerations

... The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead to smoke or ignition. To mini ...

... The IC will fully break down when used under conditions that exceed its absolute maximum ratings, when the wiring is routed improperly or when an abnormal pulse noise occurs from the wiring or load, causing a large current to continuously flow and the breakdown can lead to smoke or ignition. To mini ...

DAC8554 数据资料 dataSheet 下载

... device supports a standard 3-wire serial interface capable of operating with input data clock frequencies up to 50MHz for IOVDD = 5V. The DAC8554 requires an external reference voltage to set the output range of each DAC channel. Also incorporated into the device is a power-on reset circuit which en ...

... device supports a standard 3-wire serial interface capable of operating with input data clock frequencies up to 50MHz for IOVDD = 5V. The DAC8554 requires an external reference voltage to set the output range of each DAC channel. Also incorporated into the device is a power-on reset circuit which en ...

A 10Gb/s wide-band current-mode logic I/O interface for high

... feedback DC offset canceling network. Every amplifier gain stage is composed by CML gain stage circuit that includes pull-up resistors in order to get larger voltage gain. To achieve the required higher bandwidth, current-mode logic gain stage also incorporates active feedback and negative Miller ca ...

... feedback DC offset canceling network. Every amplifier gain stage is composed by CML gain stage circuit that includes pull-up resistors in order to get larger voltage gain. To achieve the required higher bandwidth, current-mode logic gain stage also incorporates active feedback and negative Miller ca ...

$doc.title

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

... obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment. TI warrants performance of its hardware products to the speci ...

Lab 4 - Simple Op

... of the output signal begin to be flattened due to output saturation. Record the value of resistance where this happens. Now increase the feedback resistance to 99kΩ. Describe and draw waveforms in your notebook. What is the theoretical gain at this point? How small would the input signal have to be ...

... of the output signal begin to be flattened due to output saturation. Record the value of resistance where this happens. Now increase the feedback resistance to 99kΩ. Describe and draw waveforms in your notebook. What is the theoretical gain at this point? How small would the input signal have to be ...

74VCX162373 Low Voltage 16-Bit Transparent Latch with 3.6V Tolerant Inputs and Outputs

... appear to be transparent to the data when the Latch enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state. The VCX162373 is also designed with 26: resi ...

... appear to be transparent to the data when the Latch enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state. The VCX162373 is also designed with 26: resi ...