MAX1875/MAX1876 Dual 180° Out-of-Phase PWM Step- Down Controllers with POR General Description

... 600kHz with an external resistor. Alternatively, the controller can be synchronized to an external clock generated to another MAX1875/MAX1876 or a system clock. One MAX1875/MAX1876 can be set to generate an inphase, or 90° out-of-phase, clock signal for synchronization with additional controllers. T ...

... 600kHz with an external resistor. Alternatively, the controller can be synchronized to an external clock generated to another MAX1875/MAX1876 or a system clock. One MAX1875/MAX1876 can be set to generate an inphase, or 90° out-of-phase, clock signal for synchronization with additional controllers. T ...

450W Power Supply Hardware v1.0 Author: Pierluigi Sarti, Technical Lead, Power

... series to the hot conductor (Line). The fuse is rated 5A "slow blow" type and never trips during inrush or any AC input current transients the power supply is designed to stand in normal operations. The fuse is a safety-approved component with a rating of at least 305VAC RMS, and 5 x 20 [mm] of mini ...

... series to the hot conductor (Line). The fuse is rated 5A "slow blow" type and never trips during inrush or any AC input current transients the power supply is designed to stand in normal operations. The fuse is a safety-approved component with a rating of at least 305VAC RMS, and 5 x 20 [mm] of mini ...

Features

... FPGAs. We can support within one ULC from 18 Kbits to 390 Kbits DPRAM and from 46 Kgates to 780 Kgates. Typically, ULC die size is 50% smaller than the equivalent FPGA die size. DPRAM blocks are compatible with Xilinx or Altera FPGA blocks. Devices are implemented in high–performance CMOS technology ...

... FPGAs. We can support within one ULC from 18 Kbits to 390 Kbits DPRAM and from 46 Kgates to 780 Kgates. Typically, ULC die size is 50% smaller than the equivalent FPGA die size. DPRAM blocks are compatible with Xilinx or Altera FPGA blocks. Devices are implemented in high–performance CMOS technology ...

UNITED STATES NUCLEAR REGULATORY COMMISSION OFFICE OF NUCLEAR REACTOR REGULATION WASHINGTON, DC 20555-0001

... power system can lead to or cause the failure of redundant Class 1E safety-related electrical equipment, the NRC requested that licensees install degraded voltage protection schemes (second level of voltage protection (Degraded Voltage Relays (DVRs)) for the station electric power system) as describ ...

... power system can lead to or cause the failure of redundant Class 1E safety-related electrical equipment, the NRC requested that licensees install degraded voltage protection schemes (second level of voltage protection (Degraded Voltage Relays (DVRs)) for the station electric power system) as describ ...

Lecture 5: Fault Modeling

... Potentially-detectable fault -- Test produces an unknown (X) state at primary output (PO); detection is probabilistic, usually with 50% probability. Initialization fault -- Fault prevents initialization of the faulty circuit; can be detected as a potentially-detectable fault. Hyperactive fault -- Fa ...

... Potentially-detectable fault -- Test produces an unknown (X) state at primary output (PO); detection is probabilistic, usually with 50% probability. Initialization fault -- Fault prevents initialization of the faulty circuit; can be detected as a potentially-detectable fault. Hyperactive fault -- Fa ...

AD823 Dual 16 MHz, Rail-to-Rail FET Input Amplifier Data Sheet

... outstanding load drive capability, results in an exceptionally versatile amplifier for applications such as A/D drivers, high speed active filters, and other low voltage, high dynamic range systems. The AD823 is available over the industrial temperature range of −40°C to +85°C and is offered in both ...

... outstanding load drive capability, results in an exceptionally versatile amplifier for applications such as A/D drivers, high speed active filters, and other low voltage, high dynamic range systems. The AD823 is available over the industrial temperature range of −40°C to +85°C and is offered in both ...

Circuit models for a..

... Just three values describe all! In addition, each equivalent circuit model uses the same two impedance values— the input impedance Z in and output impedance Zout . Q: So what are these models good for? A: Say we wish to analyze a circuit in which an amplifier is but one component. Instead of needing ...

... Just three values describe all! In addition, each equivalent circuit model uses the same two impedance values— the input impedance Z in and output impedance Zout . Q: So what are these models good for? A: Say we wish to analyze a circuit in which an amplifier is but one component. Instead of needing ...

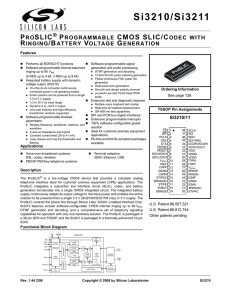

Si3210/Si3211

... The ProSLIC® is a low-voltage CMOS device that provides a complete analog telephone interface ideal for customer premise equipment (CPE) applications. The ProSLIC integrates a subscriber line interface circuit (SLIC), codec, and battery generation functionality into a single CMOS integrated circuit. ...

... The ProSLIC® is a low-voltage CMOS device that provides a complete analog telephone interface ideal for customer premise equipment (CPE) applications. The ProSLIC integrates a subscriber line interface circuit (SLIC), codec, and battery generation functionality into a single CMOS integrated circuit. ...

Current Shunt Monitor -16V to +80V Common

... In the Typical Characteristics, the Output Error vs Common-Mode Voltage curve (Figure 6) shows the highest accuracy for this region of operation. In this plot, VS = 12V; for VCM ≥ 12V, the output error is at its minimum. This case is also used to create the VSENSE ≥ 20mV output specifications in the ...

... In the Typical Characteristics, the Output Error vs Common-Mode Voltage curve (Figure 6) shows the highest accuracy for this region of operation. In this plot, VS = 12V; for VCM ≥ 12V, the output error is at its minimum. This case is also used to create the VSENSE ≥ 20mV output specifications in the ...

ics85104i.pdf

... NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential cross points. NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature, and with equal load conditions. Us ...

... NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the output differential cross points. NOTE 3: Defined as skew between outputs on different devices operating at the same supply voltage, same temperature, and with equal load conditions. Us ...

quadrature clock converter

... Input for external component connection. A resistor connected between this input and VSS adjusts the output clock pulse width (Tow). For proper operation, the output clock pulse width must be less than or equal to the A,B pulse separation (TOW≤TPS). ...

... Input for external component connection. A resistor connected between this input and VSS adjusts the output clock pulse width (Tow). For proper operation, the output clock pulse width must be less than or equal to the A,B pulse separation (TOW≤TPS). ...

MC14043B - CMOS MSI

... ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ...

... ON Semiconductor and the are registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ...

Junction Field Effect Transistor (JFET)

... ¾ The voltage applied to the drain will be designated vDD. Note that in some other texts and literature this is referred to as vDS. ¾ The voltage applied to the gate will be designated vGG. Note that in some other texts and literature this is referred to as vGS. The n-channel JFET connected to the v ...

... ¾ The voltage applied to the drain will be designated vDD. Note that in some other texts and literature this is referred to as vDS. ¾ The voltage applied to the gate will be designated vGG. Note that in some other texts and literature this is referred to as vGS. The n-channel JFET connected to the v ...

MAX1637 Miniature, Low-Voltage, Precision Step-Down Controller General Description

... (SMPS) controller designed primarily for buck-topology regulators in battery-powered applications where high efficiency and low quiescent supply current are critical. Light-load efficiency is enhanced by automatic idlemode operation—a variable-frequency, pulse-skipping mode that reduces transition a ...

... (SMPS) controller designed primarily for buck-topology regulators in battery-powered applications where high efficiency and low quiescent supply current are critical. Light-load efficiency is enhanced by automatic idlemode operation—a variable-frequency, pulse-skipping mode that reduces transition a ...

STLC3075

... is based on a SLIC core, on purpose optimized for these applications, with the addition of a DC/DC converter controller to meet the WLL and ISDN-TA design requirements. The SLIC performs the standard feeding, signalling and transmission functions. STLC3075 can be set in three different operating mod ...

... is based on a SLIC core, on purpose optimized for these applications, with the addition of a DC/DC converter controller to meet the WLL and ISDN-TA design requirements. The SLIC performs the standard feeding, signalling and transmission functions. STLC3075 can be set in three different operating mod ...

x8407_projects

... 2.1) f m 60 Hz , f cr 900 Hz and m a 1 .0 2.2) f m 20 Hz , f cr 900 Hz and ma 0.3 Show simulated waveforms ( v g 1 , v g 2 , v AN , v AB , and i A ) and the harmonic spectra of v AB and i A . Arrange your waveforms and harmonic spectra in a same format as that of Fig. 8.6-2 in textbook. ...

... 2.1) f m 60 Hz , f cr 900 Hz and m a 1 .0 2.2) f m 20 Hz , f cr 900 Hz and ma 0.3 Show simulated waveforms ( v g 1 , v g 2 , v AN , v AB , and i A ) and the harmonic spectra of v AB and i A . Arrange your waveforms and harmonic spectra in a same format as that of Fig. 8.6-2 in textbook. ...

AD1955 数据手册DataSheet下载

... Register 0 Bits 12 and 13, the left channel data field always precedes the right channel data field. The serial data format and word length in PCM Mode are set by the mode select bits (Bits 4 and 5 and Bits 2 and 3, respectively) in the SPI control register. In all data formats except for the Right- ...

... Register 0 Bits 12 and 13, the left channel data field always precedes the right channel data field. The serial data format and word length in PCM Mode are set by the mode select bits (Bits 4 and 5 and Bits 2 and 3, respectively) in the SPI control register. In all data formats except for the Right- ...