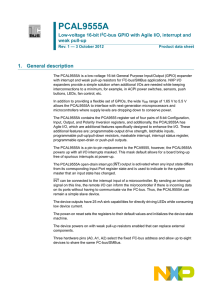

Data Sheet - NXP Semiconductors

... To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://www.freescale.com The following revision history table summari ...

... To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to: http://www.freescale.com The following revision history table summari ...

TMS320C5515 Fixed-Point Digital Signal Processor (Rev. F)

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

TMS320C5505 Fixed-Point Digital Signal Processor (Rev. F)

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

ADE7978/ADE7933/ADE7932

... SPI and I2C, can be used to communicate with the ADE7978. A dedicated high speed interface—the high speed data capture (HSDC) port—can be used in conjunction with I2C to provide access to the ADC outputs and real-time power information. The ADE7978 also has two interrupt request pins, IRQ0 and IRQ1, ...

... SPI and I2C, can be used to communicate with the ADE7978. A dedicated high speed interface—the high speed data capture (HSDC) port—can be used in conjunction with I2C to provide access to the ADC outputs and real-time power information. The ADE7978 also has two interrupt request pins, IRQ0 and IRQ1, ...

TMS320C5514 Fixed-Point Digital Signal Processor (Rev. G)

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

... The fixed-point DSP is based on the TMS320C55x™ DSP generation CPU processor core. The C55x™ DSP architecture achieves high performance and low power through increased parallelism and total focus on power savings. The CPU supports an internal bus structure that is composed of one program bus, one 32 ...

ADE7880 (Rev. B)

... The ADE7880 is suitable for measuring active, reactive, and apparent energy in various 3-phase configurations, such as wye or delta services with, both, three and four wires. The ADE7880 provides system calibration features for each phase, that is, rms offset correction, phase calibration, and gain ...

... The ADE7880 is suitable for measuring active, reactive, and apparent energy in various 3-phase configurations, such as wye or delta services with, both, three and four wires. The ADE7880 provides system calibration features for each phase, that is, rms offset correction, phase calibration, and gain ...

MC68HC705 microcontroller

... Appendix A. MC68HRC705J1A . . . . . . . . . . . . . . . . . . . 137 Appendix B. MC68HSC705J1A . . . . . . . . . . . . . . . . . . . 141 Appendix C. MC68HSR705J1A . . . . . . . . . . . . . . . . . . . 145 ...

... Appendix A. MC68HRC705J1A . . . . . . . . . . . . . . . . . . . 137 Appendix B. MC68HSC705J1A . . . . . . . . . . . . . . . . . . . 141 Appendix C. MC68HSR705J1A . . . . . . . . . . . . . . . . . . . 145 ...

PCAL6416A

... There are two supply voltages for PCAL6416A: VDD(I2C-bus) and VDD(P). VDD(I2C-bus) provides the supply voltage for the interface at the master side (for example, a microcontroller) and the VDD(P) provides the supply for core circuits and Port P. The bidirectional voltage level translation in the PCA ...

... There are two supply voltages for PCAL6416A: VDD(I2C-bus) and VDD(P). VDD(I2C-bus) provides the supply voltage for the interface at the master side (for example, a microcontroller) and the VDD(P) provides the supply for core circuits and Port P. The bidirectional voltage level translation in the PCA ...

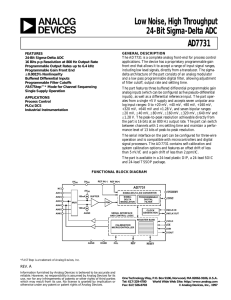

a Low Noise, High Throughput 24-Bit Sigma-Delta ADC AD7731

... The AD7731 is a complete analog front-end for process control applications. The device has a proprietary programmable gain front end that allows it to accept a range of input signal ranges, including low level signals, directly from a transducer. The sigmadelta architecture of the part consists of a ...

... The AD7731 is a complete analog front-end for process control applications. The device has a proprietary programmable gain front end that allows it to accept a range of input signal ranges, including low level signals, directly from a transducer. The sigmadelta architecture of the part consists of a ...

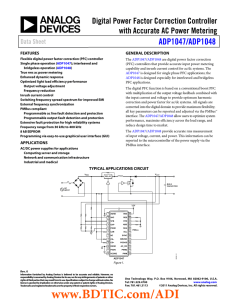

ADP1048 数据手册DataSheet 下载

... ADP1047 is designed for single phase PFC applications; the ADP1048 is designed especially for interleaved and bridgeless PFC applications. The digital PFC function is based on a conventional boost PFC with multiplication of the output voltage feedback combined with the input current and voltage to p ...

... ADP1047 is designed for single phase PFC applications; the ADP1048 is designed especially for interleaved and bridgeless PFC applications. The digital PFC function is based on a conventional boost PFC with multiplication of the output voltage feedback combined with the input current and voltage to p ...

PCAL9535A 1. General description Low-voltage 16-bit I

... The input latch registers (registers 44 and 45) enable and disable the input latch of the I/O pins. These registers are effective only when the pin is configured as an input port. When an input latch register bit is 0, the corresponding input pin state is not latched. A state change of the correspon ...

... The input latch registers (registers 44 and 45) enable and disable the input latch of the I/O pins. These registers are effective only when the pin is configured as an input port. When an input latch register bit is 0, the corresponding input pin state is not latched. A state change of the correspon ...

PCAL9555A 1. General description Low-voltage 16-bit I

... INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I2C-bus. Thus, the PCAL9555A can remain a simple slave device. The ...

... INT can be connected to the interrupt input of a microcontroller. By sending an interrupt signal on this line, the remote I/O can inform the microcontroller if there is incoming data on its ports without having to communicate via the I2C-bus. Thus, the PCAL9555A can remain a simple slave device. The ...

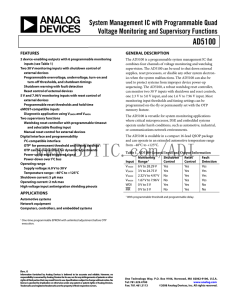

AD5100 数据手册DataSheet 下载

... The AD5100 is a programmable system management IC that combines four channels of voltage monitoring and watchdog supervision. The AD5100 can be used to shut down external supplies, reset processors, or disable any other system electronics when the system malfunctions. The AD5100 can also be used to ...

... The AD5100 is a programmable system management IC that combines four channels of voltage monitoring and watchdog supervision. The AD5100 can be used to shut down external supplies, reset processors, or disable any other system electronics when the system malfunctions. The AD5100 can also be used to ...

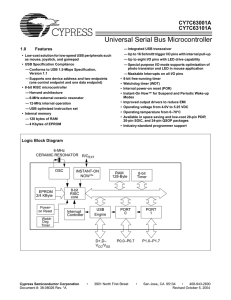

Universal Serial Bus Microcontroller

... The CY7C630/101A is a family of 8-bit RISC One Time Programmable (OTP) microcontrollers with a built-in 1.5-Mbps USB Serial Interface Engine (SIE). The microcontroller features 35 instructions that are optimized for USB applications. In addition, the microcontroller features 128 bytes of internal RA ...

... The CY7C630/101A is a family of 8-bit RISC One Time Programmable (OTP) microcontrollers with a built-in 1.5-Mbps USB Serial Interface Engine (SIE). The microcontroller features 35 instructions that are optimized for USB applications. In addition, the microcontroller features 128 bytes of internal RA ...

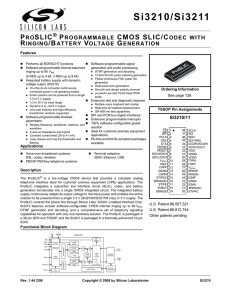

Si3210/Si3211

... The ProSLIC® is a low-voltage CMOS device that provides a complete analog telephone interface ideal for customer premise equipment (CPE) applications. The ProSLIC integrates a subscriber line interface circuit (SLIC), codec, and battery generation functionality into a single CMOS integrated circuit. ...

... The ProSLIC® is a low-voltage CMOS device that provides a complete analog telephone interface ideal for customer premise equipment (CPE) applications. The ProSLIC integrates a subscriber line interface circuit (SLIC), codec, and battery generation functionality into a single CMOS integrated circuit. ...

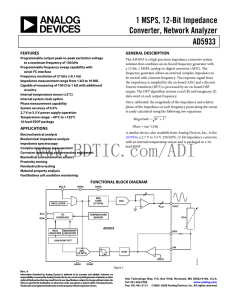

AD5933 英文数据手册DataSheet 下载

... tF, fall time of SCL and SDA when transmitting tF, fall time of SDA when receiving (CMOS compatible) tF, fall time of SDA when receiving tF, fall time of SCL and SDA when transmitting Capacitive load for each bus line ...

... tF, fall time of SCL and SDA when transmitting tF, fall time of SDA when receiving (CMOS compatible) tF, fall time of SDA when receiving tF, fall time of SCL and SDA when transmitting Capacitive load for each bus line ...

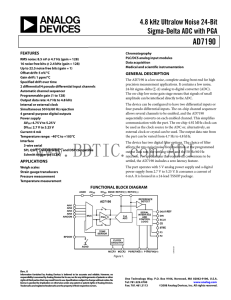

AD7190 数据手册DataSheet下载

... CS falling edge to SCLK active edge setup time4 Data valid to SCLK edge setup time Data valid to SCLK edge hold time CS rising edge to SCLK edge hold time ...

... CS falling edge to SCLK active edge setup time4 Data valid to SCLK edge setup time Data valid to SCLK edge hold time CS rising edge to SCLK edge hold time ...

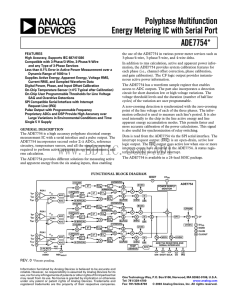

ADE7754 数据手册DataSheet 下载

... each phase (i.e., channel offset correction, phase calibration, and gain calibration). The CF logic output provides instantaneous active power information. The ADE7754 has a waveform sample register that enables access to ADC outputs. The part also incorporates a detection circuit for short duration ...

... each phase (i.e., channel offset correction, phase calibration, and gain calibration). The CF logic output provides instantaneous active power information. The ADE7754 has a waveform sample register that enables access to ADC outputs. The part also incorporates a detection circuit for short duration ...

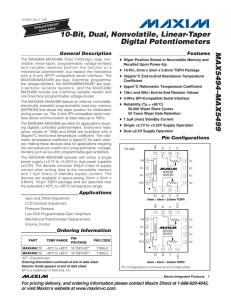

MAX5494–MAX5499 10-Bit, Dual, Nonvolatile, Linear-Taper Digital Potentiometers General Description

... The MAX5494–MAX5499 feature an internal, nonvolatile, electrically erasable programmable read-only memory (EEPROM) that stores the wiper position for initialization during power-up. The 3-wire SPI-compatible serial interface allows communication at data rates up to 7MHz. ...

... The MAX5494–MAX5499 feature an internal, nonvolatile, electrically erasable programmable read-only memory (EEPROM) that stores the wiper position for initialization during power-up. The 3-wire SPI-compatible serial interface allows communication at data rates up to 7MHz. ...

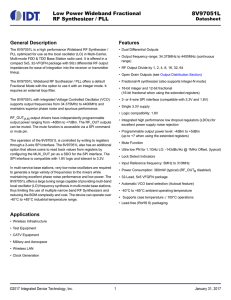

8V97051L Datasheet - Integrated Device Technology

... The operation of the 8V97051L is controlled by writing to registers through a 3-wire SPI interface. The 8V97051L also has an additional option that allows users to read back values from registers by configuring the MUX_OUT pin as a SDO for the SPI interface. The SPI interface is compatible with 1.8V ...

... The operation of the 8V97051L is controlled by writing to registers through a 3-wire SPI interface. The 8V97051L also has an additional option that allows users to read back values from registers by configuring the MUX_OUT pin as a SDO for the SPI interface. The SPI interface is compatible with 1.8V ...

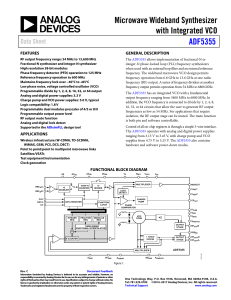

ADF5355 - Analog Devices

... integer-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference frequency. The wideband microwave VCO design permits frequency operation from 6.8 GHz to 13.6 GHz at one radio frequency (RF) output. A series of frequency dividers at another fr ...

... integer-N phase-locked loop (PLL) frequency synthesizers when used with an external loop filter and an external reference frequency. The wideband microwave VCO design permits frequency operation from 6.8 GHz to 13.6 GHz at one radio frequency (RF) output. A series of frequency dividers at another fr ...

Realtek RTL8201(F/FL/FN)-VB-CG DataSheet 1.4

... ©2011 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp. ...

... ©2011 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp. ...

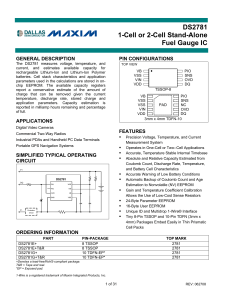

DS2781 - Maxim Part Number Search

... mode. While in ACTIVE mode, the DS2781 is fully functional with measurements and capacity estimation continuously updated. In SLEEP mode, the DS2781 conserves power by disabling measurement and capacity estimation functions, but preserves register contents. SLEEP mode is entered under two different ...

... mode. While in ACTIVE mode, the DS2781 is fully functional with measurements and capacity estimation continuously updated. In SLEEP mode, the DS2781 conserves power by disabling measurement and capacity estimation functions, but preserves register contents. SLEEP mode is entered under two different ...

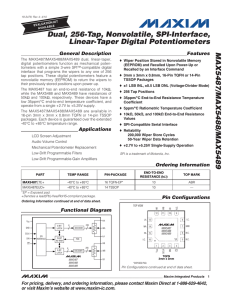

MAX5487/MAX5488/MAX5489 Dual, 256-Tap, Nonvolatile, SPI-Interface, Linear-Taper Digital Potentiometers General Description

... Note 3: DNL and INL are measured with the potentiometer configured as a variable resistor. H_ is unconnected and L_ = 0. For VDD = +5V, the wiper terminal is driven with a source current of 400µA for the 10kΩ configuration, 80µA for the 50kΩ configuration, and 40µA for the 100kΩ configuration. For V ...

... Note 3: DNL and INL are measured with the potentiometer configured as a variable resistor. H_ is unconnected and L_ = 0. For VDD = +5V, the wiper terminal is driven with a source current of 400µA for the 10kΩ configuration, 80µA for the 50kΩ configuration, and 40µA for the 100kΩ configuration. For V ...

Register file

A register file is an array of processor registers in a central processing unit (CPU). Modern integrated circuit-based register files are usually implemented by way of fast static RAMs with multiple ports. Such RAMs are distinguished by having dedicated read and write ports, whereas ordinary multiported SRAMs will usually read and write through the same ports.The instruction set architecture of a CPU will almost always define a set of registers which are used to stage data between memory and the functional units on the chip. In simpler CPUs, these architectural registers correspond one-for-one to the entries in a physical register file within the CPU. More complicated CPUs use register renaming, so that the mapping of which physical entry stores a particular architectural register changes dynamically during execution. The register file is part of the architecture and visible to the programmer, as opposed to the concept of transparent caches.