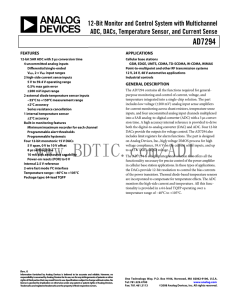

AD7294 12-Bit Monitor and Control System with Multichannel

... into a SAR analog-to-digital converter (ADC) with a 3 μs conversion time. A high accuracy internal reference is provided to drive both the digital-to-analog converter (DAC) and ADC. Four 12-bit DACs provide the outputs for voltage control. The AD7294 also includes limit registers for alarm functions ...

... into a SAR analog-to-digital converter (ADC) with a 3 μs conversion time. A high accuracy internal reference is provided to drive both the digital-to-analog converter (DAC) and ADC. Four 12-bit DACs provide the outputs for voltage control. The AD7294 also includes limit registers for alarm functions ...

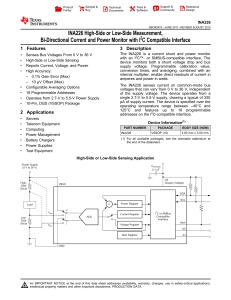

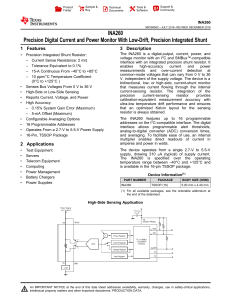

INA226 - Texas Instruments

... The device has two operating modes, continuous and triggered, that determine how the ADC operates following these conversions. When the device is in the normal operating mode (that is, MODE bits of the Configuration Register (00h) are set to '111'), it continuously converts a shunt voltage reading f ...

... The device has two operating modes, continuous and triggered, that determine how the ADC operates following these conversions. When the device is in the normal operating mode (that is, MODE bits of the Configuration Register (00h) are set to '111'), it continuously converts a shunt voltage reading f ...

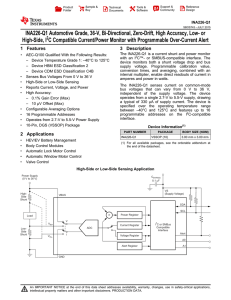

INA226-Q1 Automotive Grade, 36-V, Bi-Directional

... The device has two operating modes, continuous and triggered, that determine how the ADC operates following these conversions. When the device is in the normal operating mode (that is, MODE bits of the Configuration Register (00h) are set to '111'), it continuously converts a shunt voltage reading f ...

... The device has two operating modes, continuous and triggered, that determine how the ADC operates following these conversions. When the device is in the normal operating mode (that is, MODE bits of the Configuration Register (00h) are set to '111'), it continuously converts a shunt voltage reading f ...

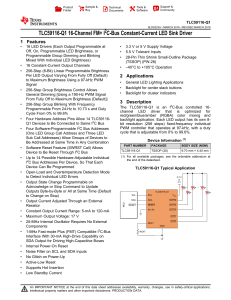

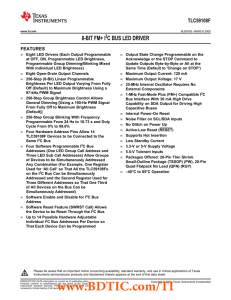

Datasheet - Texas Instruments

... TLC59116-Q1 devices to respond to a common I2C Bus address, allowing for example, all the same color LEDs to be turned on or off at the same time or marquee chasing effect, thus minimizing I2C Bus commands. Four hardware address pins allow up to 14 devices on the same Bus. The Software Reset (SWRST) ...

... TLC59116-Q1 devices to respond to a common I2C Bus address, allowing for example, all the same color LEDs to be turned on or off at the same time or marquee chasing effect, thus minimizing I2C Bus commands. Four hardware address pins allow up to 14 devices on the same Bus. The Software Reset (SWRST) ...

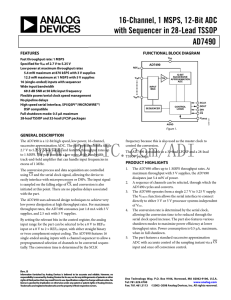

AD7490 数据手册DataSheet下载

... The mark/space ratio for the SCLK input is 40/60 to 60/40. The maximum SCLK frequency is 16 MHz with VDD = 3 V to give a throughput of 870 kSPS. Care must be taken when interfacing to account for data access time, t4, and the setup time required for the user’s processor. These two times determine th ...

... The mark/space ratio for the SCLK input is 40/60 to 60/40. The maximum SCLK frequency is 16 MHz with VDD = 3 V to give a throughput of 870 kSPS. Care must be taken when interfacing to account for data access time, t4, and the setup time required for the user’s processor. These two times determine th ...

INA260 Precision Current and Power Monitor with Low

... voltage monitor with an I2C and SMBus™-compatible interface with an integrated precision shunt resistor. It enables high-accuracy current and power measurements and over-current detection at common-mode voltages that can vary from 0 V to 36 V, independent of the supply voltage. The device is a bidir ...

... voltage monitor with an I2C and SMBus™-compatible interface with an integrated precision shunt resistor. It enables high-accuracy current and power measurements and over-current detection at common-mode voltages that can vary from 0 V to 36 V, independent of the supply voltage. The device is a bidir ...

DP8573A Real Time Clock (RTC)

... similar to an alarm clock wake up buzzer. This interrupt is generated when the clock time is equal to a value programmed into the alarm compare registers. Up to six bytes can be enabled to perform alarm time comparisons on the counter chain. These six bytes, or some subset thereof, would be loaded w ...

... similar to an alarm clock wake up buzzer. This interrupt is generated when the clock time is equal to a value programmed into the alarm compare registers. Up to six bytes can be enabled to perform alarm time comparisons on the counter chain. These six bytes, or some subset thereof, would be loaded w ...

AD7792 数据手册DataSheet下载

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

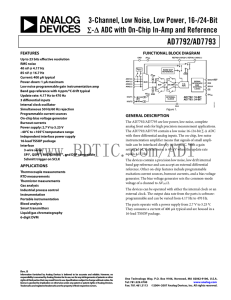

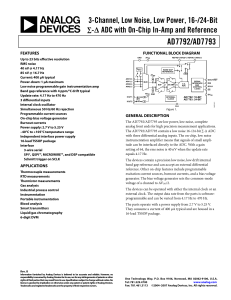

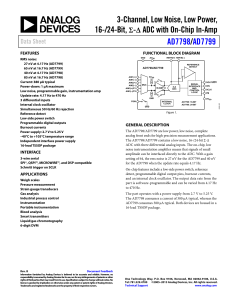

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16-/24-Bit ∑

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16/24-Bit ∑

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

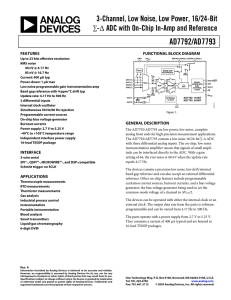

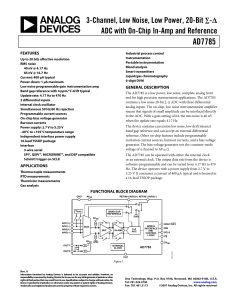

AD7785 3-Channel, Low Noise, Low Power, 20-Bit ∑

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

AD7785 3-Channel, Low Noise, Low Power, 20-Bit ∑-Δ

... continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the inte ...

... continuous with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the inte ...

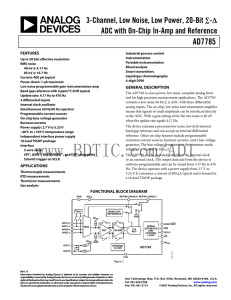

High-/Low-Side Measurement, Bidirectional CURRENT/POWER

... power-supply voltage are independent of each other; therefore, the bus voltage can be present with the supply voltage off, and vice-versa. As noted, the INA231 takes two measurements, shunt voltage and bus voltage. It then converts these measurements to current, based on the Calibration register val ...

... power-supply voltage are independent of each other; therefore, the bus voltage can be present with the supply voltage off, and vice-versa. As noted, the INA231 takes two measurements, shunt voltage and bus voltage. It then converts these measurements to current, based on the Calibration register val ...

c164cmsm_ds.pdf

... same linear address space which includes 16 MBytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable. The C164CM incorporates 32 KBytes of on-chip OTP memory or on-chip maskprogrammable ROM (no ...

... same linear address space which includes 16 MBytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable. The C164CM incorporates 32 KBytes of on-chip OTP memory or on-chip maskprogrammable ROM (no ...

COA 2

... c. Address of operand in memory d. Operand itself 79. The computer register used to hold address of instruction is a. Data Register b. Accumulator c. Instruction register d. Program counter 80. The computer register that specifies memory address is a. Address register b. Accumulator c. Instruction r ...

... c. Address of operand in memory d. Operand itself 79. The computer register used to hold address of instruction is a. Data Register b. Accumulator c. Instruction register d. Program counter 80. The computer register that specifies memory address is a. Address register b. Accumulator c. Instruction r ...

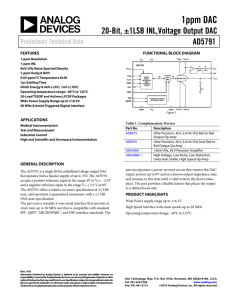

Rev. PrG

... Positive analog supply connection. A voltage in the range of 7.5 V to 16.5 V. can be connected VDD should be decoupled to AGND. Active Low Reset Pin. Asserting this pin will return the AD5791 to its power on status. Active Low input. Asserting this pin sets the DAC register to a user defined value ( ...

... Positive analog supply connection. A voltage in the range of 7.5 V to 16.5 V. can be connected VDD should be decoupled to AGND. Active Low Reset Pin. Asserting this pin will return the AD5791 to its power on status. Active Low input. Asserting this pin sets the DAC register to a user defined value ( ...

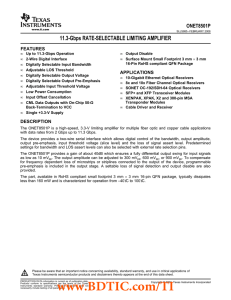

ONET8501P 数据资料 dataSheet 下载

... consists of a 100-Ω differential on-chip line termination resistor followed by a digitally controlled bandwidth switch input buffer for rate select. The RATE1 and RATE0 pins can be used to control the bandwidth of the filter. Default bandwidth settings are used; however, these can be changed using r ...

... consists of a 100-Ω differential on-chip line termination resistor followed by a digitally controlled bandwidth switch input buffer for rate select. The RATE1 and RATE0 pins can be used to control the bandwidth of the filter. Default bandwidth settings are used; however, these can be changed using r ...

AD7798-99 - Analog Devices

... transmitted in a continuous train of pulses. Alternatively, it can be noncontinuous, with the information transmitted to or from the ADC in smaller batches of data. Chip Select Input. This is an active low logic input used to select the ADC. CS can be used to select the ADC in systems with more than ...

... transmitted in a continuous train of pulses. Alternatively, it can be noncontinuous, with the information transmitted to or from the ADC in smaller batches of data. Chip Select Input. This is an active low logic input used to select the ADC. CS can be used to select the ADC in systems with more than ...

AD7798 数据手册DataSheet下载

... transmitted in a continuous train of pulses. Alternatively, it can be noncontinuous, with the information transmitted to or from the ADC in smaller batches of data. Chip Select Input. This is an active low logic input used to select the ADC. CS can be used to select the ADC in systems with more than ...

... transmitted in a continuous train of pulses. Alternatively, it can be noncontinuous, with the information transmitted to or from the ADC in smaller batches of data. Chip Select Input. This is an active low logic input used to select the ADC. CS can be used to select the ADC in systems with more than ...

TLC59108F 数据资料 dataSheet 下载

... A master device must internally provide a hold time of at least 300 ns for the SDA signal (refer to the VIL of the SCL signal) in order to bridge the undefined region of SCLs falling edge. The maximum tf for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time (tf) for the SDA out ...

... A master device must internally provide a hold time of at least 300 ns for the SDA signal (refer to the VIL of the SCL signal) in order to bridge the undefined region of SCLs falling edge. The maximum tf for the SDA and SCL bus lines is specified at 300 ns. The maximum fall time (tf) for the SDA out ...

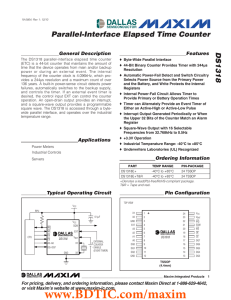

DS1318 Parallel-Interface Elapsed Time Counter General Description Features

... is disabled while the device is in power fail. The interrupt output pin provides two maskable interrupt sources. A 32-bit alarm register allows an interrupt to be generated whenever the upper 32 bits of the counter match the alarm register. A periodic interrupt can also be generated from once every ...

... is disabled while the device is in power fail. The interrupt output pin provides two maskable interrupt sources. A 32-bit alarm register allows an interrupt to be generated whenever the upper 32 bits of the counter match the alarm register. A periodic interrupt can also be generated from once every ...

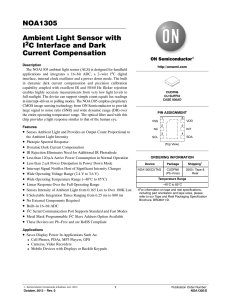

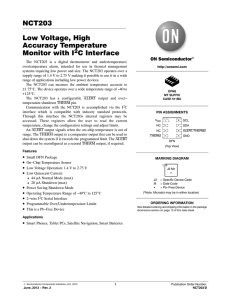

NCT203 - Low Voltage, High Accuracy

... The status register is a read−only register at Address 0x02. It contains status information for the NCT203. When Bit 7 of the status register is high, it indicates that the ADC is bisy converting. The other bits in this register flag the out−of−limit temperature measurements (Bit 6 to Bit 3, and Bit ...

... The status register is a read−only register at Address 0x02. It contains status information for the NCT203. When Bit 7 of the status register is high, it indicates that the ADC is bisy converting. The other bits in this register flag the out−of−limit temperature measurements (Bit 6 to Bit 3, and Bit ...

AD7787 数据手册DataSheet下载

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

AD7790 - Analog Devices

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

... The DOUT/RDY falling edge can be used as an interrupt to a processor, indicating that valid data is available. With an external serial clock, the data can be read using the DOUT/RDY pin. With CS low, the data/control word information is placed on the DOUT/RDY pin on the SCLK falling edge and is vali ...

Register file

A register file is an array of processor registers in a central processing unit (CPU). Modern integrated circuit-based register files are usually implemented by way of fast static RAMs with multiple ports. Such RAMs are distinguished by having dedicated read and write ports, whereas ordinary multiported SRAMs will usually read and write through the same ports.The instruction set architecture of a CPU will almost always define a set of registers which are used to stage data between memory and the functional units on the chip. In simpler CPUs, these architectural registers correspond one-for-one to the entries in a physical register file within the CPU. More complicated CPUs use register renaming, so that the mapping of which physical entry stores a particular architectural register changes dynamically during execution. The register file is part of the architecture and visible to the programmer, as opposed to the concept of transparent caches.