a LC MOS 16-Bit Voltage Output DAC

... In addition to the excellent accuracy specifications, the AD7846 also offers a comprehensive microprocessor interface. There are 16 data I/O pins, plus control lines (CS, R/W, LDAC and CLR). R/W and CS allow writing to and reading from the I/O latch. This is the readback function which is useful in ...

... In addition to the excellent accuracy specifications, the AD7846 also offers a comprehensive microprocessor interface. There are 16 data I/O pins, plus control lines (CS, R/W, LDAC and CLR). R/W and CS allow writing to and reading from the I/O latch. This is the readback function which is useful in ...

TRS3223-Q1 数据资料 dataSheet 下载

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant ...

... Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant ...

PD Service Manual - Intelligent Weighing Technology

... The charging current will go down automatically when voltage reached. Q8 (C945) and R14 (1.2R, 1/2W) provide Over-Current protection. 4) -5V power drives analog devices(OP. amp. & A/D converter) U9 (IC 7660) is a -5volts Voltage generator. 5) +5V power drives analog and digital circuit systems. U8 ...

... The charging current will go down automatically when voltage reached. Q8 (C945) and R14 (1.2R, 1/2W) provide Over-Current protection. 4) -5V power drives analog devices(OP. amp. & A/D converter) U9 (IC 7660) is a -5volts Voltage generator. 5) +5V power drives analog and digital circuit systems. U8 ...

MAX8660/MAX8660A/MAX8660B/MAX8661 High-Efficiency, Low-I , PMICs with Dynamic Voltage Management for Mobile Applications

... and an 8th always-on LDO are integrated with powermanagement functions. Two dynamically controlled DCDC outputs power the processor core and internal memory. Two other DC-DC converters power I/O, memory, and other peripherals. Additional functions include on/off control for outputs, low-battery dete ...

... and an 8th always-on LDO are integrated with powermanagement functions. Two dynamically controlled DCDC outputs power the processor core and internal memory. Two other DC-DC converters power I/O, memory, and other peripherals. Additional functions include on/off control for outputs, low-battery dete ...

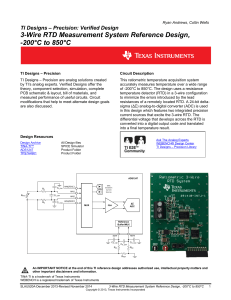

3-Wire RTD Measurement System Reference Design,

... resolution and accuracy needed to achieve the aforementioned design goals, but also features all the internal sub-circuits required to realize the design. The ADS1247 is a 24-bit, delta-sigma (ΔΣ) ADC that offers a complete front-end solution for RTD applications. It comes from a product family of h ...

... resolution and accuracy needed to achieve the aforementioned design goals, but also features all the internal sub-circuits required to realize the design. The ADS1247 is a 24-bit, delta-sigma (ΔΣ) ADC that offers a complete front-end solution for RTD applications. It comes from a product family of h ...

HMC981LP3E 数据资料DataSheet下载

... The HMC981LP3E has an integrated negative voltage generator to synthesize negative voltages required to drive depletion mode amplifiers. If an external negative supply is already available or an enhancement mode device is targeted, the negative voltage generator can be disabled. The HMC981LP3E achie ...

... The HMC981LP3E has an integrated negative voltage generator to synthesize negative voltages required to drive depletion mode amplifiers. If an external negative supply is already available or an enhancement mode device is targeted, the negative voltage generator can be disabled. The HMC981LP3E achie ...

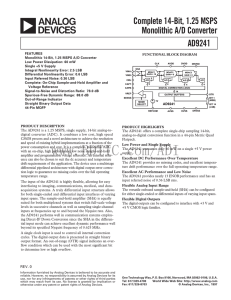

AD9241 数据手册DataSheet 下载

... CMOS process and a novel architecture to achieve the resolution and speed of existing hybrid implementations at a fraction of the power consumption and cost. It is a complete, monolithic ADC with an on-chip, high performance, low noise sample-and-hold amplifier and programmable voltage reference. An ...

... CMOS process and a novel architecture to achieve the resolution and speed of existing hybrid implementations at a fraction of the power consumption and cost. It is a complete, monolithic ADC with an on-chip, high performance, low noise sample-and-hold amplifier and programmable voltage reference. An ...

BD81002MUV

... VDD1 will activate. When EN2 is H, VDD2 will activate. When EN3 is High, AVDD・HVLDO・VCOM・VGH・VGL will activate. The control pin is internally pulled down to GND, whereby operating the relevant block in the open state. The Power Good pin (PG1・PG2・PGCP) is designed in an open-drain pattern to use as t ...

... VDD1 will activate. When EN2 is H, VDD2 will activate. When EN3 is High, AVDD・HVLDO・VCOM・VGH・VGL will activate. The control pin is internally pulled down to GND, whereby operating the relevant block in the open state. The Power Good pin (PG1・PG2・PGCP) is designed in an open-drain pattern to use as t ...

Constant Current Source and Temperature Sensor

... is expressed as a percent deviation from this amount. ISET increases at 0.336%/°C at Tj = 25°C. Note 4: ISET is nominally directly proportional to absolute temperature (°K). ISET at any temperature can be calculated from: ISET = IO (T/TO) where IO is ISET measured at TO (°K). Note 5: VMAX = 40V for ...

... is expressed as a percent deviation from this amount. ISET increases at 0.336%/°C at Tj = 25°C. Note 4: ISET is nominally directly proportional to absolute temperature (°K). ISET at any temperature can be calculated from: ISET = IO (T/TO) where IO is ISET measured at TO (°K). Note 5: VMAX = 40V for ...

LM139/LM239/LM339/LM2901/LM3302 Low Power Low Offset

... The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines. The input common-mode voltage or either input signal voltage should not be allowed ...

... The direction of the input current is out of the IC due to the PNP input stage. This current is essentially constant, independent of the state of the output so no loading change exists on the reference or input lines. The input common-mode voltage or either input signal voltage should not be allowed ...

LTC2424/LTC2428 - 4-/8-Channel 20-Bit

... GND (Pins 1, 6, 16, 18, 22, 27, 28): Ground. Should be connected directly to a ground plane through a minimum length trace or it should be the single-point-ground in a single-point grounding system. ...

... GND (Pins 1, 6, 16, 18, 22, 27, 28): Ground. Should be connected directly to a ground plane through a minimum length trace or it should be the single-point-ground in a single-point grounding system. ...

Lateral SCR Devices with Low-Voltage High

... against the overshooting or undershooting noise pulses when the CMOS IC’s are in the normal operating conditions. There are two possible methods to avoid the LVTSCR being triggered on by the noise pulses when the IC is in the normal operating conditions. One possible method is to increase the holdin ...

... against the overshooting or undershooting noise pulses when the CMOS IC’s are in the normal operating conditions. There are two possible methods to avoid the LVTSCR being triggered on by the noise pulses when the IC is in the normal operating conditions. One possible method is to increase the holdin ...

ADS5281 数据资料 dataSheet 下载

... –40°C to TMAX = +85°C, AVDD = 3.3V, LVDD = 1.8V, clock frequency = 10MSPS to 65MSPS, 50% clock duty cycle, –1dBFS differential analog input, internal reference mode, ISET resistor = 56.2kΩ, and LVDS buffer current setting = 3.5mA, unless ...

... –40°C to TMAX = +85°C, AVDD = 3.3V, LVDD = 1.8V, clock frequency = 10MSPS to 65MSPS, 50% clock duty cycle, –1dBFS differential analog input, internal reference mode, ISET resistor = 56.2kΩ, and LVDS buffer current setting = 3.5mA, unless ...

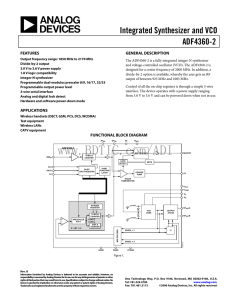

Integrated Synthesizer and VCO ADF4360-2 FEATURES

... Internal Compensation Node. This pin must be decoupled to VVCO with a 10 μF capacitor. Digital Ground. Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of 100 kΩ. See Figure 10. This input can be driven from a TTL or CMOS crystal oscillator ...

... Internal Compensation Node. This pin must be decoupled to VVCO with a 10 μF capacitor. Digital Ground. Reference Input. This is a CMOS input with a nominal threshold of VDD/2 and a dc equivalent input resistance of 100 kΩ. See Figure 10. This input can be driven from a TTL or CMOS crystal oscillator ...

BD95835EFJ

... must be established within the fixed soft start time. As output capacitance, bypass capacitor will be also connected to output load side (CEXT, Figure 23). Please set the over current detection value with regards to these capacitance. Co+CEXT≦ ...

... must be established within the fixed soft start time. As output capacitance, bypass capacitor will be also connected to output load side (CEXT, Figure 23). Please set the over current detection value with regards to these capacitance. Co+CEXT≦ ...

Old Company Name in Catalogs and Other Documents

... All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renes ...

... All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renes ...

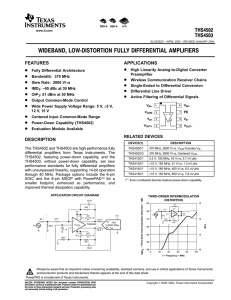

Wideband, Low-Distortion Fully Differential Amplifiers (Rev. D)

... junction temperature at or below 125°C for best performance and long term reliability. ...

... junction temperature at or below 125°C for best performance and long term reliability. ...

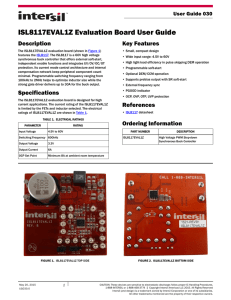

ISL8117EVAL1Z User Guide

... refer to Table 2 for the desired operating option. Ensure that the circuit is correctly connected to the supply and electronic loads prior to applying any power. Please refer to Figure 4 for ...

... refer to Table 2 for the desired operating option. Ensure that the circuit is correctly connected to the supply and electronic loads prior to applying any power. Please refer to Figure 4 for ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.