docx - Instructure

... 1. Design: The R-2R ladder D/A circuit is shown above in Fig. 1. The value of R cancels out in this circuit. That is, vD/A does not depend on the value of R. In practice, however, we want a value of R that will result in currents around 100 mA. Much smaller currents than 100 mA result in circuit noi ...

... 1. Design: The R-2R ladder D/A circuit is shown above in Fig. 1. The value of R cancels out in this circuit. That is, vD/A does not depend on the value of R. In practice, however, we want a value of R that will result in currents around 100 mA. Much smaller currents than 100 mA result in circuit noi ...

AMIS120 Circuit Description

... approximately 300mV below the reference voltage (pin3, ~7.5V) will provide full mute (-80dB). The need to have the remote pot on two wire connection means that there is a small amount of attenuation (approx 1dB) when the pot is connected. For the best audio control a log pot should be used. The cont ...

... approximately 300mV below the reference voltage (pin3, ~7.5V) will provide full mute (-80dB). The need to have the remote pot on two wire connection means that there is a small amount of attenuation (approx 1dB) when the pot is connected. For the best audio control a log pot should be used. The cont ...

MAX1615/MAX1616 High-Voltage, Low-Power Linear Regulators for Notebook Computers ________________General Description

... Use 1µF minimum on the output, or 4.7µF for the full 30mA load current (6.8µF, MAX1616). Otherwise, use 1µF plus 0.125µF/mA (0.2µF/µA, MAX1616). For output voltages less than 3.3V, use 15µF instead of 6.8µF. The output capacitor’s effective series resistance (ESR) must be less than 1Ω for stable ope ...

... Use 1µF minimum on the output, or 4.7µF for the full 30mA load current (6.8µF, MAX1616). Otherwise, use 1µF plus 0.125µF/mA (0.2µF/µA, MAX1616). For output voltages less than 3.3V, use 15µF instead of 6.8µF. The output capacitor’s effective series resistance (ESR) must be less than 1Ω for stable ope ...

2E7 Engineering Science: Electrical Engineering

... iC CVm ( jCost j 2 Sint ) iC jCVm (Cost jSint ) iC jCVme jt jIme jt The presence of the j term in the result indicates a phase advancement of 90 o in the complex plane. This is consistent with the result obtained above where the exciting voltage was treated as a singular sine fu ...

... iC CVm ( jCost j 2 Sint ) iC jCVm (Cost jSint ) iC jCVme jt jIme jt The presence of the j term in the result indicates a phase advancement of 90 o in the complex plane. This is consistent with the result obtained above where the exciting voltage was treated as a singular sine fu ...

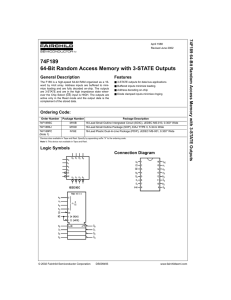

74F189 64-Bit Random Access Memory with 3

... 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E ...

... 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E ...

bp5220a : Power Modules

... (1) No circuit is installed in the modules to protect against excessive output currents. Therefore, take physical safety measures such as using a fuse if short-circuit loading is probable. (2) The output current should be reduced according to an increase in the input voltage or ambient temperature. ...

... (1) No circuit is installed in the modules to protect against excessive output currents. Therefore, take physical safety measures such as using a fuse if short-circuit loading is probable. (2) The output current should be reduced according to an increase in the input voltage or ambient temperature. ...

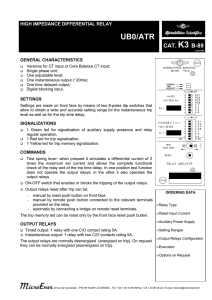

UB0/ATR - Microener

... 1 Red led for trip signalization. 1 Yellow led for trip memory signalization. ...

... 1 Red led for trip signalization. 1 Yellow led for trip memory signalization. ...

FST3244 — 8-Bit Bus Switch Features Description

... Minimal Propagation Delay through the Switch ...

... Minimal Propagation Delay through the Switch ...

UNIT-VII Static Series Compensators

... maximum and the successive, opposite polarity half-cycle of the line current will discharge it from this maximum to zero. • As can be seen, the capacitor insertion at line current zero, necessitated by the switching limitation of the thyristor valve, results in a dc offset voltage which is equal to ...

... maximum and the successive, opposite polarity half-cycle of the line current will discharge it from this maximum to zero. • As can be seen, the capacitor insertion at line current zero, necessitated by the switching limitation of the thyristor valve, results in a dc offset voltage which is equal to ...

Document

... and some other benefits. EXISTING SYSTEM: Due to the elimination of the full-bridge input rectifier, the components in the current path are reduced and this results in fewer conduction losses. There are several bridgeless PFC topologies already published, for example the “Basic Bridgeless Boost ...

... and some other benefits. EXISTING SYSTEM: Due to the elimination of the full-bridge input rectifier, the components in the current path are reduced and this results in fewer conduction losses. There are several bridgeless PFC topologies already published, for example the “Basic Bridgeless Boost ...

physics 201 - La Salle University

... Part 6. Digital to Analog. Build a simple digital-to-analog converter discussed in lecture. Build a circuit that converts a digital signal (three inputs of +5 volts or 0 volts) to an analog signal (the appropriate fraction of 5 volts). Paste two copies of your circuit below showing different inputs ...

... Part 6. Digital to Analog. Build a simple digital-to-analog converter discussed in lecture. Build a circuit that converts a digital signal (three inputs of +5 volts or 0 volts) to an analog signal (the appropriate fraction of 5 volts). Paste two copies of your circuit below showing different inputs ...

Product Specifications VC-6000 Monitoring System Monitoring Module – SM-610-A04

... channel. Any 2 vector components (1n, 2n, Xn & Yn magnitude and phase, residual values, and overall RMS) per vibration signal input can be monitored to alarm limits, the other vector values are subsequently available only for condition monitoring purposes. ...

... channel. Any 2 vector components (1n, 2n, Xn & Yn magnitude and phase, residual values, and overall RMS) per vibration signal input can be monitored to alarm limits, the other vector values are subsequently available only for condition monitoring purposes. ...

Z04706163168

... The inclusion of a few additional diodes and passive elements in the high-frequency full-bridge ac–dc converter with galvanic isolation permits one to achieve sinusoidal input-current wave shaping and output-voltage regulation simultaneously without adding any auxiliary transistors. Recently, this p ...

... The inclusion of a few additional diodes and passive elements in the high-frequency full-bridge ac–dc converter with galvanic isolation permits one to achieve sinusoidal input-current wave shaping and output-voltage regulation simultaneously without adding any auxiliary transistors. Recently, this p ...

MAX1747 Triple Charge-Pump TFT LCD DC-DC Converter General Description

... (VPOS) and a negative output (VNEG). These two outputs use external diode and capacitor stages (as many stages as required) to regulate output voltages above +35V and under -35V. A proprietary regulation algorithm minimizes output ripple as well as capacitor sizes for all three charge pumps. Also in ...

... (VPOS) and a negative output (VNEG). These two outputs use external diode and capacitor stages (as many stages as required) to regulate output voltages above +35V and under -35V. A proprietary regulation algorithm minimizes output ripple as well as capacitor sizes for all three charge pumps. Also in ...

High-Speed Data Communication LA302Z – 10 GHz Differential

... The LA302Z is an ultra-broadband fully differential limiting amplifier designed for highspeed wide-band communication applications up to 10 Gb/s. The amplifier has an excellent input sensitivity of 2.5 mVpp and a small-signal bandwidth of 10 GHz. Its wide bandwidth and high sensitivity ensure a low ...

... The LA302Z is an ultra-broadband fully differential limiting amplifier designed for highspeed wide-band communication applications up to 10 Gb/s. The amplifier has an excellent input sensitivity of 2.5 mVpp and a small-signal bandwidth of 10 GHz. Its wide bandwidth and high sensitivity ensure a low ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.