Lecture 4: Transformers

... proportional to the square of the current transmitted, raising the voltage, say, by the factor of 10 would decrease the current by the same factor (to deliver the same amount of energy) and, therefore, reduce losses by factor of 100. ...

... proportional to the square of the current transmitted, raising the voltage, say, by the factor of 10 would decrease the current by the same factor (to deliver the same amount of energy) and, therefore, reduce losses by factor of 100. ...

Computer Exercises Manual: Device Parameters in SPICE

......f or g

For example,

R1 1 0 100

speci¯es that a 100 resistor, labeled R1, is connected between the nodes 1 and 0. An additional

line like C1 1 0 5p would mean that a capacitor is connected in parallel with the resistor. The

capacitor value is expressed as 5p, ...

...

MAX1232 - Maxim Part Number Search

... The microprocessor drives the ST input with an input/ output (I/O) line. The microprocessor must toggle the ST input within a set period (as determined by TD) to verify proper software execution. If a hardware or software failure keeps ST from toggling within the minimum timeout period—ST is activat ...

... The microprocessor drives the ST input with an input/ output (I/O) line. The microprocessor must toggle the ST input within a set period (as determined by TD) to verify proper software execution. If a hardware or software failure keeps ST from toggling within the minimum timeout period—ST is activat ...

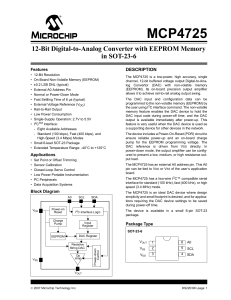

12-Bit DAC with EEPROM Memory in SOT-23-6

... nel driver. Therefore, it needs a pull-up resistor from the VDD line to the SDA pin. Except for start and stop conditions, the data on the SDA pin must be stable during the high period of the clock. The high or low state of the SDA pin can only change when the clock signal on the SCL pin is low. Ref ...

... nel driver. Therefore, it needs a pull-up resistor from the VDD line to the SDA pin. Except for start and stop conditions, the data on the SDA pin must be stable during the high period of the clock. The high or low state of the SDA pin can only change when the clock signal on the SCL pin is low. Ref ...

Pdf

... V R full load into 100 percent. So, this is what we define, basically what we are trying to say here is that suppose we have a line which is loaded to it is full load value. And if the load is suddenly thrown off what will be the voltage at the receiving end. How much rise of voltage is there at the ...

... V R full load into 100 percent. So, this is what we define, basically what we are trying to say here is that suppose we have a line which is loaded to it is full load value. And if the load is suddenly thrown off what will be the voltage at the receiving end. How much rise of voltage is there at the ...

21 circuits, bioelectricity, and dc instruments

... • Explain why a null measurement device is more accurate than a standard voltmeter or ammeter. • Demonstrate how a Wheatstone bridge can be used to accurately calculate the resistance in a circuit. 21.6. DC Circuits Containing Resistors and Capacitors • Explain the importance of the time constant, τ ...

... • Explain why a null measurement device is more accurate than a standard voltmeter or ammeter. • Demonstrate how a Wheatstone bridge can be used to accurately calculate the resistance in a circuit. 21.6. DC Circuits Containing Resistors and Capacitors • Explain the importance of the time constant, τ ...

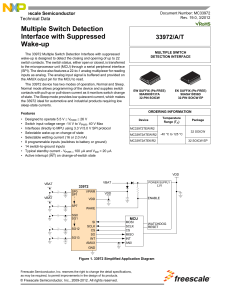

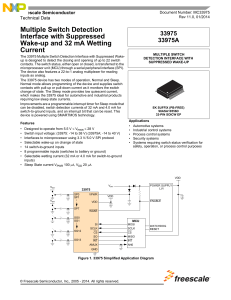

MC33972, Multiple Switch Detection Interface with Suppressed

... register of the 33972. The SI data is latched into the input shift register on the falling edge of SCLK signal. The SO pin shifts the switch status bits out on the rising edge of SCLK. The SO data is available for the MCU to read on the falling edge of SCLK. False clocking of the shift register must ...

... register of the 33972. The SI data is latched into the input shift register on the falling edge of SCLK signal. The SO pin shifts the switch status bits out on the rising edge of SCLK. The SO data is available for the MCU to read on the falling edge of SCLK. False clocking of the shift register must ...

PTN3381D - NXP Semiconductors

... Current sense port used to provide an accurate current reference for the differential outputs OUT_Dx. For best output voltage swing accuracy, use of a 10 k resistor (1 % tolerance) from this terminal to GND is recommended. May also be tied to either VDD or GND directly (0 ). See Section 7.2 for de ...

... Current sense port used to provide an accurate current reference for the differential outputs OUT_Dx. For best output voltage swing accuracy, use of a 10 k resistor (1 % tolerance) from this terminal to GND is recommended. May also be tied to either VDD or GND directly (0 ). See Section 7.2 for de ...

Designing a Three Phase Inverter for a Permanent Magnet Synchronous Motor

... Synchronous machines were first development during the middle of the 19th century as single phase generators to supply lighting systems. In the early development the salient pole rotor motor and the turbo generator formed as the typical design type. Being closely connected with the development of po ...

... Synchronous machines were first development during the middle of the 19th century as single phase generators to supply lighting systems. In the early development the salient pole rotor motor and the turbo generator formed as the typical design type. Being closely connected with the development of po ...

ESM-49 96x48 1/8 DIN 00 Process Indicator

... with the unit can be prevented. Never attempt to disassemble, modify or repair this unit. Tampering with the unit may results in malfunction, electric shock or fire. Do not use the unit in combustible or explosive gaseous atmospheres. During the equipment is putted in hole on the metal panel while m ...

... with the unit can be prevented. Never attempt to disassemble, modify or repair this unit. Tampering with the unit may results in malfunction, electric shock or fire. Do not use the unit in combustible or explosive gaseous atmospheres. During the equipment is putted in hole on the metal panel while m ...

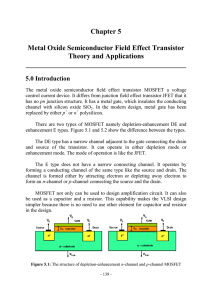

Chapter 5 MOSFET Theory and Applications

... 5.5.1 Equivalent Circuit for Enhancement MOSFET From Fig. 4.14 of JEFT equivalent circuit in Chapter 4, the output resistance ro of MOSFET is at least a few orders higher than the drain resistance RD. Similar it is true for MOSFET. Practically there is no gate-to-source current. Thus, the gate-to-so ...

... 5.5.1 Equivalent Circuit for Enhancement MOSFET From Fig. 4.14 of JEFT equivalent circuit in Chapter 4, the output resistance ro of MOSFET is at least a few orders higher than the drain resistance RD. Similar it is true for MOSFET. Practically there is no gate-to-source current. Thus, the gate-to-so ...

PowerPad Portable Power Monitor User Manual

... WARNING: The battery may fully discharge when recording for long periods of time while not connected to a power supply. The PowerPad unit will continue to record for some time, even if below the minimum battery charge value. However, the display may not come back on, and will eventually stop saving ...

... WARNING: The battery may fully discharge when recording for long periods of time while not connected to a power supply. The PowerPad unit will continue to record for some time, even if below the minimum battery charge value. However, the display may not come back on, and will eventually stop saving ...

BDTIC www.BDTIC.com/infineon Ballast Design for 54W T5 Fluorescent Lamp

... development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Inco ...

... development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium. HYPERTERMINAL™ of Hilgraeve Inco ...

Hot Swap Controller and Digital Power Monitor with Soft Start Pin ADM1177

... Timer Pin. An external capacitor, CTIMER, sets a 270 ms/μF initial timing cycle delay and a 21.7 ms/μF fault delay. The GATE pin turns off when the TIMER pin is pulled beyond the upper threshold. An overvoltage detection with an external Zener can be used to force this pin high. I2C Clock Pin. Open- ...

... Timer Pin. An external capacitor, CTIMER, sets a 270 ms/μF initial timing cycle delay and a 21.7 ms/μF fault delay. The GATE pin turns off when the TIMER pin is pulled beyond the upper threshold. An overvoltage detection with an external Zener can be used to force this pin high. I2C Clock Pin. Open- ...

Document

... A 1 V p-p change in vGS gives a 1.25 mA p-p change in iDS and a 4 V p-p change in vDS. Notice the characteristic non-linear I/O relationship compared to the BJT. Dr. D G Borse ...

... A 1 V p-p change in vGS gives a 1.25 mA p-p change in iDS and a 4 V p-p change in vDS. Notice the characteristic non-linear I/O relationship compared to the BJT. Dr. D G Borse ...

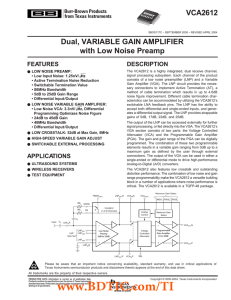

VCA2612 数据资料 dataSheet 下载

... noise figure improvement. Different cable termination characteristics can be accommodated by utilizing the VCA2612’s switchable LNA feedback pins. The LNP has the ability to accept both differential and single-ended inputs, and generates a differential output signal. The LNP provides strappable gain ...

... noise figure improvement. Different cable termination characteristics can be accommodated by utilizing the VCA2612’s switchable LNA feedback pins. The LNP has the ability to accept both differential and single-ended inputs, and generates a differential output signal. The LNP provides strappable gain ...

PTN3360D 1. General description Enhanced performance HDMI/DVI level shifter with active DDC

... HVQFN48 package supply ground is connected to both GND pins and exposed center pad. GND pins and the exposed center pad must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board usi ...

... HVQFN48 package supply ground is connected to both GND pins and exposed center pad. GND pins and the exposed center pad must be connected to supply ground for proper device operation. For enhanced thermal, electrical, and board level performance, the exposed pad needs to be soldered to the board usi ...

S6B1713 - ELECTRONIC ASSEMBLY

... Internal resistors select pin This pin selects the resistors for adjusting V0 voltage level. − INTRS = "H": use the internal resistors. − INTRS = "L": use the external resistors. V0 voltage is controlled with VR pin and external resistive divider. Power control pin of the power supply circuit for LC ...

... Internal resistors select pin This pin selects the resistors for adjusting V0 voltage level. − INTRS = "H": use the internal resistors. − INTRS = "L": use the external resistors. V0 voltage is controlled with VR pin and external resistive divider. Power control pin of the power supply circuit for LC ...

2300 Exam 1 Spring 2003

... The first load absorbs 1500[W] and delivers 2000[VAR]. The second load absorbs 900[VA] at 0.8 pf lagging. The third load is purely resistive, and draws an rms current of 3[Arms]. The fourth load can be modeled as a 5[] resistor in series with a 2[mF] capacitor. a) Find the average power delivered b ...

... The first load absorbs 1500[W] and delivers 2000[VAR]. The second load absorbs 900[VA] at 0.8 pf lagging. The third load is purely resistive, and draws an rms current of 3[Arms]. The fourth load can be modeled as a 5[] resistor in series with a 2[mF] capacitor. a) Find the average power delivered b ...

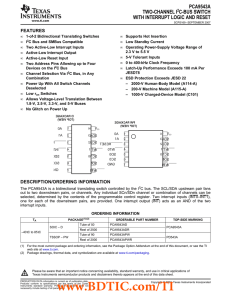

PCA9543A 数据资料 dataSheet 下载

... is driven low. The channel does not need to be active for detection of the interrupt. A bit also is set in the control register. Bit 4 and Bit 5 of the control register correspond to the INT0 and INT1 inputs of the PCA9543A, respectively. Therefore, if an interrupt is generated by any device connect ...

... is driven low. The channel does not need to be active for detection of the interrupt. A bit also is set in the control register. Bit 4 and Bit 5 of the control register correspond to the INT0 and INT1 inputs of the PCA9543A, respectively. Therefore, if an interrupt is generated by any device connect ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.