Get low-noise, low-ripple, high

... element. AOL is the open-loop gain of the error amplifier, and gm is the pass-element transconductance. The error amplifier controls the voltage at the gate of the pass element so that the current through the FET keeps the output voltage regulated relative to the internal reference voltage. Assuming ...

... element. AOL is the open-loop gain of the error amplifier, and gm is the pass-element transconductance. The error amplifier controls the voltage at the gate of the pass element so that the current through the FET keeps the output voltage regulated relative to the internal reference voltage. Assuming ...

ADS5542 数据资料 dataSheet 下载

... degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. If the input signal can exceed 3.6 V, then a resistor greater than or equal to 25 Ω should be added in series with each of the ana ...

... degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied. If the input signal can exceed 3.6 V, then a resistor greater than or equal to 25 Ω should be added in series with each of the ana ...

LM5005 High Voltage 2.5 Amp Buck Regulator (Rev. E)

... high voltage buck regulator using a minimum of external components. This easy to use regulator integrates a 75V N-Channel buck switch with an output current capability of 2.5 Amps. The regulator control method is based on current mode control utilizing an emulated current ramp. Peak current mode con ...

... high voltage buck regulator using a minimum of external components. This easy to use regulator integrates a 75V N-Channel buck switch with an output current capability of 2.5 Amps. The regulator control method is based on current mode control utilizing an emulated current ramp. Peak current mode con ...

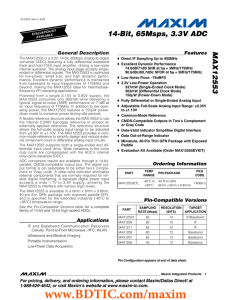

General Description Features

... The MAX12553 is a 3.3V, 14-bit, 65Msps analog-to-digital converter (ADC) featuring a fully differential wideband track-and-hold (T/H) input amplifier, driving a low-noise internal quantizer. The analog input stage accepts singleended or differential signals. The MAX12553 is optimized for low-power, ...

... The MAX12553 is a 3.3V, 14-bit, 65Msps analog-to-digital converter (ADC) featuring a fully differential wideband track-and-hold (T/H) input amplifier, driving a low-noise internal quantizer. The analog input stage accepts singleended or differential signals. The MAX12553 is optimized for low-power, ...

ADF4156 (Rev. E)

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the shift register on the CLOCK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the three LSBs serving as the contr ...

... Serial Clock Input. This serial clock is used to clock in the serial data to the registers. The data is latched into the shift register on the CLOCK rising edge. This input is a high impedance CMOS input. Serial Data Input. The serial data is loaded MSB first with the three LSBs serving as the contr ...

LTC2310-12 – 12-Bit + Sign, 2Msps Differential Input ADC with Wide

... Note 2: All voltage values are with respect to ground. Note 3: When these pin voltages are taken below ground, or above VDD or OVDD, they will be clamped by internal diodes. This product can handle input currents up to 100mA below ground, or above VDD or OVDD, without latch-up. Note 4: VDD = 5V, OVD ...

... Note 2: All voltage values are with respect to ground. Note 3: When these pin voltages are taken below ground, or above VDD or OVDD, they will be clamped by internal diodes. This product can handle input currents up to 100mA below ground, or above VDD or OVDD, without latch-up. Note 4: VDD = 5V, OVD ...

AS339/339A Description Features

... transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground fo ...

... transistors becoming forward biased and thereby acting as input diode clamps. In addition to this diode action, there is also lateral NPN parasitic transistor action on the IC chip. This transistor action can cause the output voltages of the comparators to go to the V+ voltage level (or to ground fo ...

ph104exp07_AC_RLC_Circuits_04

... them, and you have the basis for understanding an enormous variety of functions performed by electronic circuits. This week we concentrate on circuits containing R, L, and C. In Labs #10-11 you will learn about voltage rectification by a diode and amplification by a transistor circuit. This Lab allo ...

... them, and you have the basis for understanding an enormous variety of functions performed by electronic circuits. This week we concentrate on circuits containing R, L, and C. In Labs #10-11 you will learn about voltage rectification by a diode and amplification by a transistor circuit. This Lab allo ...

ADF4360-1 Integrated Synthesizer and VCO Data Sheet (REV. 0)

... Analog Ground. This is the ground return path of the prescaler and VCO. VCO Output. The output level is programmable from −6 dBm to −13 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −6 dBm to −13 d ...

... Analog Ground. This is the ground return path of the prescaler and VCO. VCO Output. The output level is programmable from −6 dBm to −13 dBm. See the Output Matching section for a description of the various output stages. VCO Complementary Output. The output level is programmable from −6 dBm to −13 d ...

Multiple State Electrostatically Formed Nanowire Transistors

... independent gates, termed here JGN, JGS, JGE and JGW. The drains are `islands’, isolated from each other and located between the gates. The source is located beneath the drains. An illustration of a three dimensional MSET with four gates and four drains is shown in Fig 1(b). In this case the conduct ...

... independent gates, termed here JGN, JGS, JGE and JGW. The drains are `islands’, isolated from each other and located between the gates. The source is located beneath the drains. An illustration of a three dimensional MSET with four gates and four drains is shown in Fig 1(b). In this case the conduct ...

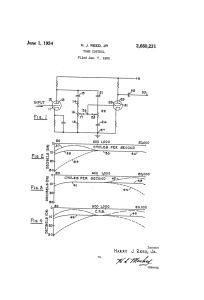

pat2680231_reed.pdf

... spectrum is accomplished by providing a concontrols, whether employed in an audible fre- 15 trol which reduces the attemation of the netquency band or in an inaudible frequency band, work for this particular frequency range. Acare herein termed tone controls. cordingly, to boost the high frequency e ...

... spectrum is accomplished by providing a concontrols, whether employed in an audible fre- 15 trol which reduces the attemation of the netquency band or in an inaudible frequency band, work for this particular frequency range. Acare herein termed tone controls. cordingly, to boost the high frequency e ...

Introduction to Electronics Laboratory Manual

... Configuration" (CBC) and the "Common Emitter Configuration" (CEC). The naming originates from the fact that the Base, respectively the Emitter, are connected to the Ground of the circuit which is the common connection between one jack of input jacks and one jack of the output jacks. Consdering the ...

... Configuration" (CBC) and the "Common Emitter Configuration" (CEC). The naming originates from the fact that the Base, respectively the Emitter, are connected to the Ground of the circuit which is the common connection between one jack of input jacks and one jack of the output jacks. Consdering the ...

Atmel ATA6831C Triple Half-bridge Driver with SPI and PWM Features DATASHEET

... If undervoltage is detected at pin VS, the power-supply fail bit (PSF) in the output register is set and all outputs are disabled. To detect an undervoltage, its duration has to last longer than the undervoltage detection delay time tdUV. The outputs are enabled immediately when the supply voltage r ...

... If undervoltage is detected at pin VS, the power-supply fail bit (PSF) in the output register is set and all outputs are disabled. To detect an undervoltage, its duration has to last longer than the undervoltage detection delay time tdUV. The outputs are enabled immediately when the supply voltage r ...

LM5576/5576Q SIMPLE SWITCHER® 75V, 3A Step

... The LM5576 switching regulator features all of the functions necessary to implement an efficient high voltage buck regulator using a minimum of external components. This easy to use regulator integrates a 75 V N-Channel buck switch with an output current capability of 3 Amps. The regulator control m ...

... The LM5576 switching regulator features all of the functions necessary to implement an efficient high voltage buck regulator using a minimum of external components. This easy to use regulator integrates a 75 V N-Channel buck switch with an output current capability of 3 Amps. The regulator control m ...

AD7679 数据手册DataSheet下载

... incomplete read error flag. In slave mode, when a data read is started and not complete when the following conversion is complete, the current data is lost and RDERROR is pulsed high. Bit 14 to Bit 17 of the Parallel Port Data Output Bus. These pins are always outputs regardless of the interface mod ...

... incomplete read error flag. In slave mode, when a data read is started and not complete when the following conversion is complete, the current data is lost and RDERROR is pulsed high. Bit 14 to Bit 17 of the Parallel Port Data Output Bus. These pins are always outputs regardless of the interface mod ...

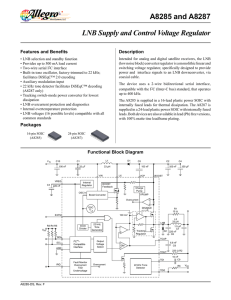

A8285 and A8287 - Allegro Microsystems

... • Undervoltage Lockout (VUV). When the input voltage (VIN) drops below the undervoltage threshold, the undervoltage bit VUV is set, disabling the output. When VIN is initially applied to the A8285/A8285, the VUV bit is set, indicating that an undervoltage condition has occurred. IRQ Flag. The IRQ fl ...

... • Undervoltage Lockout (VUV). When the input voltage (VIN) drops below the undervoltage threshold, the undervoltage bit VUV is set, disabling the output. When VIN is initially applied to the A8285/A8285, the VUV bit is set, indicating that an undervoltage condition has occurred. IRQ Flag. The IRQ fl ...

MAX3053 ±80V Fault-Protected, 2Mbps, Low Supply Current CAN Transceiver General Description

... high-voltage power buses. The device provides differential transmit capability to the bus and differential receive capability to the CAN controller. The MAX3053 has three different modes of operation: high-speed, slope control, and shutdown. High-speed mode allows data rates up to 2Mbps. In slope co ...

... high-voltage power buses. The device provides differential transmit capability to the bus and differential receive capability to the CAN controller. The MAX3053 has three different modes of operation: high-speed, slope control, and shutdown. High-speed mode allows data rates up to 2Mbps. In slope co ...

BD90610EFJ-C

... only effective in preventing destruction from sudden accident. It does not support the continuous operation of the protection circuit (e.g. if a load, which significantly exceeds the output current capacitance, is connected). ・SCP (Short Circuit Protection) and SCP-LATCH While OCP is operating, and ...

... only effective in preventing destruction from sudden accident. It does not support the continuous operation of the protection circuit (e.g. if a load, which significantly exceeds the output current capacitance, is connected). ・SCP (Short Circuit Protection) and SCP-LATCH While OCP is operating, and ...

H8CA-S - OMRON Kft.

... When “ MODE ” lights on display, terminals 1 and 3 are connected. In this case, it is not possible to preset values. Be sure to disconnect the terminals. The H8CA-S uses “regular read format,” so the preset values can be changed whether power is ON or OFF. ...

... When “ MODE ” lights on display, terminals 1 and 3 are connected. In this case, it is not possible to preset values. Be sure to disconnect the terminals. The H8CA-S uses “regular read format,” so the preset values can be changed whether power is ON or OFF. ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.