DS1831C/D/E 3.3V/2.5V Multisupply MicroMonitor FEATURES PIN ASSIGNMENT

... supply noise is minimized in the monitoring function, reducing false interrupts. See Figure 8 for the nonmaskable timing diagram. Versatile trip voltages can be configured by the use of an external resistor divider to divide the voltage at a sense point to the 1.25V trip levels of the referenced com ...

... supply noise is minimized in the monitoring function, reducing false interrupts. See Figure 8 for the nonmaskable timing diagram. Versatile trip voltages can be configured by the use of an external resistor divider to divide the voltage at a sense point to the 1.25V trip levels of the referenced com ...

Experiment 8

... When the source voltage is smaller than 0.7V, the voltage across the diodes will be equal to the source. When the source voltage is larger than 0.7V, the voltage across the diodes will be 0.7V. The sinusoidal source will be badly distorted into almost a square wave, but the voltage will not be a ...

... When the source voltage is smaller than 0.7V, the voltage across the diodes will be equal to the source. When the source voltage is larger than 0.7V, the voltage across the diodes will be 0.7V. The sinusoidal source will be badly distorted into almost a square wave, but the voltage will not be a ...

MAX11646/MAX11647 Low-Power, 1-/2-Channel, I C, 10-Bit ADCs in Ultra-Tiny 1.9mm x 2.2mm Package

... All WLP devices are 100% production tested at TA = +25°C. Specifications over temperature limits are guaranteed by design and characterization. Note 2: For DC accuracy, the MAX11646 is tested at VDD = 5V and the MAX11647 is tested at VDD = 3V, with an external reference for both ADCs. All devices ar ...

... All WLP devices are 100% production tested at TA = +25°C. Specifications over temperature limits are guaranteed by design and characterization. Note 2: For DC accuracy, the MAX11646 is tested at VDD = 5V and the MAX11647 is tested at VDD = 3V, with an external reference for both ADCs. All devices ar ...

Aiken--PhaseShiftOsc..

... impedance of the amplifier, so as to not load the output appreciably, which would reduce the gain, possibly to a point where it can no longer sustain oscillations. A good minimum value is around ten times the actual output impedance of the amplification stage. Since the input impedance is proportion ...

... impedance of the amplifier, so as to not load the output appreciably, which would reduce the gain, possibly to a point where it can no longer sustain oscillations. A good minimum value is around ten times the actual output impedance of the amplification stage. Since the input impedance is proportion ...

TPA032D03 数据资料 dataSheet 下载

... of power DMOS transistors to replicate the analog input signal through high-frequency switching of the output stage. This allows the TPA032D03 to be configured as a bridge-tied load (BTL) amplifier capable of delivering up to 10 W of continuous average power into a 4-Ω load at 0.5% THD+N from a 12-V ...

... of power DMOS transistors to replicate the analog input signal through high-frequency switching of the output stage. This allows the TPA032D03 to be configured as a bridge-tied load (BTL) amplifier capable of delivering up to 10 W of continuous average power into a 4-Ω load at 0.5% THD+N from a 12-V ...

TPS70302 数据资料 dataSheet 下载

... (that is, logic high) after a 120 ms delay when all three of the following conditions are met. First, VIN1 must be above the undervoltage condition. Second, the manual reset (MR) pin must be in a high impedance state. Third, VOUT2 must be above approximately 95% of its regulated voltage. To monitor ...

... (that is, logic high) after a 120 ms delay when all three of the following conditions are met. First, VIN1 must be above the undervoltage condition. Second, the manual reset (MR) pin must be in a high impedance state. Third, VOUT2 must be above approximately 95% of its regulated voltage. To monitor ...

Lab

... 3. Now measure the voltage drops on each of the 3 resistors and enter into the measured values section of the table. 4. Compare the measured values with your calculated values. Do they agree? If not, then either your measured values are incorrect or the calculated values are wrong. Recheck and repea ...

... 3. Now measure the voltage drops on each of the 3 resistors and enter into the measured values section of the table. 4. Compare the measured values with your calculated values. Do they agree? If not, then either your measured values are incorrect or the calculated values are wrong. Recheck and repea ...

1 MSPS, 12-Bit, Simultaneous Sampling AD7262 Data Sheet

... Analog Inputs of ADC A. True differential input pair. Analog Inputs of ADC B. True differential input pair. Reference Input/Output. Decoupling capacitors connect to these pins to decouple the internal reference buffer for each respective ADC. Typically, 1 μF capacitors are required to decouple the r ...

... Analog Inputs of ADC A. True differential input pair. Analog Inputs of ADC B. True differential input pair. Reference Input/Output. Decoupling capacitors connect to these pins to decouple the internal reference buffer for each respective ADC. Typically, 1 μF capacitors are required to decouple the r ...

Power Topology - Buck Converter

... A Type-III compensation loop comprises two poles and two zeros. The compensation network needs to be calculated and tested in detail to achieve a stable system with high bandwidth. Switching power supplies are sampled-data systems. A step-down converter is only limited in bandwidth by the switching ...

... A Type-III compensation loop comprises two poles and two zeros. The compensation network needs to be calculated and tested in detail to achieve a stable system with high bandwidth. Switching power supplies are sampled-data systems. A step-down converter is only limited in bandwidth by the switching ...

735/737 FEEDER PROTECTION SySTEM

... Block Instantaneous on Autoreclosure The 735/737 is capable of blocking instantaneous trips after an autoreclose operation. This prevents accidental trips caused by the high inrush currents typically experienced in these situations. The custom scheme switch allows this function to be enabled. The ph ...

... Block Instantaneous on Autoreclosure The 735/737 is capable of blocking instantaneous trips after an autoreclose operation. This prevents accidental trips caused by the high inrush currents typically experienced in these situations. The custom scheme switch allows this function to be enabled. The ph ...

MAX17017 - Part Number Search

... The main regulator can be configured as either a stepdown converter (for 2 to 4 Li+ cell applications) or as a step-up converter (for 1 Li+ cell applications). The internal switching regulators include 5V synchronous MOSFETs that can be powered directly from a single Li+ cell or from the main 3.3V/5 ...

... The main regulator can be configured as either a stepdown converter (for 2 to 4 Li+ cell applications) or as a step-up converter (for 1 Li+ cell applications). The internal switching regulators include 5V synchronous MOSFETs that can be powered directly from a single Li+ cell or from the main 3.3V/5 ...

Title : Feasible Performance Evaluations of Digitally

... the need for large number of isolated DC sources. One way to ease this problem is to have the highest voltage stage, also referred to by the main stage, constructed with a topology that uses one DC supply for the three phase branches instead of the three full bridge cells. Constructing multistage in ...

... the need for large number of isolated DC sources. One way to ease this problem is to have the highest voltage stage, also referred to by the main stage, constructed with a topology that uses one DC supply for the three phase branches instead of the three full bridge cells. Constructing multistage in ...

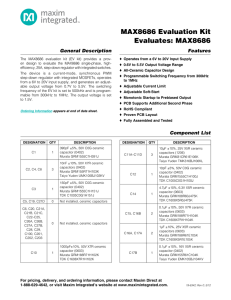

General Description Features

... changing the values of resistors R15 and R14. To determine the values of the resistor-divider, first select R15 and then use the following equation to calculate R14, where VOUT is the desired output. The sum of the two resistors should exceed 165kI. R14 = R15 x (3.3V/ VOUT - 1) If the desired output ...

... changing the values of resistors R15 and R14. To determine the values of the resistor-divider, first select R15 and then use the following equation to calculate R14, where VOUT is the desired output. The sum of the two resistors should exceed 165kI. R14 = R15 x (3.3V/ VOUT - 1) If the desired output ...

A low-phase-noise LC-VCO with an enhanced

... of a five bit DSCA and a two bit DSVA for a wide tuning range with KVCO equalization over different sub-bands. The proposed DSCA is shown in Fig. 3(b), two symmetrical MIM caps C are controlled by switching MN1 on and off. In order to avoid floating DC of C, this degrades phase noise because MN1 wor ...

... of a five bit DSCA and a two bit DSVA for a wide tuning range with KVCO equalization over different sub-bands. The proposed DSCA is shown in Fig. 3(b), two symmetrical MIM caps C are controlled by switching MN1 on and off. In order to avoid floating DC of C, this degrades phase noise because MN1 wor ...

VCA820 数据资料 dataSheet 下载

... voltage-controlled gain amplifier. It provides a differential input to single-ended conversion with a high-impedance gain control input used to vary the gain down 40dB from the nominal maximum gain set by the gain resistor (RG) and feedback resistor (RF). The VCA820 internal architecture consists of ...

... voltage-controlled gain amplifier. It provides a differential input to single-ended conversion with a high-impedance gain control input used to vary the gain down 40dB from the nominal maximum gain set by the gain resistor (RG) and feedback resistor (RF). The VCA820 internal architecture consists of ...

ADM1085 数据手册DataSheet 下载

... ADM1088 are related to the VIN and enable inputs by a simple AND function. The enable output is asserted only if the enable input is asserted and the voltage at VIN is above VTH_RISING, with the time delay elapsed. Table 5 and Table 6 show the enable output logic states for different VIN/enable inpu ...

... ADM1088 are related to the VIN and enable inputs by a simple AND function. The enable output is asserted only if the enable input is asserted and the voltage at VIN is above VTH_RISING, with the time delay elapsed. Table 5 and Table 6 show the enable output logic states for different VIN/enable inpu ...

DS709

... The number of output clocks is user-configurable. The maximum number allowed depends upon the selected device and the interaction of the major clocking features you specify. Users can simply input their desired timing parameters (frequency, phase, and duty cycle) and let the clocking wizard select a ...

... The number of output clocks is user-configurable. The maximum number allowed depends upon the selected device and the interaction of the major clocking features you specify. Users can simply input their desired timing parameters (frequency, phase, and duty cycle) and let the clocking wizard select a ...

SN65LVEL11 数据资料 dataSheet 下载

... Maximum switching frequency measured at output amplitude of 300 mVpp. Within-device skew is defined as identical transitions on similar paths through a device. Device-Device Skew is defined as identical transitions at identical Vcc levels. Duty cycle skew is the difference between a tPLH and tPHL pr ...

... Maximum switching frequency measured at output amplitude of 300 mVpp. Within-device skew is defined as identical transitions on similar paths through a device. Device-Device Skew is defined as identical transitions at identical Vcc levels. Duty cycle skew is the difference between a tPLH and tPHL pr ...

Integrating ADC

An integrating ADC is a type of analog-to-digital converter that converts an unknown input voltage into a digital representation through the use of an integrator. In its most basic implementation, the unknown input voltage is applied to the input of the integrator and allowed to ramp for a fixed time period (the run-up period). Then a known reference voltage of opposite polarity is applied to the integrator and is allowed to ramp until the integrator output returns to zero (the run-down period). The input voltage is computed as a function of the reference voltage, the constant run-up time period, and the measured run-down time period. The run-down time measurement is usually made in units of the converter's clock, so longer integration times allow for higher resolutions. Likewise, the speed of the converter can be improved by sacrificing resolution.Converters of this type can achieve high resolution, but often do so at the expense of speed. For this reason, these converters are not found in audio or signal processing applications. Their use is typically limited to digital voltmeters and other instruments requiring highly accurate measurements.