EEE 120-3741

... multilevel inverter structure consists of the Hbridges connected in series. Then, the diodeclamped multilevel inverter was emerged. It employs the capacitors connected in series to separate the DC bus voltage in different levels. In 1992, the capacitor clamped multilevel inverter was introduced .Thi ...

... multilevel inverter structure consists of the Hbridges connected in series. Then, the diodeclamped multilevel inverter was emerged. It employs the capacitors connected in series to separate the DC bus voltage in different levels. In 1992, the capacitor clamped multilevel inverter was introduced .Thi ...

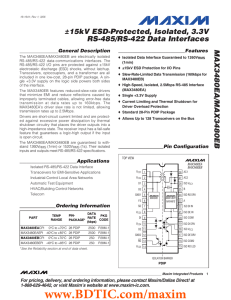

MAX3480EA/MAX3480EB ±15kV ESD-Protected, Isolated, 3.3V RS-485/RS-422 Data Interfaces General Description

... Transceivers, optocouplers, and a transformer are all included in one low-cost, 28-pin PDIP package. A single +3.3V supply on the logic side powers both sides of the interface. The MAX3480EB features reduced-slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated c ...

... Transceivers, optocouplers, and a transformer are all included in one low-cost, 28-pin PDIP package. A single +3.3V supply on the logic side powers both sides of the interface. The MAX3480EB features reduced-slew-rate drivers that minimize EMI and reduce reflections caused by improperly terminated c ...

BD8162AEKV

... mounted on the input side. For this reason, it is recommended to use low-ESR capacitors above 10µF and below 100mΩ as the input capacitors. Using input capacitors outside of this range may superimpose excess ripple voltage upon the input voltage, causing the IC to malfunction. However, since the afo ...

... mounted on the input side. For this reason, it is recommended to use low-ESR capacitors above 10µF and below 100mΩ as the input capacitors. Using input capacitors outside of this range may superimpose excess ripple voltage upon the input voltage, causing the IC to malfunction. However, since the afo ...

Very high accuracy (25 µV) high bandwidth (3 MHz) zero drift 5 V

... Higher accuracy without calibration Accuracy virtually unaffected by temperature change ...

... Higher accuracy without calibration Accuracy virtually unaffected by temperature change ...

AL8806 Description Pin Assignments

... This rising current produces a voltage ramp across RSET. The internal circuit of the AL8806 senses the voltage across RSET and applies a proportional voltage to the input of the internal comparator. When this voltage reaches an internally set upper threshold, the internal switch is turned off. The i ...

... This rising current produces a voltage ramp across RSET. The internal circuit of the AL8806 senses the voltage across RSET and applies a proportional voltage to the input of the internal comparator. When this voltage reaches an internally set upper threshold, the internal switch is turned off. The i ...

General Description Features

... The DS3923 high-speed current mirror integrates highvoltage devices necessary for monitoring the burst-mode receive power signal in avalanche photodiode (APD) biasing and optical line terminal (OLT) applications. It provides small and large gain current mirror outputs to monitor the APD current. A s ...

... The DS3923 high-speed current mirror integrates highvoltage devices necessary for monitoring the burst-mode receive power signal in avalanche photodiode (APD) biasing and optical line terminal (OLT) applications. It provides small and large gain current mirror outputs to monitor the APD current. A s ...

DAC312 数据手册DataSheet 下载

... The DAC312 series of 12-bit multiplying digital-to-analog converters provide high speed with guaranteed performance to 0.012% differential nonlinearity over the full commercial operating temperature range. The DAC312 combines a 9-bit master D/A converter with a 3-bit (MSBs) segment generator to form ...

... The DAC312 series of 12-bit multiplying digital-to-analog converters provide high speed with guaranteed performance to 0.012% differential nonlinearity over the full commercial operating temperature range. The DAC312 combines a 9-bit master D/A converter with a 3-bit (MSBs) segment generator to form ...

A High Swing Range, High Bandwidth CMOS PGA and ADC for IF

... Second, the output common mode feedback circuit at Fig. 6. must process the continuos diffential output signal and the large operation range. It means that if the common signal of the PGA differential output is low or high, the output common mode voltage must be maintained the half power voltage. It ...

... Second, the output common mode feedback circuit at Fig. 6. must process the continuos diffential output signal and the large operation range. It means that if the common signal of the PGA differential output is low or high, the output common mode voltage must be maintained the half power voltage. It ...

... normal mode and common mode rejection. The meter measures bipolar true differential and single-ended DC voltages over four factory calibrated ranges from ±1.9999V to ±1200.0V full scale. Resolution is 100µV over ±19999 counts, and errors due to zero drift are virtually eliminated by means of autozer ...

Document

... current IL flows through the load and this is assumed to be constant. At the same time SCR short circuits the LC combination which starts oscillating. A current ‘i’ starts flowing in the direction shown in figure. As ‘i’ reaches its maximum value, the capacitor voltage reduces to zero and then the p ...

... current IL flows through the load and this is assumed to be constant. At the same time SCR short circuits the LC combination which starts oscillating. A current ‘i’ starts flowing in the direction shown in figure. As ‘i’ reaches its maximum value, the capacitor voltage reduces to zero and then the p ...

XC1700Product Specification V4.0 (1/96)

... driving RESET/OE from LDC or system reset — assume that the Serial PROM internal power-on-reset is always in step with the FPGA’s internal power-onreset, which may not be a safe assumption. • The CE input of the lead (or only) Serial PROM is driven by the DONE/PRGM or DONE output of the lead FPGA de ...

... driving RESET/OE from LDC or system reset — assume that the Serial PROM internal power-on-reset is always in step with the FPGA’s internal power-onreset, which may not be a safe assumption. • The CE input of the lead (or only) Serial PROM is driven by the DONE/PRGM or DONE output of the lead FPGA de ...

AAT1235 数据资料DataSheet下载

... hysteresis threshold, which determines the inductor ripple current. Peak current is adjusted by the controller until the desired LED output current level is met. The magnitude of the feedback error signal determines the average input current. Therefore, the AAT1235 controller implements a programmed ...

... hysteresis threshold, which determines the inductor ripple current. Peak current is adjusted by the controller until the desired LED output current level is met. The magnitude of the feedback error signal determines the average input current. Therefore, the AAT1235 controller implements a programmed ...

UMC5N Features Mechanical Data

... Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein: A. Life support devices or systems are devices or systems which: ...

... Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein: A. Life support devices or systems are devices or systems which: ...

36-V, Low-Power, Precision, CMOS, RRIO, Low Offset, Low Input

... – Single in SOIC-8, SOT-5, and VSSOP-8 – Dual in SOIC-8 and VSSOP-8 – Quad in SOIC-14 and TSSOP-14 ...

... – Single in SOIC-8, SOT-5, and VSSOP-8 – Dual in SOIC-8 and VSSOP-8 – Quad in SOIC-14 and TSSOP-14 ...

MAX9218 27-Bit, 3MHz-to-35MHz DC-Balanced LVDS Deserializer General Description

... LVTTL/LVCMOS Output Enable Input. High activates the single-ended outputs. Driving low places the single-ended outputs in high impedance. Internally pulled down to GND. LVTTL/LVCMOS Control Data Outputs. CNTL_OUT[8:0] are latched into the next chip on the rising or falling edge of PCLK_OUT as select ...

... LVTTL/LVCMOS Output Enable Input. High activates the single-ended outputs. Driving low places the single-ended outputs in high impedance. Internally pulled down to GND. LVTTL/LVCMOS Control Data Outputs. CNTL_OUT[8:0] are latched into the next chip on the rising or falling edge of PCLK_OUT as select ...

0.5 – 6 GHz Low Noise GaAs MMIC Amplifier Technical Data MGA-86563

... matching circuit to the output will increase the gain and output power by 0.5 to 1.5 dB. The output matching circuit will not effect the noise figure. A small value resistor placed in series with the Vdd line may be useful to “de-Q” the bias circuit. Typical values of R1 are in the 10 Ω to 100 Ω ran ...

... matching circuit to the output will increase the gain and output power by 0.5 to 1.5 dB. The output matching circuit will not effect the noise figure. A small value resistor placed in series with the Vdd line may be useful to “de-Q” the bias circuit. Typical values of R1 are in the 10 Ω to 100 Ω ran ...

EEAP 245_Due: February 2, 1998

... waveform. The trigger system insures that the start of each sweep is synchronized to the waveform being displayed. Figure 5 shows three consecutive displays of a waveform. The point at which a display (also called a sweep) is started is called the trigger point and is defined by the level and the si ...

... waveform. The trigger system insures that the start of each sweep is synchronized to the waveform being displayed. Figure 5 shows three consecutive displays of a waveform. The point at which a display (also called a sweep) is started is called the trigger point and is defined by the level and the si ...

cdv/dt induced turn-on in synchronous buck regulators

... A more effective way of solving the Cdv/dt induced turnon problem is to implement an AC gate drive for Q2. An example of implementing an AC gate drive can be found in the schematic of Figure 9. As shown in Figure 9, an AC coupling capacitor and a gate-to-source resistor are added to the gate of Q2. ...

... A more effective way of solving the Cdv/dt induced turnon problem is to implement an AC gate drive for Q2. An example of implementing an AC gate drive can be found in the schematic of Figure 9. As shown in Figure 9, an AC coupling capacitor and a gate-to-source resistor are added to the gate of Q2. ...

LT1993-4

... Amplifier/ADC driver for use in applications from DC to 900MHz. The LT1993-4 has been designed for ease of use, with minimal support circuitry required. Exceptionally low input-referred noise and low distortion products (with either single-ended or differential inputs) make the LT1993-4 an excellent ...

... Amplifier/ADC driver for use in applications from DC to 900MHz. The LT1993-4 has been designed for ease of use, with minimal support circuitry required. Exceptionally low input-referred noise and low distortion products (with either single-ended or differential inputs) make the LT1993-4 an excellent ...

Schmitt trigger

In electronics a Schmitt trigger is a comparator circuit with hysteresis implemented by applying positive feedback to the noninverting input of a comparator or differential amplifier. It is an active circuit which converts an analog input signal to a digital output signal. The circuit is named a ""trigger"" because the output retains its value until the input changes sufficiently to trigger a change. In the non-inverting configuration, when the input is higher than a chosen threshold, the output is high. When the input is below a different (lower) chosen threshold the output is low, and when the input is between the two levels the output retains its value. This dual threshold action is called hysteresis and implies that the Schmitt trigger possesses memory and can act as a bistable multivibrator (latch or flip-flop). There is a close relation between the two kinds of circuits: a Schmitt trigger can be converted into a latch and a latch can be converted into a Schmitt trigger.Schmitt trigger devices are typically used in signal conditioning applications to remove noise from signals used in digital circuits, particularly mechanical contact bounce. They are also used in closed loop negative feedback configurations to implement relaxation oscillators, used in function generators and switching power supplies.