Data Sheet

... determined by regulator‘s feedback threshold accuracy and is independent of the LEDs‘ forward voltage variation. So the precise resistors are the better choices. The resistance of R5 is in inverse proportion to the LED current since the feedback reference is fixed at 0.5V. The relation of R5 and the ...

... determined by regulator‘s feedback threshold accuracy and is independent of the LEDs‘ forward voltage variation. So the precise resistors are the better choices. The resistance of R5 is in inverse proportion to the LED current since the feedback reference is fixed at 0.5V. The relation of R5 and the ...

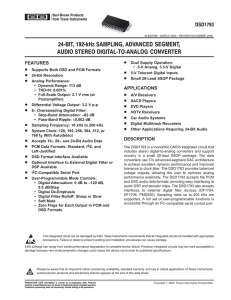

24-Bit 192kHz Sampling Advanced Segment Audio Stereo DAC

... The DSD1793 requires a system clock for operating the digital interpolation filters and advanced segment DAC modulators. The system clock is applied at the SCK input (pin 5). The DSD1793 has a system clock detection circuit that automatically senses which frequency the system clock is operating. Tab ...

... The DSD1793 requires a system clock for operating the digital interpolation filters and advanced segment DAC modulators. The system clock is applied at the SCK input (pin 5). The DSD1793 has a system clock detection circuit that automatically senses which frequency the system clock is operating. Tab ...

XIO1100 Data Manual (Rev. C)

... Specification). P1 is used for the Disabled state, all Detect states, and L1.Idle state of the Link Training and Status State Machine (LTSSM). While in P1 state, the optional P1_SLEEP input signal can be used to reduce even more power consumption by disabling the RX_CLK signal. However, the P1_SLEEP ...

... Specification). P1 is used for the Disabled state, all Detect states, and L1.Idle state of the Link Training and Status State Machine (LTSSM). While in P1 state, the optional P1_SLEEP input signal can be used to reduce even more power consumption by disabling the RX_CLK signal. However, the P1_SLEEP ...

$doc.title

... Supply voltage VDD + (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 V Supply voltage VDD − (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

... Supply voltage VDD + (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8 V Supply voltage VDD − (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Operational Amplifiers: Chapter 2 (Horenstein)

... Consider a case with an infinitely long 4V pulse – The capacitor will continue to charge linearly in time, but will eventually reach 10V which will force vOUT to –10V (= VNEG) and saturate the op-amp (at 12.5 ms) – After this time, the op-amp will no longer be able to maintain v- at 0 volts – Since ...

... Consider a case with an infinitely long 4V pulse – The capacitor will continue to charge linearly in time, but will eventually reach 10V which will force vOUT to –10V (= VNEG) and saturate the op-amp (at 12.5 ms) – After this time, the op-amp will no longer be able to maintain v- at 0 volts – Since ...

Data Sheet Features (Continued) General Description

... The CS5519 is a low-cost high-resolution single chip solution for APA capacitive touch screen. It is an 8-bit single cycle 8051 microcontroller with I2C Interface. The chip includes 8-bit successive approximation analog-to-digital converters with an I2C interface and multiplexer-switcher circuits fo ...

... The CS5519 is a low-cost high-resolution single chip solution for APA capacitive touch screen. It is an 8-bit single cycle 8051 microcontroller with I2C Interface. The chip includes 8-bit successive approximation analog-to-digital converters with an I2C interface and multiplexer-switcher circuits fo ...

QUADRUPLE OPERATIONAL AMPLIFIER LM2902-EP FEATURES

... This device consists of four independent high-gain frequency-compensated operational amplifiers that are designed specifically to operate from a single supply over a wide range of voltages. Operation from split supplies is possible when the difference between the two supplies is 3 V to 26 V (3 V to ...

... This device consists of four independent high-gain frequency-compensated operational amplifiers that are designed specifically to operate from a single supply over a wide range of voltages. Operation from split supplies is possible when the difference between the two supplies is 3 V to 26 V (3 V to ...

ADM3485E 数据手册DataSheet 下载

... The ADM3485E is a 3.3 V, low power data transceiver with ±15 kV ESD protection, suitable for half-duplex communication on multipoint bus transmission lines. The ADM3485E is designed for balanced data transmission and complies with TIA/EIA standards RS485 and RS-422. The ADM3485E is a half-duplex tr ...

... The ADM3485E is a 3.3 V, low power data transceiver with ±15 kV ESD protection, suitable for half-duplex communication on multipoint bus transmission lines. The ADM3485E is designed for balanced data transmission and complies with TIA/EIA standards RS485 and RS-422. The ADM3485E is a half-duplex tr ...

A Low-Power High-Precision Comparator With Time-Domain Bulk-Tuned Offset Cancellation

... proposed other ways to cancel the offset of comparators. A common approach is to intentionally introduce imbalances to the circuit to counterbalance the offset. This imbalance can be realized by charge injection at latch nodes [11], binary-weighted capacitor arrays as the load [12], or current sourc ...

... proposed other ways to cancel the offset of comparators. A common approach is to intentionally introduce imbalances to the circuit to counterbalance the offset. This imbalance can be realized by charge injection at latch nodes [11], binary-weighted capacitor arrays as the load [12], or current sourc ...

MAX1687 Step-Up DC-DC Converters with Precise, Adaptive Current Limit for GSM General Description

... output voltage is sampled by the MAX1688. This voltage controls the peak inductor current. The greater the difference between the regulated output voltage and the valley of the sag voltage, the higher the peak current. This results in a constant recharge time that compensates for varying output filt ...

... output voltage is sampled by the MAX1688. This voltage controls the peak inductor current. The greater the difference between the regulated output voltage and the valley of the sag voltage, the higher the peak current. This results in a constant recharge time that compensates for varying output filt ...

BQ24313 数据资料 dataSheet 下载

... The bq24313 and bq24315 are integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current and the battery voltage. For an input overvoltage condition, the IC immediately removes power fr ...

... The bq24313 and bq24315 are integrated circuits designed to provide protection to Li-ion batteries from failures of the charging circuit. The IC continuously monitors the input voltage, the input current and the battery voltage. For an input overvoltage condition, the IC immediately removes power fr ...

TPS543x 3-A, Wide Input Range, Step-Down

... ENA pin is floating. The TPS543x includes an internal slow-start circuit that slows the output rise time during start up to reduce in rush current and output voltage overshoot. The minimum output voltage is the internal 1.221-V feedback reference. Output overvoltage transients are minimized by an Ov ...

... ENA pin is floating. The TPS543x includes an internal slow-start circuit that slows the output rise time during start up to reduce in rush current and output voltage overshoot. The minimum output voltage is the internal 1.221-V feedback reference. Output overvoltage transients are minimized by an Ov ...

SN74GTL2003 数据资料 dataSheet 下载

... All transistors in the SN74GTL2003 have the same electrical characteristics, and there is minimal deviation from one output to another in voltage or propagation delay. This offers superior matching over discrete transistor voltage-translation solutions where the fabrication of the transistors is not ...

... All transistors in the SN74GTL2003 have the same electrical characteristics, and there is minimal deviation from one output to another in voltage or propagation delay. This offers superior matching over discrete transistor voltage-translation solutions where the fabrication of the transistors is not ...

STPMS2

... IEC 62053-21, IEC 62053-22 and IEC 6205323 standards specs for class 1, class 0.5 and class 0.2 AC watt meters ...

... IEC 62053-21, IEC 62053-22 and IEC 6205323 standards specs for class 1, class 0.5 and class 0.2 AC watt meters ...

Analog-to-digital converter

An analog-to-digital converter (ADC, A/D, or A to D) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity's amplitude.The conversion involves quantization of the input, so it necessarily introduces a small amount of error. Furthermore, instead of continuously performing the conversion, an ADC does the conversion periodically, sampling the input. The result is a sequence of digital values that have been converted from a continuous-time and continuous-amplitude analog signal to a discrete-time and discrete-amplitude digital signal.An ADC is defined by its bandwidth (the range of frequencies it can measure) and its signal to noise ratio (how accurately it can measure a signal relative to the noise it introduces). The actual bandwidth of an ADC is characterized primarily by its sampling rate, and to a lesser extent by how it handles errors such as aliasing. The dynamic range of an ADC is influenced by many factors, including the resolution (the number of output levels it can quantize a signal to), linearity and accuracy (how well the quantization levels match the true analog signal) and jitter (small timing errors that introduce additional noise). The dynamic range of an ADC is often summarized in terms of its effective number of bits (ENOB), the number of bits of each measure it returns that are on average not noise. An ideal ADC has an ENOB equal to its resolution. ADCs are chosen to match the bandwidth and required signal to noise ratio of the signal to be quantized. If an ADC operates at a sampling rate greater than twice the bandwidth of the signal, then perfect reconstruction is possible given an ideal ADC and neglecting quantization error. The presence of quantization error limits the dynamic range of even an ideal ADC, however, if the dynamic range of the ADC exceeds that of the input signal, its effects may be neglected resulting in an essentially perfect digital representation of the input signal.An ADC may also provide an isolated measurement such as an electronic device that converts an input analog voltage or current to a digital number proportional to the magnitude of the voltage or current. However, some non-electronic or only partially electronic devices, such as rotary encoders, can also be considered ADCs. The digital output may use different coding schemes. Typically the digital output will be a two's complement binary number that is proportional to the input, but there are other possibilities. An encoder, for example, might output a Gray code.The inverse operation is performed by a digital-to-analog converter (DAC).