AD7792 数据手册DataSheet下载

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

... is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and, as such, are independent of external bus loading capacitances. 6 RDY returns high after a ...

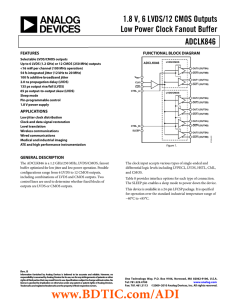

1.8 V, 6 LVDS/12 CMOS Outputs Low Power Clock Fanout Buffer ADCLK846

... The clock input accepts various types of single-ended and differential logic levels including LVPECL, LVDS, HSTL, CML, and CMOS. Table 8 provides interface options for each type of connection. The SLEEP pin enables a sleep mode to power down the device. This device is available in a 24-pin LFCSP pac ...

... The clock input accepts various types of single-ended and differential logic levels including LVPECL, LVDS, HSTL, CML, and CMOS. Table 8 provides interface options for each type of connection. The SLEEP pin enables a sleep mode to power down the device. This device is available in a 24-pin LFCSP pac ...

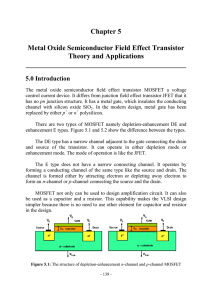

Sedra/Smith Microelectronic Circuits 5/e

... Y The Ro ≈ RC is moderate to high in value (typically, in the kilohms to tens kilohms range). Reducing RD to lower Ro is not a viable proportional, because the Av is also reduced. Z The open circuit voltage gain Avo can be hig, making the CS configration the work-hourse in MOS amplifier design. Howe ...

... Y The Ro ≈ RC is moderate to high in value (typically, in the kilohms to tens kilohms range). Reducing RD to lower Ro is not a viable proportional, because the Av is also reduced. Z The open circuit voltage gain Avo can be hig, making the CS configration the work-hourse in MOS amplifier design. Howe ...

LTM8055 - Linear Technology

... = 58mV. This feature is generally useful only if a current sense resistor is applied between VOUT and IOUT. IINMON (Pin L3): Input Current Monitor. This pin produces a voltage that is proportional to the voltage between IIN and VIN. IINMON will equal 1V when IIN – VIN = 50mV. This feature is general ...

... = 58mV. This feature is generally useful only if a current sense resistor is applied between VOUT and IOUT. IINMON (Pin L3): Input Current Monitor. This pin produces a voltage that is proportional to the voltage between IIN and VIN. IINMON will equal 1V when IIN – VIN = 50mV. This feature is general ...

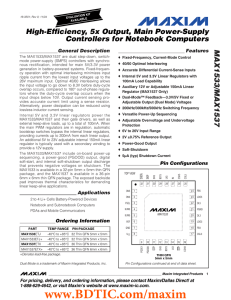

MAX1533/MAX1537 High-Efficiency, 5x Output, Main Power-Supply Controllers for Notebook Computers General Description

... overlap occurs, compared to 180° out-of-phase regulators where the duty-cycle overlap occurs when the input drops below 10V. Output current sensing provides accurate current limit using a sense resistor. Alternatively, power dissipation can be reduced using lossless inductor current sensing. Interna ...

... overlap occurs, compared to 180° out-of-phase regulators where the duty-cycle overlap occurs when the input drops below 10V. Output current sensing provides accurate current limit using a sense resistor. Alternatively, power dissipation can be reduced using lossless inductor current sensing. Interna ...

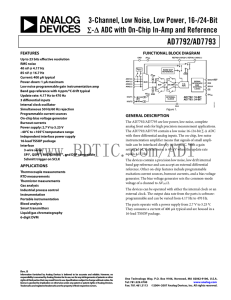

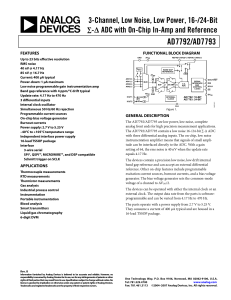

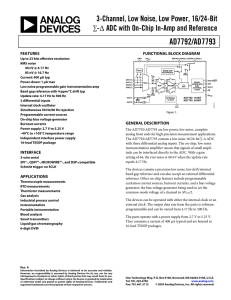

AD7792/AD7793 3-Channel, Low Noise, Low Power, 16/24-Bit ∑

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

... with all data transmitted in a continuous train of pulses. Alternatively, it can be a noncontinuous clock with the information being transmitted to or from the ADC in smaller batches of data. Clock In/Clock Out. The internal clock can be made available at this pin. Alternatively, the internal clock ...

DRV5013 Digital-Latch Hall Effect Sensor (Rev. H)

... with superior sensitivity stability over temperature and integrated protection features. The magnetic field is indicated via a digital bipolar latch output. The IC has an open-drain output stage with 30-mA current sink capability. A wide operating voltage range from 2.5 to 38 V with reverse polarity ...

... with superior sensitivity stability over temperature and integrated protection features. The magnetic field is indicated via a digital bipolar latch output. The IC has an open-drain output stage with 30-mA current sink capability. A wide operating voltage range from 2.5 to 38 V with reverse polarity ...

74VCX245 Low Voltage Bidirectional Transceiver with 3.6V Tolerant Inputs and Outputs 7

... DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support de ...

... DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein: 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support de ...

AD9865

... solutions. Power saving modes include the ability to reduce power consumption of individual functional blocks, or to power down unused blocks in half-duplex applications. A serial port interface (SPI®) allows software programming of the various functional blocks. An on-chip PLL clock multiplier and ...

... solutions. Power saving modes include the ability to reduce power consumption of individual functional blocks, or to power down unused blocks in half-duplex applications. A serial port interface (SPI®) allows software programming of the various functional blocks. An on-chip PLL clock multiplier and ...

Design of a 14-bit fully differential discrete time delta

... possible way been a part of this project. And above all I would like to thank my parents and God, without their blessing and encouragement this thesis would not have been possible. I know they are always there for me and always help me get out of all intriguing situations I get myself into. ...

... possible way been a part of this project. And above all I would like to thank my parents and God, without their blessing and encouragement this thesis would not have been possible. I know they are always there for me and always help me get out of all intriguing situations I get myself into. ...