Level Conversion for Dual-Supply Systems

... layout placement restrictions of the level converter [12]. The performance comparison between these two asynchronous level converters will be discussed in Section III-B. The half-latch topology contains small number of transistors and is a promising level converter to minimize delay, power, and area ...

... layout placement restrictions of the level converter [12]. The performance comparison between these two asynchronous level converters will be discussed in Section III-B. The half-latch topology contains small number of transistors and is a promising level converter to minimize delay, power, and area ...

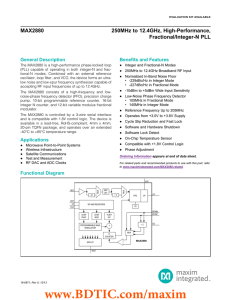

MAX2880 General Description Benefits and Features

... (PLL) capable of operating in both integer-N and fractional-N modes. Combined with an external reference oscillator, loop filter, and VCO, the device forms an ultralow noise and low-spur frequency synthesizer capable of accepting RF input frequencies of up to 12.4GHz. ...

... (PLL) capable of operating in both integer-N and fractional-N modes. Combined with an external reference oscillator, loop filter, and VCO, the device forms an ultralow noise and low-spur frequency synthesizer capable of accepting RF input frequencies of up to 12.4GHz. ...

IOSR Journal of Electronics and Communication Engineering (IOSR-JECE)

... when transmitting high-speed electrical signal, the EM fields for the signal trace and the return current on the ground plane have the potential to cause electrical interference on adjacent circuits. Furthermore with digital system going for lower operating voltage, logic signal swing and noise marg ...

... when transmitting high-speed electrical signal, the EM fields for the signal trace and the return current on the ground plane have the potential to cause electrical interference on adjacent circuits. Furthermore with digital system going for lower operating voltage, logic signal swing and noise marg ...

8 Serial digital interfaces

... Figure 7-1: HPC interface arrangement ................................................................................ 47 Figure 7-2: LPC active signal output voltage vs. load current ............................................... 49 Figure 7-3: LPC-P and LPC-S interface arrangement ............... ...

... Figure 7-1: HPC interface arrangement ................................................................................ 47 Figure 7-2: LPC active signal output voltage vs. load current ............................................... 49 Figure 7-3: LPC-P and LPC-S interface arrangement ............... ...

PDF: 410KB

... switching current flows on this route. In addition, please add a bypass condenser Co’ with good frequency response such as a polypropylene film condenser closely to the P and N terminals. ・The two IGBT emitters are connected to the VNO terminal of LVIC inside the DIP-PFC. If the internal wiring indu ...

... switching current flows on this route. In addition, please add a bypass condenser Co’ with good frequency response such as a polypropylene film condenser closely to the P and N terminals. ・The two IGBT emitters are connected to the VNO terminal of LVIC inside the DIP-PFC. If the internal wiring indu ...

DIP-PFC APPLICATION NOTE MITSUBISHI ELECTRIC CORPORATION POWER SEMICONDUCTOR

... switching current flows on this route. In addition, please add a bypass condenser Co’ with good frequency response such as a polypropylene film condenser closely to the P and N terminals. ・The two IGBT emitters are connected to the VNO terminal of LVIC inside the DIP-PFC. If the internal wiring indu ...

... switching current flows on this route. In addition, please add a bypass condenser Co’ with good frequency response such as a polypropylene film condenser closely to the P and N terminals. ・The two IGBT emitters are connected to the VNO terminal of LVIC inside the DIP-PFC. If the internal wiring indu ...

MAX1446 10-Bit, 60Msps, 3.0V, Low-Power ADC with Internal Reference General Description

... 19-1729; Rev 4; 11/08 ...

... 19-1729; Rev 4; 11/08 ...

Document

... Norton’s Theorem: any circuit built of sources and resistors can be represented by one current source (Thevenin Current ) and a resistance in parallel (Thevenin Resistance). ...

... Norton’s Theorem: any circuit built of sources and resistors can be represented by one current source (Thevenin Current ) and a resistance in parallel (Thevenin Resistance). ...

ADC音频放大器系列SSM2319 数据手册DataSheet 下载

... RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 2.5 V RL = 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V RL = 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V RL = 8 Ω, THD = 10%, f = 1 k ...

... RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V RL = 8 Ω, THD = 1%, f = 1 kHz, 20 kHz BW, VDD = 2.5 V RL = 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 5.0 V RL = 8 Ω, THD = 10%, f = 1 kHz, 20 kHz BW, VDD = 3.6 V RL = 8 Ω, THD = 10%, f = 1 k ...

ADS5204 数据资料 dataSheet 下载

... Negative Input for the Analog B Channel Positive Input for the Analog B Channel Reference Voltage Top. The voltage at this terminal defines the top reference voltage for the ADC. Sufficient filtering should be applied to this input: the use of 0.1µF capacitor between REFT and AVSS is highly recommen ...

... Negative Input for the Analog B Channel Positive Input for the Analog B Channel Reference Voltage Top. The voltage at this terminal defines the top reference voltage for the ADC. Sufficient filtering should be applied to this input: the use of 0.1µF capacitor between REFT and AVSS is highly recommen ...