Understanding Pressure Measuring with Overview on Sensor Signal

... This guide is intended to give some practical notions on the way of designing the material interface between the sensor and the microcontroller. It focus on circuit used to do the signal conditioning. In the different chapters, various applications are explained. Most of them are from common industr ...

... This guide is intended to give some practical notions on the way of designing the material interface between the sensor and the microcontroller. It focus on circuit used to do the signal conditioning. In the different chapters, various applications are explained. Most of them are from common industr ...

MAX19793 1500MHz to 6000MHz Dual Analog Voltage Variable

... Note 5: Production tested at TC = +100NC. All other temperatures are guaranteed by design and characterization. Note 6: Recommended functional range. Not production tested. Operation outside this range is possible, but with degraded performance of some parameters. Note 7: All limits include exter ...

... Note 5: Production tested at TC = +100NC. All other temperatures are guaranteed by design and characterization. Note 6: Recommended functional range. Not production tested. Operation outside this range is possible, but with degraded performance of some parameters. Note 7: All limits include exter ...

Ch9-12

... Similar to its bipolar counterpart, the output impedance of a MOS cascode amplifier can be improved by using a PMOS cascode current source. CH 9 Cascode Stages and Current Mirrors ...

... Similar to its bipolar counterpart, the output impedance of a MOS cascode amplifier can be improved by using a PMOS cascode current source. CH 9 Cascode Stages and Current Mirrors ...

MAX11156 18-Bit, 500ksps, ±5V SAR ADC with Internal Reference in TDFN General Description

... (VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 500kHz, VREF = 4.096V, Reference Mode 3; TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25NC.) (Note 2) Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a tempera ...

... (VDD = 4.75V to 5.25V, VOVDD = 2.3V to 5.25V, fSAMPLE = 500kHz, VREF = 4.096V, Reference Mode 3; TA = TMIN to TMAX, unless otherwise noted. Typical values are at TA = +25NC.) (Note 2) Note 2: Maximum and minimum limits are fully production tested over specified supply voltage range and at a tempera ...

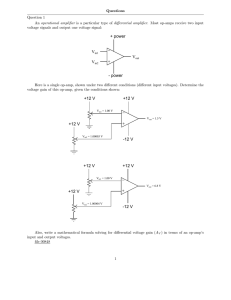

12 V +12 V +12 V

... the student expects to measure 0 volts DC at the output of the op-amp. This is what the DC voltmeter registers, but when set to AC, it registers substantial AC voltage! Now this is strange. How can a simple voltage buffer output alternating current when its input is grounded and the power supply is ...

... the student expects to measure 0 volts DC at the output of the op-amp. This is what the DC voltmeter registers, but when set to AC, it registers substantial AC voltage! Now this is strange. How can a simple voltage buffer output alternating current when its input is grounded and the power supply is ...

The Physics of Implantable Devices

... The voltage gradient results in current flow The size of the current depends on the tissue impedance Also known as the “Shock impedance” High impedance- low current Low impedance- high current o Shock Impedance is smaller then the Pacing Impedance ...

... The voltage gradient results in current flow The size of the current depends on the tissue impedance Also known as the “Shock impedance” High impedance- low current Low impedance- high current o Shock Impedance is smaller then the Pacing Impedance ...

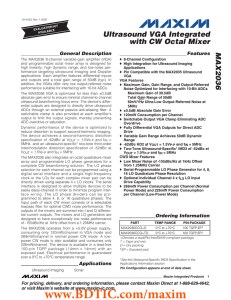

General Description Features

... input impedance of the pin causes there to be a period of time (related to the RC time constant) when the DC level on the chip side of the capacitor is outside the acceptable common-mode range and the LO swing does not exceed both the logic thresholds required for proper operation. This problem asso ...

... input impedance of the pin causes there to be a period of time (related to the RC time constant) when the DC level on the chip side of the capacitor is outside the acceptable common-mode range and the LO swing does not exceed both the logic thresholds required for proper operation. This problem asso ...

Chapter 2 - Part 1 - PPT - Mano & Kime

... outputs, overcoming the problem of the limited inputs to the PAL Ors • Some PLAs have outputs that can be complemented, adding POS functions Chapter 6 - Part 4 ...

... outputs, overcoming the problem of the limited inputs to the PAL Ors • Some PLAs have outputs that can be complemented, adding POS functions Chapter 6 - Part 4 ...

ADITYA COLLEGE OF ENGG.MADANAPALLE (ACEM) III B.Tech., I

... CMOS AND-OR-INVERT(A-O-I) and OR-AND-INVERT (O-A-I ) Gates: CMOS circuits can perform two levels of logic with just a single “level” of transistors. For example, the circuit in below Figure 10 is a two-wide, two-input CMOS AND-OR-INVERT (AOI) gate o/p Z= (AB+CD)’. The function table for this circuit ...

... CMOS AND-OR-INVERT(A-O-I) and OR-AND-INVERT (O-A-I ) Gates: CMOS circuits can perform two levels of logic with just a single “level” of transistors. For example, the circuit in below Figure 10 is a two-wide, two-input CMOS AND-OR-INVERT (AOI) gate o/p Z= (AB+CD)’. The function table for this circuit ...

Armature Core

... It means that coil span is 180o electrical degrees. In this case, the coil sides lie under opposite poles, hence the induced e.m.f.s in them are additive. Therefore, maximum e.m.f. is induced in the two coil sides. Fractional Pitched: If the coil span is less than the pole pitch, then the winding is ...

... It means that coil span is 180o electrical degrees. In this case, the coil sides lie under opposite poles, hence the induced e.m.f.s in them are additive. Therefore, maximum e.m.f. is induced in the two coil sides. Fractional Pitched: If the coil span is less than the pole pitch, then the winding is ...

to get the file - Caltech Optical Observatories

... Persistence is higher if the stimulus is delivered as a flash at exposure start instead of a constant flux integrated to the same level (Fig. 4). Traps are exposed to charge for longer on average and thus capture more charge. Optical and electrically induced changes in detector bias produce simi ...

... Persistence is higher if the stimulus is delivered as a flash at exposure start instead of a constant flux integrated to the same level (Fig. 4). Traps are exposed to charge for longer on average and thus capture more charge. Optical and electrically induced changes in detector bias produce simi ...

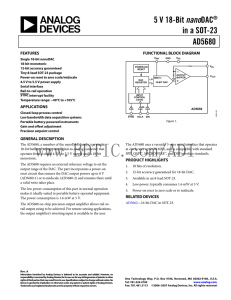

AD5680 数据手册DataSheet 下载

... 12-bit accuracy guaranteed Tiny 8-lead SOT-23 package Power-on reset to zero scale/midscale 4.5 V to 5.5 V power supply Serial interface Rail-to-rail operation SYNC interrupt facility Temperature range: −40°C to +105°C ...

... 12-bit accuracy guaranteed Tiny 8-lead SOT-23 package Power-on reset to zero scale/midscale 4.5 V to 5.5 V power supply Serial interface Rail-to-rail operation SYNC interrupt facility Temperature range: −40°C to +105°C ...