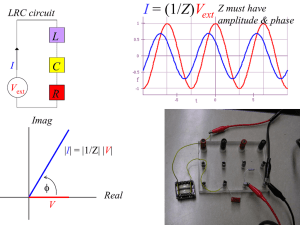

V - Physics | Oregon State University

... • Draw phasor diagrams of Vext, I, 1/Z (or Z) • Express 1/Z (or Z) in terms of R, L, C or w0, b You should be able to discuss: • The amplitude of the response and resonance • The phase of the response • The nature of the behavior at all frequencies • The transfer of the series LCR circuit analysis t ...

... • Draw phasor diagrams of Vext, I, 1/Z (or Z) • Express 1/Z (or Z) in terms of R, L, C or w0, b You should be able to discuss: • The amplitude of the response and resonance • The phase of the response • The nature of the behavior at all frequencies • The transfer of the series LCR circuit analysis t ...

MAX5080 Evaluation Kit Evaluates: MAX5080–MAX5083 General Description Features

... converter and automatically switches to PFM mode at light loads to improve efficiency. The MAX5080 features a SYNC input to provide external frequency synchronization for noise-sensitive applications. The EV kit features PC board pads to evaluate the SYNC and ON/OFF features of the MAX5080. The MAX5 ...

... converter and automatically switches to PFM mode at light loads to improve efficiency. The MAX5080 features a SYNC input to provide external frequency synchronization for noise-sensitive applications. The EV kit features PC board pads to evaluate the SYNC and ON/OFF features of the MAX5080. The MAX5 ...

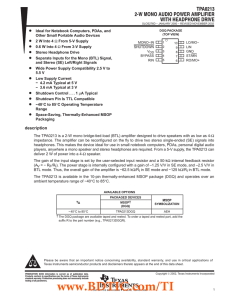

TPA0213 数据资料 dataSheet 下载

... consideration for this capacitor is the leakage path from the input source through the input network (Ci) and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this ...

... consideration for this capacitor is the leakage path from the input source through the input network (Ci) and the feedback network to the load. This leakage current creates a dc offset voltage at the input to the amplifier that reduces useful headroom, especially in high gain applications. For this ...

AN4076

... The non-inverting configuration shown in Figure 3 is usually used in STEVAL boards. As can be seen, as the signal on the shunt resistor can be both positive and negative, while the MCU can only read positive voltage, an offset is added (R2, R3) so that the output of the op amp equals about half of t ...

... The non-inverting configuration shown in Figure 3 is usually used in STEVAL boards. As can be seen, as the signal on the shunt resistor can be both positive and negative, while the MCU can only read positive voltage, an offset is added (R2, R3) so that the output of the op amp equals about half of t ...

... This thesis presents the development and assessment of imaging techniques in the millimeterwave (mmW) and terahertz frequency bands. In the first part of the thesis, the development of a 94 GHz passive screener based on a total-power radiometer (TPR) with mechanical beamscanning is presented. Severa ...

OPA830-EP Low-Power, Single-Supply, Wideband Operational

... common-emitter outputs provides an output swing to within 25mV of either supply while driving 150Ω. High output drive current (±80mA) and low differential gain and phase errors also make them ideal for singlesupply consumer video products. ...

... common-emitter outputs provides an output swing to within 25mV of either supply while driving 150Ω. High output drive current (±80mA) and low differential gain and phase errors also make them ideal for singlesupply consumer video products. ...

LOW NOISE, HIGH SLEW RATE, UNITY GAIN STABLE VOLTAGE FEEDBACK AMPLIFIER THS4271-EP FEATURES

... 0.1-dB gain flatness frequency response ...

... 0.1-dB gain flatness frequency response ...

ADS5120 数据资料 dataSheet 下载

... digital I/O supply (DRVDD) can be set to either +1.8V or +3.3V. The ADC core of each channel consists of 10 pipeline stages. Each of the 10 stages produces one digital bit per stage. Both the rising and the falling clock edges are utilized to propagate the sample through the pipeline every half cloc ...

... digital I/O supply (DRVDD) can be set to either +1.8V or +3.3V. The ADC core of each channel consists of 10 pipeline stages. Each of the 10 stages produces one digital bit per stage. Both the rising and the falling clock edges are utilized to propagate the sample through the pipeline every half cloc ...

DAC8811 - Texas Instruments

... Added Input high voltage for VDD = 2.7 V and 2.5 V in the Electrical Characteristics ........................................................... 6 ...

... Added Input high voltage for VDD = 2.7 V and 2.5 V in the Electrical Characteristics ........................................................... 6 ...