A Novel Square Root Domain Lossless Integrator and Its Application

... multiplier/divider circuit blocks. In this work, a new square root domain lossless integrator is designed by using state space synthesis method. The proposed lossless integrator consists of only a geometric mean circuit. Lossless integrator circuits are useful for designing highorder filters and biq ...

... multiplier/divider circuit blocks. In this work, a new square root domain lossless integrator is designed by using state space synthesis method. The proposed lossless integrator consists of only a geometric mean circuit. Lossless integrator circuits are useful for designing highorder filters and biq ...

LXMG1618A-12-4x - uri=media.digikey

... them open or grounding them is all that is needed to set the output current, they can also be actively set. Using an open collector or open drain logic signal will allow you to reduce the lamp current for situations where greater dim range is required, as an example in nighttime situations. In conju ...

... them open or grounding them is all that is needed to set the output current, they can also be actively set. Using an open collector or open drain logic signal will allow you to reduce the lamp current for situations where greater dim range is required, as an example in nighttime situations. In conju ...

低噪声、低静态电流、高精度运算放大器 ™ 系列 e-trim OPA376-Q1

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

... This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete devi ...

Difet OPA2111 Dual Low Noise Precision OPERATIONAL AMPLIFIER

... damage can cause subtle changes in amplifier input characteristics without necessarily destroying the device. In precision operational amplifiers (both bipolar and FET types), this may cause a noticeable degradation of offset voltage and drift. ...

... damage can cause subtle changes in amplifier input characteristics without necessarily destroying the device. In precision operational amplifiers (both bipolar and FET types), this may cause a noticeable degradation of offset voltage and drift. ...

Aalborg Universitet

... frequency circulating current between the parallel connected VSCs. This unwanted current introduces additional losses and increases the stress on both the semiconductor devices and the filter components. Therefore, the circulating current should be suppressed by introducing additional impedance in t ...

... frequency circulating current between the parallel connected VSCs. This unwanted current introduces additional losses and increases the stress on both the semiconductor devices and the filter components. Therefore, the circulating current should be suppressed by introducing additional impedance in t ...

FEATURES DESCRIPTION D

... path. This amplifier is zero-corrected every 100µs using a proprietary technique. Upon power-up, the amplifier requires approximately 400µs to achieve specified VOS accuracy, which includes one full auto-zero cycle of approximately 100µs and the start-up time for the bias circuitry. Prior to this ti ...

... path. This amplifier is zero-corrected every 100µs using a proprietary technique. Upon power-up, the amplifier requires approximately 400µs to achieve specified VOS accuracy, which includes one full auto-zero cycle of approximately 100µs and the start-up time for the bias circuitry. Prior to this ti ...

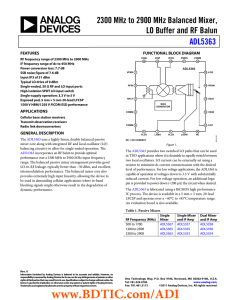

2300 MHz to 2900 MHz Balanced Mixer, ADL5363

... Transmit observation receivers Radio link downconverters ...

... Transmit observation receivers Radio link downconverters ...

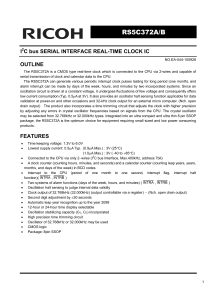

Ricoh RS5C372A - on Natisbad.org!

... alarm interrupt can be made by days of the week, hours, and minutes by two incorporated systems. Since an oscillation circuit is driven at a constant voltage, it undergoes fluctuations of few voltage and consequently offers low current consumption (Typ. 0.5μA at 3V). It also provides an oscillator h ...

... alarm interrupt can be made by days of the week, hours, and minutes by two incorporated systems. Since an oscillation circuit is driven at a constant voltage, it undergoes fluctuations of few voltage and consequently offers low current consumption (Typ. 0.5μA at 3V). It also provides an oscillator h ...

SN65MLVD040 数据资料 dataSheet 下载

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

... receivers implement a failsafe by using an offset threshold. The xFSEN pins is used to select the Type-1 and Type-2 receiver for each of the channels. In addition, the driver rise and fall times are between 1 ns and 2 ns, complying with the M-LVDS standard to provide operation at 250 Mbps while also ...

TPS54350 数据资料 dataSheet 下载

... operating as an input, the SYNC pin is a falling-edge triggered signal (see Figures 3, 4, and 19). When operating as an output, the signal’s falling edge is approximately 180° out of phase with the rising edge of the PH pins. Thus, two TPS54350 devices operating in a system can share an input capaci ...

... operating as an input, the SYNC pin is a falling-edge triggered signal (see Figures 3, 4, and 19). When operating as an output, the signal’s falling edge is approximately 180° out of phase with the rising edge of the PH pins. Thus, two TPS54350 devices operating in a system can share an input capaci ...

ECE 162-0813

... speed design. Final Adder: The final adder is the largest component in the S&A, which sums the outputs of four select units. The carry-save array [2] and the new carry-select adder presented in Section III-A are used for high performance. As mentioned before, the input data is in two‟s complement fo ...

... speed design. Final Adder: The final adder is the largest component in the S&A, which sums the outputs of four select units. The carry-save array [2] and the new carry-select adder presented in Section III-A are used for high performance. As mentioned before, the input data is in two‟s complement fo ...

2.7 V to 5.25 V, Micropower, 2-Channel, AD7887 Data Sheet

... Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7887 and also frames the serial data transfer. When the AD7887 operates in its default mode, the CS pin also acts as the shutdown pin such that with the CS pin high, the AD7887 is in its pow ...

... Chip Select. Active low logic input. This input provides the dual function of initiating conversions on the AD7887 and also frames the serial data transfer. When the AD7887 operates in its default mode, the CS pin also acts as the shutdown pin such that with the CS pin high, the AD7887 is in its pow ...

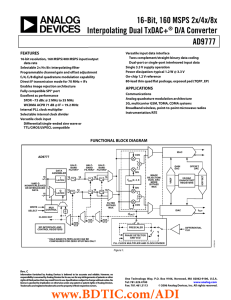

AD9777 数据手册DataSheet 下载

... modulator to complete the image rejection upconversion process. Another digital modulation mode (that is, the direct IF mode) allows the original baseband signal representation to be frequency translated such that pairs of images fall at multiples of one-half the DAC update rate. The AD977x family i ...

... modulator to complete the image rejection upconversion process. Another digital modulation mode (that is, the direct IF mode) allows the original baseband signal representation to be frequency translated such that pairs of images fall at multiples of one-half the DAC update rate. The AD977x family i ...

Optimized Resonant Harmonic Filters

... where Q is the load reactive power per-phase and dk is the coefficient of the reactive power allocation to particular branches of the filter. The opinions with respect to the reactive power allocation to particular branches are divided. According to Ref. [1], this allocation is irrelevant for the fi ...

... where Q is the load reactive power per-phase and dk is the coefficient of the reactive power allocation to particular branches of the filter. The opinions with respect to the reactive power allocation to particular branches are divided. According to Ref. [1], this allocation is irrelevant for the fi ...

THS3201-EP

... a wide supply range of ±3.3 V to ±7.5 V for today's high-performance applications. The wide supply range, combined with low distortion and high slew rate, makes the THS3201 ideally suited for arbitrary waveform driver applications. The distortion performance also enables driving high-resolution and ...

... a wide supply range of ±3.3 V to ±7.5 V for today's high-performance applications. The wide supply range, combined with low distortion and high slew rate, makes the THS3201 ideally suited for arbitrary waveform driver applications. The distortion performance also enables driving high-resolution and ...

BDTIC

... Please note that ICE2PCXX has enhance dynamic block which is active when Vout exceed ±5% of regulated level. The enchanc dynamic block should be designed to work only during load or line change. During steady state with constant load, the enhance dynamic block should not be triggered, otherwise THD ...

... Please note that ICE2PCXX has enhance dynamic block which is active when Vout exceed ±5% of regulated level. The enchanc dynamic block should be designed to work only during load or line change. During steady state with constant load, the enhance dynamic block should not be triggered, otherwise THD ...

Physics 2511 Laboratory Manual

... Safety in the laboratory is very important. The experiments performed in the laboratory are designed to be as safe as possible, but caution is always advised concerning the use of the equipment. When you arrive at the start of each class meeting, it is very important that you do not touch or turn on ...

... Safety in the laboratory is very important. The experiments performed in the laboratory are designed to be as safe as possible, but caution is always advised concerning the use of the equipment. When you arrive at the start of each class meeting, it is very important that you do not touch or turn on ...

Multiplying DACs Flexible Building Blocks

... Analog Devices has a comprehensive family of 8-/10-/12-/14-/16-bit multiplying digital-to-analog converters. As a result of manufacture on a CMOS submicron process, these DACs offer excellent 4-quadrant multiplication characteristics. By offering flexibility and simplicity, multiplying DAC products ...

... Analog Devices has a comprehensive family of 8-/10-/12-/14-/16-bit multiplying digital-to-analog converters. As a result of manufacture on a CMOS submicron process, these DACs offer excellent 4-quadrant multiplication characteristics. By offering flexibility and simplicity, multiplying DAC products ...

UNIT-3 (1) - WordPress.com

... To change the bistable over from one state to the other, the bistable circuit requires a suitable trigger pulse and to go through a full cycle, two triggering pulses, one for each stage are required. Its more common name or term of “flip-flop” relates to the actual operation of the device, as it “f ...

... To change the bistable over from one state to the other, the bistable circuit requires a suitable trigger pulse and to go through a full cycle, two triggering pulses, one for each stage are required. Its more common name or term of “flip-flop” relates to the actual operation of the device, as it “f ...

Chpt. 7 Introduction to digital system clocking

... Historically computers built in the past were large in size and they filled up several electronic cabinets occupying entire floors of a large air-conditioned room. They were built from discrete components or used a few LSI chips in the later models. Those systems were clocked at frequencies of about ...

... Historically computers built in the past were large in size and they filled up several electronic cabinets occupying entire floors of a large air-conditioned room. They were built from discrete components or used a few LSI chips in the later models. Those systems were clocked at frequencies of about ...

Aalborg Universitet Stationary Frame Current Control Evaluations for Three-Phase Grid-Connected

... However, by using only grid-current control, the system is prone to resonances if it is not properly damped, and the current distortion would be amplified significantly under highly distorted grid conditions. In this paper, a synchronous reference frame equivalent proportional-integral (SRF-EPI) con ...

... However, by using only grid-current control, the system is prone to resonances if it is not properly damped, and the current distortion would be amplified significantly under highly distorted grid conditions. In this paper, a synchronous reference frame equivalent proportional-integral (SRF-EPI) con ...

MAX5080 Evaluation Kit Evaluates: MAX5080–MAX5083 General Description Features

... converter IC (U1) to implement a step-down DC-DC converter circuit. The MAX5080 EV kit operates over a wide 4.5V to 40V input voltage range and is configured to provide 3.3V at up to 1A of output current. The MAX5080 step-down converter IC features an internal high-side low RDS(ON) MOSFET to achieve ...

... converter IC (U1) to implement a step-down DC-DC converter circuit. The MAX5080 EV kit operates over a wide 4.5V to 40V input voltage range and is configured to provide 3.3V at up to 1A of output current. The MAX5080 step-down converter IC features an internal high-side low RDS(ON) MOSFET to achieve ...

AN-835: Understanding High Speed ADC Testing and Evaluation

... rejection of 60 dB, meaning that signals that fall into the stop band will be rejected by 60 dB. If, for example, a signal source has a harmonic that is 25 dB below the fundamental, the effective level of the harmonic is −85 dBc after a Q70T filter. For many high performance ADCs, this is not suffic ...

... rejection of 60 dB, meaning that signals that fall into the stop band will be rejected by 60 dB. If, for example, a signal source has a harmonic that is 25 dB below the fundamental, the effective level of the harmonic is −85 dBc after a Q70T filter. For many high performance ADCs, this is not suffic ...

UCC28500 数据资料 dataSheet 下载

... current-mode control. The dc-to-dc converter uses peak current-mode control to perform the step-down power conversion. The PFC stage is leading-edge modulated while the second stage is trailing-edge synchronized to allow for minimum overlap between the boost and PWM switches. This reduces ripple cur ...

... current-mode control. The dc-to-dc converter uses peak current-mode control to perform the step-down power conversion. The PFC stage is leading-edge modulated while the second stage is trailing-edge synchronized to allow for minimum overlap between the boost and PWM switches. This reduces ripple cur ...