POWER NOTES

... the rise and fall time of the semiconductor devices used in the inverter section of VFDs. The present tendency among drive manufacturers is to use InsulatedGate-Bipolar-Transistor (IGBTs) devices which have a much lower power loss and higher switching speed than their predecessors Bipolar Junction T ...

... the rise and fall time of the semiconductor devices used in the inverter section of VFDs. The present tendency among drive manufacturers is to use InsulatedGate-Bipolar-Transistor (IGBTs) devices which have a much lower power loss and higher switching speed than their predecessors Bipolar Junction T ...

FM_Lecture3 - WordPress.com

... Memoryless Non-linear operation: The non-linear device is assumed to be memory-less means that there is no energy storage. The memoryless non-linear device is represented by input and output relation ...

... Memoryless Non-linear operation: The non-linear device is assumed to be memory-less means that there is no energy storage. The memoryless non-linear device is represented by input and output relation ...

EE202 Powerpoint Slides

... critical frequency but rejects those below. – Bandpass filter - Passes only frequencies in a narrow range between upper and lower cutoff frequencies. – Band-reject filter - Rejects or stops frequencies in a narrow range but passes others. ...

... critical frequency but rejects those below. – Bandpass filter - Passes only frequencies in a narrow range between upper and lower cutoff frequencies. – Band-reject filter - Rejects or stops frequencies in a narrow range but passes others. ...

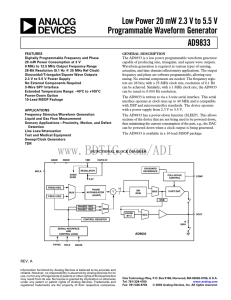

a Low Power 20 mW 2.3 V to 5.5 V AD9833

... synchronization and chip enable. Data can be transferred into the device only when FSYNC is low. To start the serial data transfer, FSYNC should be taken low, observing the minimum FSYNC to SCLK falling edge setup time, t7. After FSYNC goes low, serial data will be shifted into the device’s input sh ...

... synchronization and chip enable. Data can be transferred into the device only when FSYNC is low. To start the serial data transfer, FSYNC should be taken low, observing the minimum FSYNC to SCLK falling edge setup time, t7. After FSYNC goes low, serial data will be shifted into the device’s input sh ...

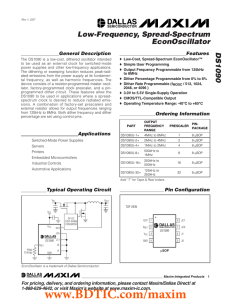

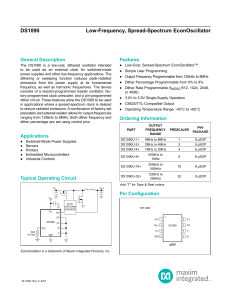

DS1090 Low-Frequency, Spread-Spectrum EconOscillator General Description

... The DS1090 is a center-dithered, spread-spectrum silicon oscillator for use as an external clock in reducedEMI applications. With a combination of factoryprogrammed prescalers and a user-selected external resistor, output frequencies from 125kHz to 8MHz can be achieved. The output center frequency c ...

... The DS1090 is a center-dithered, spread-spectrum silicon oscillator for use as an external clock in reducedEMI applications. With a combination of factoryprogrammed prescalers and a user-selected external resistor, output frequencies from 125kHz to 8MHz can be achieved. The output center frequency c ...

1. Pre-Lab Introduction

... 1. Construct the circuit shown in Figure 7-1. Use ± 15 V supplies for the op-amp and a load resistance of 2.4 k-Ohms. 2. Verify the operation of the circuit using a 500 mV peak, 50 Hz sinewave as the input signal. Be sure to design the "gain" such that the output does not saturate. 3. Repeat step 2 ...

... 1. Construct the circuit shown in Figure 7-1. Use ± 15 V supplies for the op-amp and a load resistance of 2.4 k-Ohms. 2. Verify the operation of the circuit using a 500 mV peak, 50 Hz sinewave as the input signal. Be sure to design the "gain" such that the output does not saturate. 3. Repeat step 2 ...

View File - UET Taxila

... Signal spreading is done before transmission by using a spreading sequence. The same sequence is used at the receiver to retrieve the signal Spread Spectrum is most effective against interference (intentional or non-intentional) with fixed energy. Main commercial applications in wireless and GPS. Tw ...

... Signal spreading is done before transmission by using a spreading sequence. The same sequence is used at the receiver to retrieve the signal Spread Spectrum is most effective against interference (intentional or non-intentional) with fixed energy. Main commercial applications in wireless and GPS. Tw ...

74LS74 - eeshop home page

... General Description This device contains two independent positive-edge-triggered D-type flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly rela ...

... General Description This device contains two independent positive-edge-triggered D-type flip-flops with complementary outputs. The information on the D input is accepted by the flip-flops on the positive going edge of the clock pulse. The triggering occurs at a voltage level and is not directly rela ...

W. Rieutort-Louis, L. Huang, Y. Hu, J. Sanz-Robinson, S. Wagner, J.C. Sturm, N. Verma, "A figure of merit for oscillator-based thin-film circuits on plastic for high-performance signaling, energy harvesting and driving of actuation circuits, Device Research Conference (DRC), 10.1109/DRC.2012.6256980 pp. 117-118 University Park, PA JUN (2012).

... oscillators as a function of CLOAD. Measured parameters are similar on plastic and glass substrates, and experimental results were validated with a developed Level 61 a-Si TFT SPICE model. Power consumption scales inversely with stage load resistances (Fig. 7), dominated by on-state static current. ...

... oscillators as a function of CLOAD. Measured parameters are similar on plastic and glass substrates, and experimental results were validated with a developed Level 61 a-Si TFT SPICE model. Power consumption scales inversely with stage load resistances (Fig. 7), dominated by on-state static current. ...

Lecture #2 Oscilloscopes 2 Comparators

... • Calculate the values of RL for the 4 angles given in Step 18. • Review the oscilloscope material referenced on the course web site. • (optional) Review Lissajous diagrams on the web. ...

... • Calculate the values of RL for the 4 angles given in Step 18. • Review the oscilloscope material referenced on the course web site. • (optional) Review Lissajous diagrams on the web. ...

AD8072

... The high bandwidth of 100 MHz, 500 V/µs of slew rate, along with settling to 0.1% in 25 ns, make the AD8072 and AD8073 useful in many general purpose, high speed applications where a single 5 V or dual power supplies up to ± 6 V are needed. The AD8072 is available in 8-lead plastic DIP, SOIC, and µS ...

... The high bandwidth of 100 MHz, 500 V/µs of slew rate, along with settling to 0.1% in 25 ns, make the AD8072 and AD8073 useful in many general purpose, high speed applications where a single 5 V or dual power supplies up to ± 6 V are needed. The AD8072 is available in 8-lead plastic DIP, SOIC, and µS ...

Experiment 2 - Portal UniMAP

... Output offset voltage is the dc voltage that appears at the output when both inputs are zero volts. The output offset voltage of an operational-amplifier is caused by input offset voltage, due to slightly mismatched transistors in the differential-amplifier input stage, and differences in input bias ...

... Output offset voltage is the dc voltage that appears at the output when both inputs are zero volts. The output offset voltage of an operational-amplifier is caused by input offset voltage, due to slightly mismatched transistors in the differential-amplifier input stage, and differences in input bias ...

Lab 2: Op-Amp Parameters

... Output offset voltage is the dc voltage that appears at the output when both inputs are zero volts. The output offset voltage of an operational-amplifier is caused by input offset voltage, due to slightly mismatched transistors in the differential-amplifier input stage, and differences in input bias ...

... Output offset voltage is the dc voltage that appears at the output when both inputs are zero volts. The output offset voltage of an operational-amplifier is caused by input offset voltage, due to slightly mismatched transistors in the differential-amplifier input stage, and differences in input bias ...

IOSR Journal of Electrical and Electronics Engineering (IOSR-JEEE) e-ISSN: 2278-1676,p-ISSN: 2320-3331,

... P. Rodr´ıguez, J. Pou, J. Bergas, I. Candela, R. Burgos, and D. Boroyevich, “Double synchronous reference frame PLL for power converters control,” in Proc. IEEE PESC, 2005, pp. 1415–1421. P. Rodriguez, J. Pou, J. Bergas, I. Candela, R. Burgos, and D. Boroyevich, “Decoupled double synchronous referen ...

... P. Rodr´ıguez, J. Pou, J. Bergas, I. Candela, R. Burgos, and D. Boroyevich, “Double synchronous reference frame PLL for power converters control,” in Proc. IEEE PESC, 2005, pp. 1415–1421. P. Rodriguez, J. Pou, J. Bergas, I. Candela, R. Burgos, and D. Boroyevich, “Decoupled double synchronous referen ...

Fault Classification in Phase-Locked Loops Using Back Propagation

... The basic BP algorithm adjusts the weights in the steepest descent direction. This is the direction in which the performance function decreases most rapidly. Although the function decreases most rapidly along the negative of the gradient, this does not necessarily produce the fastest convergence. In ...

... The basic BP algorithm adjusts the weights in the steepest descent direction. This is the direction in which the performance function decreases most rapidly. Although the function decreases most rapidly along the negative of the gradient, this does not necessarily produce the fastest convergence. In ...