Respiratory Inductance Plethysmography An Introduction

... field normal to the orientation of the loop (Faraday’s Law) and that a change in the area enclosed by the loop creates an opposing current within the loop directly proportional to the change in the area (Lenz’s Law). An elastic belt into which a zigzagging (coiled) wire is sewn (to allow for expansi ...

... field normal to the orientation of the loop (Faraday’s Law) and that a change in the area enclosed by the loop creates an opposing current within the loop directly proportional to the change in the area (Lenz’s Law). An elastic belt into which a zigzagging (coiled) wire is sewn (to allow for expansi ...

AD828

... Superior load handling capability (50 mA min/amp), high bandwidth, wide supply voltage range, and excellent crosstalk rejection makes the AD828 an ideal choice for even the most demanding high speed transmission applications. The schematic below shows a pair of AD828s configured to drive 100 feet of ...

... Superior load handling capability (50 mA min/amp), high bandwidth, wide supply voltage range, and excellent crosstalk rejection makes the AD828 an ideal choice for even the most demanding high speed transmission applications. The schematic below shows a pair of AD828s configured to drive 100 feet of ...

0.18µm PHASE / FREQUENCY DETECTOR AND CHARGE PUMP

... broadcasting for hand held devices. The schematic designs of the circuits are implemented using TSMC 0.18µm CMOS technology. Two phase/frequency detector are proposed in this paper to show the effect of the dead zone on the performance of the frequency synthesizer. The main propose of these two PFD ...

... broadcasting for hand held devices. The schematic designs of the circuits are implemented using TSMC 0.18µm CMOS technology. Two phase/frequency detector are proposed in this paper to show the effect of the dead zone on the performance of the frequency synthesizer. The main propose of these two PFD ...

Digital Electronics I: Logic, Flip

... requires more than a single bit, either more wires can be used to convey data (parallel digital data), or a sequence of bits can be sent over time as HIGH‟s and LOW‟s moving along a single wire (serial digital data). Analog information can be translated into digital form by a device called an Analog ...

... requires more than a single bit, either more wires can be used to convey data (parallel digital data), or a sequence of bits can be sent over time as HIGH‟s and LOW‟s moving along a single wire (serial digital data). Analog information can be translated into digital form by a device called an Analog ...

Kirchoffs Circuit Law Example No1

... to a halt. An even more dangerous type of virus is one capable of transmitting itself across networks and bypassing security systems. Since 1987, when a virus infected ARPANET, a large network used by the Defense Department and many universities, many antivirus programs have become available. These ...

... to a halt. An even more dangerous type of virus is one capable of transmitting itself across networks and bypassing security systems. Since 1987, when a virus infected ARPANET, a large network used by the Defense Department and many universities, many antivirus programs have become available. These ...

MAX3892 +3.3V, 2.5Gbps/2.7Gbps, SDH/SONET 4:1 Serializer with Clock Synthesis General Description

... DWDM and SONET/SDH applications. A 4 ✕ 4-bit FIFO allows for any static delay between the parallel output clock and parallel input clock. Delay variation up to a unit interval (UI) is allowed after reset. A fully integrated phase-locked loop (PLL) synthesizes an internal 2.5GHz serial clock from a 6 ...

... DWDM and SONET/SDH applications. A 4 ✕ 4-bit FIFO allows for any static delay between the parallel output clock and parallel input clock. Delay variation up to a unit interval (UI) is allowed after reset. A fully integrated phase-locked loop (PLL) synthesizes an internal 2.5GHz serial clock from a 6 ...

MAX9248/MAX9250 27-Bit, 2.5MHz to 42MHz DC-Balanced LVDS Deserializers General Description

... The MAX9248/MAX9250 digital video serial-to-parallel converters deserialize a total of 27 bits during data and control phases. In the data phase, the LVDS serial input is converted to 18 bits of parallel video data and in the control phase, the input is converted to 9 bits of parallel control data. ...

... The MAX9248/MAX9250 digital video serial-to-parallel converters deserialize a total of 27 bits during data and control phases. In the data phase, the LVDS serial input is converted to 18 bits of parallel video data and in the control phase, the input is converted to 9 bits of parallel control data. ...

ADS5232 数据资料 dataSheet 下载

... For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI ...

... For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI ...

ADS5237 数据资料 dataSheet 下载

... For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI ...

... For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the TI ...

PDF

... Fig. 7(a) shows the input to the system when line to ground fault occurs. The system was initially in balanced condition (having amplitude 1.5V). Line to ground fault occurs at time, t = 0.4sec.At this instant the phase voltage of 2 of the phases increases and remains at an amplitude of 2.4V. The sy ...

... Fig. 7(a) shows the input to the system when line to ground fault occurs. The system was initially in balanced condition (having amplitude 1.5V). Line to ground fault occurs at time, t = 0.4sec.At this instant the phase voltage of 2 of the phases increases and remains at an amplitude of 2.4V. The sy ...

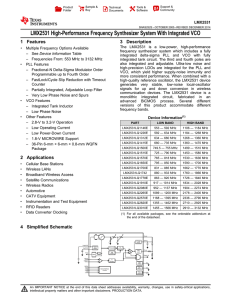

LMX2531 - Texas Instruments

... frequency as: LNPLL_flicker(f) = LPLL_flicker(10 kHz) – 10 × log (10 kHz / f) + 20 × log ( Fout / 1 GHz ). Flicker noise can dominate at low offsets from the carrier and has a 10 dB/decade slope and improves with higher charge pump currents and at higher offset frequencies . To accurately measure LP ...

... frequency as: LNPLL_flicker(f) = LPLL_flicker(10 kHz) – 10 × log (10 kHz / f) + 20 × log ( Fout / 1 GHz ). Flicker noise can dominate at low offsets from the carrier and has a 10 dB/decade slope and improves with higher charge pump currents and at higher offset frequencies . To accurately measure LP ...

AD7740

... The crystal/resonator is tied between this pin and CLKIN. In the case of an external clock driving CLKIN, an inverted clock signal appears on this pin and can be used to drive other circuitry provided it is buffered first. The master clock for the device may be in the form of a crystal/resonator tied ...

... The crystal/resonator is tied between this pin and CLKIN. In the case of an external clock driving CLKIN, an inverted clock signal appears on this pin and can be used to drive other circuitry provided it is buffered first. The master clock for the device may be in the form of a crystal/resonator tied ...

Physics 160 Lecture 15

... A real op amp will have some input bias current (especially for BJT input) input). The current flowing through R1 and R2 will shift the voltage at the inverting input. We should add a resistor to the g input p to compensate: p non-inverting ...

... A real op amp will have some input bias current (especially for BJT input) input). The current flowing through R1 and R2 will shift the voltage at the inverting input. We should add a resistor to the g input p to compensate: p non-inverting ...

PLL1707-Q1 数据资料 dataSheet 下载

... The PLL1707 is a low-cost phase-locked loop (PLL) multiclock generator. The PLL1707 can generate four system clocks from a 27-MHz reference input frequency. The clock outputs of the PLL1707 can be controlled by sampling frequency-control pins. The device gives customers both cost and space savings b ...

... The PLL1707 is a low-cost phase-locked loop (PLL) multiclock generator. The PLL1707 can generate four system clocks from a 27-MHz reference input frequency. The clock outputs of the PLL1707 can be controlled by sampling frequency-control pins. The device gives customers both cost and space savings b ...