AN3971

... Each Z affects power transfer between the input source and output load and for each Z an input voltage (Vin) and current (Iin) can be measured. The purpose of the MPPT algorithm is to guarantee Z = ZM, assuming ZM as the impedance value for which the power extracted from the supply source (Pin = Vin ...

... Each Z affects power transfer between the input source and output load and for each Z an input voltage (Vin) and current (Iin) can be measured. The purpose of the MPPT algorithm is to guarantee Z = ZM, assuming ZM as the impedance value for which the power extracted from the supply source (Pin = Vin ...

BDTIC www.BDTIC.com/infineon BGR420

... • Noise figure NF = 1.5 dB at 0.4 GHz • Gain S21 = 26 dB at 0.4 GHz • On chip bias circuitry, 13 mA bias current at VCC = 3.6 V; VBB = 2.8 V • SIEGET ® 25 GHz fT-Line • Pb-free (RoHS compliant) package ...

... • Noise figure NF = 1.5 dB at 0.4 GHz • Gain S21 = 26 dB at 0.4 GHz • On chip bias circuitry, 13 mA bias current at VCC = 3.6 V; VBB = 2.8 V • SIEGET ® 25 GHz fT-Line • Pb-free (RoHS compliant) package ...

Lab 1 - Diode Circuits

... □ Construct the circuit in Figure 1-10 using 1N4148s or 1N400xs and record the output voltage. Vary Figure 1-10 – Series-connected diodes the supply voltage ±2V and record how much the 1 kΩ output voltage changes. Clearly a zener would be more economical for larger voltages. In any case it is import ...

... □ Construct the circuit in Figure 1-10 using 1N4148s or 1N400xs and record the output voltage. Vary Figure 1-10 – Series-connected diodes the supply voltage ±2V and record how much the 1 kΩ output voltage changes. Clearly a zener would be more economical for larger voltages. In any case it is import ...

R09 SET-1 Code No: R09221902

... ANALOG AND DIGITAL IC APPLICATIONS (ELECTRONICS & COMPUTER ENGINEERING) Time: 3 hours Max. Marks: 75 Answer any five questions All questions carry equal marks --1.a) What are the Four Differential Amplifier Configurations? Compare and Contrast these configurations with Circuit Diagrams. b) For an Op ...

... ANALOG AND DIGITAL IC APPLICATIONS (ELECTRONICS & COMPUTER ENGINEERING) Time: 3 hours Max. Marks: 75 Answer any five questions All questions carry equal marks --1.a) What are the Four Differential Amplifier Configurations? Compare and Contrast these configurations with Circuit Diagrams. b) For an Op ...

Chapter 6: Parallel Circuits

... • When two equal sources are connected in parallel – Each source supplies half the required current ...

... • When two equal sources are connected in parallel – Each source supplies half the required current ...

Chapter 6: Parallel Circuits

... • When two equal sources are connected in parallel – Each source supplies half the required current ...

... • When two equal sources are connected in parallel – Each source supplies half the required current ...

Final Input Buffer Design

... wanted a design that would be compliant if possible. This required us to find a design that would allow conversion from 500mV to 3.3V in a single stage, as extra stages will increase both active power and leakage, which go against our design goals. We later added two PMOS transistors into the pull u ...

... wanted a design that would be compliant if possible. This required us to find a design that would allow conversion from 500mV to 3.3V in a single stage, as extra stages will increase both active power and leakage, which go against our design goals. We later added two PMOS transistors into the pull u ...

ADXRS624 英文数据手册DataSheet 下载

... The ADXRS624 includes a self-test feature that actuates each of the sensing structures and associated electronics as if subjected to angular rate. The self-test feature is activated by standard logic high levels applied to Input ST1 (5F, 5G), Input ST2 (4F, 4G), or both. ST1 causes the voltage at RA ...

... The ADXRS624 includes a self-test feature that actuates each of the sensing structures and associated electronics as if subjected to angular rate. The self-test feature is activated by standard logic high levels applied to Input ST1 (5F, 5G), Input ST2 (4F, 4G), or both. ST1 causes the voltage at RA ...

OPA353 OPA2353 OPA4353 High-Speed, Single-Supply, Rail-to-Rail

... OPA353 series op amps are fully specified from +2.7V to +5.5V. However, supply voltage may range from +2.5V to +5.5V. Parameters are guaranteed over the specified supply range—a unique feature of the OPA353 series. In addition, many specifications apply from –40°C to +85°C. Most behavior remains vir ...

... OPA353 series op amps are fully specified from +2.7V to +5.5V. However, supply voltage may range from +2.5V to +5.5V. Parameters are guaranteed over the specified supply range—a unique feature of the OPA353 series. In addition, many specifications apply from –40°C to +85°C. Most behavior remains vir ...

TOSHIBA TC55V328AJ-15/17/20 SILICON GATE CMOS

... The TC55V328AJ is a 262,144 bits high speed static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 3.3-volt supply. Toshiba’s CMOS technology and advanced circuit form provide low voltage operation and high speed feature. The TC55V328AJ has ...

... The TC55V328AJ is a 262,144 bits high speed static random access memory organized as 32,768 words by 8 bits using CMOS technology, and operated from a single 3.3-volt supply. Toshiba’s CMOS technology and advanced circuit form provide low voltage operation and high speed feature. The TC55V328AJ has ...

DC2132A - Linear Technology

... (potentiometer). That voltage directly sets the output voltage of the LT3081. The maximum output voltage can be set to three settings: 24V, 15V and 5.5V with the shunt position on JP1. The setting should be changed according to the choice of input voltage. A 36V, 24V, or 12V AC/DC converter can be u ...

... (potentiometer). That voltage directly sets the output voltage of the LT3081. The maximum output voltage can be set to three settings: 24V, 15V and 5.5V with the shunt position on JP1. The setting should be changed according to the choice of input voltage. A 36V, 24V, or 12V AC/DC converter can be u ...

LM555/NE555/SA555 Single Timer

... Figure 1 illustrates a monostable circuit. In this mode, the timer generates a fixed pulse whenever the trigger voltage falls below Vcc/3. When the trigger pulse voltage applied to the #2 pin falls below Vcc/3 while the timer output is low, the timer's internal flip-flop turns the discharging Tr. of ...

... Figure 1 illustrates a monostable circuit. In this mode, the timer generates a fixed pulse whenever the trigger voltage falls below Vcc/3. When the trigger pulse voltage applied to the #2 pin falls below Vcc/3 while the timer output is low, the timer's internal flip-flop turns the discharging Tr. of ...

EB63A Construction Hints - Communication Concepts, Inc.

... 4. The output of the amplifier contains harmonics of the input signal. Thus if direct operation into an antenna is expected, filtering of the output is necessary to meet FCC regulations for spectral purity. The low pass filters shown in Figure 1 will provide more that sufficient harmonic attenuation ...

... 4. The output of the amplifier contains harmonics of the input signal. Thus if direct operation into an antenna is expected, filtering of the output is necessary to meet FCC regulations for spectral purity. The low pass filters shown in Figure 1 will provide more that sufficient harmonic attenuation ...

Precision Adjustable Shunt Regulator

... COLL: The collector of the output transistor with a maximum voltage of 36V. This pin is the output of the transconductance amplifier. The overall open loop voltage gain of the transconductance amplifier is gm • RL, where gm is designed to be –140mS ±30mS and RL represents the output load. COMP: The ...

... COLL: The collector of the output transistor with a maximum voltage of 36V. This pin is the output of the transconductance amplifier. The overall open loop voltage gain of the transconductance amplifier is gm • RL, where gm is designed to be –140mS ±30mS and RL represents the output load. COMP: The ...

AD8300 数据手册DataSheet 下载

... is active low. After the new value is fully loaded in the serialinput register, it can be asynchronously transferred to the DAC register by strobing the LD pin. The DAC register uses a level sensitive LD strobe that should be returned high before any new data is loaded ...

... is active low. After the new value is fully loaded in the serialinput register, it can be asynchronously transferred to the DAC register by strobing the LD pin. The DAC register uses a level sensitive LD strobe that should be returned high before any new data is loaded ...

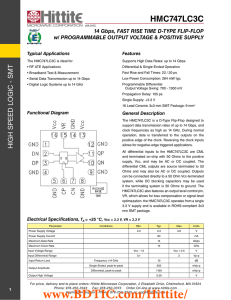

HMC747LC3C 数据资料DataSheet下载

... All differential inputs to the HMC747LC3C are CML and terminated on-chip with 50 Ohms to the positive supply, Vcc, and may be AC or DC coupled. The differential CML outputs are source terminated to 50 Ohms and may also be AC or DC coupled. Outputs can be connected directly to a 50 Ohm Vcc-terminated ...

... All differential inputs to the HMC747LC3C are CML and terminated on-chip with 50 Ohms to the positive supply, Vcc, and may be AC or DC coupled. The differential CML outputs are source terminated to 50 Ohms and may also be AC or DC coupled. Outputs can be connected directly to a 50 Ohm Vcc-terminated ...