Truth Tables and Ohm`s Law

... AND: when two or more Boolean expressions are ANDed, both must be true for the combination to be true. OR: when two or more Boolean expressions are ORed, if either one or the other or both are true, then the combination is true. NOT: takes one Boolean expression and yields the opposite of it, true ...

... AND: when two or more Boolean expressions are ANDed, both must be true for the combination to be true. OR: when two or more Boolean expressions are ORed, if either one or the other or both are true, then the combination is true. NOT: takes one Boolean expression and yields the opposite of it, true ...

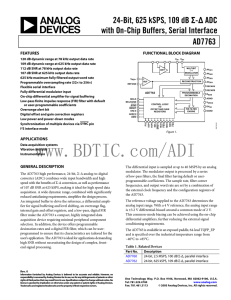

AD7763 数据手册DataSheet下载

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. N ...

... Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. N ...

DS4432 Dual-Channel, I C, 7-Bit Sink/Source Current DAC

... On power-up the DS4432 outputs zero current. This is done to prevent the device from sinking or sourcing an incorrect amount of current before the system host controller has had a chance to modify the DS4432’s setting. As a source for biasing instrumentation or other circuits, the DS4432 provides a ...

... On power-up the DS4432 outputs zero current. This is done to prevent the device from sinking or sourcing an incorrect amount of current before the system host controller has had a chance to modify the DS4432’s setting. As a source for biasing instrumentation or other circuits, the DS4432 provides a ...

F. MILSA implementation considerations

... layer to decide where to send the data packets. However, the caching mechanism in DNS and the binding of TCP connections to IP address make it hard to provide continuous connectivity for mobile users. Mobile IP [2] is one solution, but it suffers from the triangular routing problem. Routing Optimiza ...

... layer to decide where to send the data packets. However, the caching mechanism in DNS and the binding of TCP connections to IP address make it hard to provide continuous connectivity for mobile users. Mobile IP [2] is one solution, but it suffers from the triangular routing problem. Routing Optimiza ...

Calibration of Torque Measurements using Strain

... The previous pages should be all that is needed to get from torque on a shaft to readings recorded by a data acquisition system. The following is information that can assist in optimizing the telemetry, if desired. If the expected telemetry input amplifier’s measurement range is very low in comparis ...

... The previous pages should be all that is needed to get from torque on a shaft to readings recorded by a data acquisition system. The following is information that can assist in optimizing the telemetry, if desired. If the expected telemetry input amplifier’s measurement range is very low in comparis ...

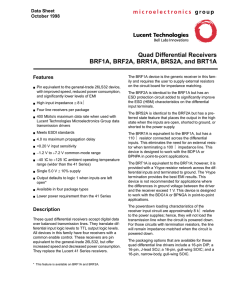

Quad Differential Receivers BRF1A, BRF2A, BRR1A, BRS2A, and BRT1A Features Data Sheet

... The BRS2A is identical to the BRF2A but has a preferred state feature that places the output in the high state when the inputs are open, shorted to ground, or shorted to the power supply. The BRR1A is equivalent to the BRF1A, but has a 110 Ω resistor connected across the differential inputs. This el ...

... The BRS2A is identical to the BRF2A but has a preferred state feature that places the output in the high state when the inputs are open, shorted to ground, or shorted to the power supply. The BRR1A is equivalent to the BRF1A, but has a 110 Ω resistor connected across the differential inputs. This el ...

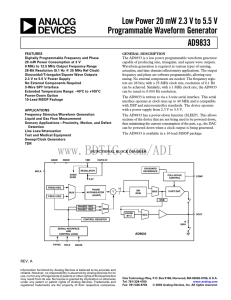

a Low Power 20 mW 2.3 V to 5.5 V AD9833

... The FSYNC input is a level triggered input that acts as a frame synchronization and chip enable. Data can be transferred into the device only when FSYNC is low. To start the serial data transfer, FSYNC should be taken low, observing the minimum FSYNC to SCLK falling edge setup time, t7. After FSYNC ...

... The FSYNC input is a level triggered input that acts as a frame synchronization and chip enable. Data can be transferred into the device only when FSYNC is low. To start the serial data transfer, FSYNC should be taken low, observing the minimum FSYNC to SCLK falling edge setup time, t7. After FSYNC ...

X31-20050926-029 R2 QCOM 3GPP2 Packet Data Network

... Call Flows for Evolved Architecture (1) (for Simple IPv6 or Mobile IPv6 MS) ...

... Call Flows for Evolved Architecture (1) (for Simple IPv6 or Mobile IPv6 MS) ...

Programmable 27-Bit Parallel-to-Serial Receiver

... SubLVDS interface from the transmitting device. Once the SN65LVDS308 detects the presence of the clock and the PLL has locked onto PCLK, then the parity is checked. Parity-error detection ensures detection of all single-bit errors in one pixel and 50% of all multibit errors. The parity bit covers th ...

... SubLVDS interface from the transmitting device. Once the SN65LVDS308 detects the presence of the clock and the PLL has locked onto PCLK, then the parity is checked. Parity-error detection ensures detection of all single-bit errors in one pixel and 50% of all multibit errors. The parity bit covers th ...

ADS1100 数据资料 dataSheet 下载

... carries data; SCL provides the clock. All data is transmitted across the I2C bus in groups of eight bits. To send a bit on the I2C bus, the SDA line is driven to the appropriate level while SCL is LOW (a LOW on SDA indicates the bit is zero; a HIGH indicates the bit is one). Once the SDA line has se ...

... carries data; SCL provides the clock. All data is transmitted across the I2C bus in groups of eight bits. To send a bit on the I2C bus, the SDA line is driven to the appropriate level while SCL is LOW (a LOW on SDA indicates the bit is zero; a HIGH indicates the bit is one). Once the SDA line has se ...

DS1339A Low-Current, I C, Serial Real-Time Clock 2

... Note 13: CB—total capacitance of one bus line in pF. Note 14: Guaranteed by design; not production tested. Note 15: The parameter tOSF is the period of time the oscillator must be stopped for the OSF flag to be set. Note 16: The DS1339A can detect any single SCL clock held low longer than tTIMEOUTMI ...

... Note 13: CB—total capacitance of one bus line in pF. Note 14: Guaranteed by design; not production tested. Note 15: The parameter tOSF is the period of time the oscillator must be stopped for the OSF flag to be set. Note 16: The DS1339A can detect any single SCL clock held low longer than tTIMEOUTMI ...

ccna3 3.0-04 Introduction to LAN Switching

... support data transmission rates of up to 10 Gbps (gigabits per second). Goal of Standard Ethernet is to provide a best effort delivery service and allow all devices on the shared medium to transmit on an equal basis. ...

... support data transmission rates of up to 10 Gbps (gigabits per second). Goal of Standard Ethernet is to provide a best effort delivery service and allow all devices on the shared medium to transmit on an equal basis. ...

AD5516: 英文产品数据手册下载

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

... Serial Clock Input. Data is clocked into the shift register on the falling edge of SCLK. This operates at clock speeds up to 20 MHz. Serial Data Input. Data must be valid on the falling edge of SCLK. Serial Data Output. DOUT can be used for daisy-chaining a number of devices together or for reading ...

T D A 7 1 1 0 F

... AC/DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AC/DC Characteristic at 3V, 25°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AC/DC Characteristic at 2.1V ... 4.0 V, -40°C ...+85°C . . . . . . . . . . . . . ...

... AC/DC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AC/DC Characteristic at 3V, 25°C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . AC/DC Characteristic at 2.1V ... 4.0 V, -40°C ...+85°C . . . . . . . . . . . . . ...

Data center application note No. 10079

... alleviates the design hassle of trying to achieve selectively coordinated OCPDs at the cabinet and busway (or PDU) levels as well as further upstream. Fuses simply need to maintain a 2:1* amp rating ratio for Bussmann series Low-Peak fuses from the lineside fuse to the loadside fuse in order to achi ...

... alleviates the design hassle of trying to achieve selectively coordinated OCPDs at the cabinet and busway (or PDU) levels as well as further upstream. Fuses simply need to maintain a 2:1* amp rating ratio for Bussmann series Low-Peak fuses from the lineside fuse to the loadside fuse in order to achi ...

Physics Unpacked Content - North Carolina Public Schools

... Phy.1.2 Analyze systems of forces and their interaction with matter. Phy.1.2.1 Analyze forces and systems of forces graphically and numerically using vectors, graphs, and calculations. Phy.1.2.2 Analyze systems of forces in one dimension and two dimensions using free body diagrams. Phy.1.2.3 Explain ...

... Phy.1.2 Analyze systems of forces and their interaction with matter. Phy.1.2.1 Analyze forces and systems of forces graphically and numerically using vectors, graphs, and calculations. Phy.1.2.2 Analyze systems of forces in one dimension and two dimensions using free body diagrams. Phy.1.2.3 Explain ...

C-Linking - Elsevier Store

... [Src Port][Dest Port][Seq #][Ack #][H Len][Res][Uflag][Pflag][Rflag][Sflag][Fflag][WinSz][Chksum][UP[O] [Data] ...

... [Src Port][Dest Port][Seq #][Ack #][H Len][Res][Uflag][Pflag][Rflag][Sflag][Fflag][WinSz][Chksum][UP[O] [Data] ...

PCM1798 数据资料 dataSheet 下载

... The PCM1798 includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1798 also includes an external reset capability using the RS ...

... The PCM1798 includes a power-on reset function. Figure 19 shows the operation of this function. With VDD > 2 V, the power-on reset function is enabled. The initialization sequence requires 1024 system clocks from the time VDD > 2 V. The PCM1798 also includes an external reset capability using the RS ...