ppt

... require virtualizing the I/O – only needs to assure exclusivity Interposition on all DMA requests allows to share disk and memory resources among virtual machines and allows VMs to communicate with each other ...

... require virtualizing the I/O – only needs to assure exclusivity Interposition on all DMA requests allows to share disk and memory resources among virtual machines and allows VMs to communicate with each other ...

PowerPoint - NYU Computer Science

... Supervisor mode: Guest operating system Provides access to special memory segment (used for optimizations) ...

... Supervisor mode: Guest operating system Provides access to special memory segment (used for optimizations) ...

08-OS-Support

... Pentium II Segmentation • Each virtual address is 16-bit segment and 32-bit offset • 2 bits of segment are protection ...

... Pentium II Segmentation • Each virtual address is 16-bit segment and 32-bit offset • 2 bits of segment are protection ...

Concepts and Structures

... File System • Implements long-term store (often on disk) • root, file-hierarchy, working directory, access ...

... File System • Implements long-term store (often on disk) • root, file-hierarchy, working directory, access ...

Suppose that a disk drive has 10,000 cylinders, numbered 0 to 9999

... Binding of code and data to memory can be done at compile-time, load-time, or execution-time. An address generated by a CPU is referred to as a physical address The vfork() system call in UNIX allows the child process to use the address space of the parent. Belady's Anomaly states that giving more m ...

... Binding of code and data to memory can be done at compile-time, load-time, or execution-time. An address generated by a CPU is referred to as a physical address The vfork() system call in UNIX allows the child process to use the address space of the parent. Belady's Anomaly states that giving more m ...

one.world — System Support for Pervasive Applications

... Emulation by direct execution Not for privileged instructions, direct access to physical memory and I/O devices Emulated in VMM Recorded in per VM data structure (registers, TLB contents) Some traps (syscall, page fault) handled by guest OS’s trap handlers ...

... Emulation by direct execution Not for privileged instructions, direct access to physical memory and I/O devices Emulated in VMM Recorded in per VM data structure (registers, TLB contents) Some traps (syscall, page fault) handled by guest OS’s trap handlers ...

Section 10: Intro to I/O and File Systems

... the I/O devices are mapped to (associated with) address values. So when an address is accessed by the CPU, it may refer to a portion of physical RAM, but it can also refer to memory of the I/O device. Thus, the CPU instructions used to access the memory can also be used for accessing devices. ...

... the I/O devices are mapped to (associated with) address values. So when an address is accessed by the CPU, it may refer to a portion of physical RAM, but it can also refer to memory of the I/O device. Thus, the CPU instructions used to access the memory can also be used for accessing devices. ...

Chapter 1: Introduction

... the associated process. This process of address translation will also check to make sure that all addresses are “legal”, ie., make sure that the addresses are within the specified address space. Sharing memory will be only allowed “cautiously” under the discipline of the OS. This process is logicall ...

... the associated process. This process of address translation will also check to make sure that all addresses are “legal”, ie., make sure that the addresses are within the specified address space. Sharing memory will be only allowed “cautiously” under the discipline of the OS. This process is logicall ...

COS 318: Operating Systems Virtual Memory and Address Translation Andy Bavier

... Bits in a TLB Entry ...

... Bits in a TLB Entry ...

Answer the following questions clearly but concisely. What is multiprogramming? 1.

... (b) With a two-level page table. 16KB pages, and 4-byte entries, how many bits should be allocated for the top-level page table field and how many for the next-level page table field? Explain. ...

... (b) With a two-level page table. 16KB pages, and 4-byte entries, how many bits should be allocated for the top-level page table field and how many for the next-level page table field? Explain. ...

COS 318: Operating Systems Virtual Memory and Its Address Translations Kai Li

... Bits in a TLB Entry ...

... Bits in a TLB Entry ...

08 Operating System Support

... memory (according to Raymond Kurzweil). A Holographic Versatile Disc (HVD) can hold up to 3.9 terabytes. One hour of uncompressed Ultra High Definition Video (UHDV) consumes approximately 11.5 terabytes of data. The U.S. Library of Congress has claimed that "as of December 31, 2005, the Library has ...

... memory (according to Raymond Kurzweil). A Holographic Versatile Disc (HVD) can hold up to 3.9 terabytes. One hour of uncompressed Ultra High Definition Video (UHDV) consumes approximately 11.5 terabytes of data. The U.S. Library of Congress has claimed that "as of December 31, 2005, the Library has ...

Computers

... interrupted processes Mutual exclusion: keeping shared resource use separate Determinate program operation: programs get the same result every time independent of what else is running Deadlock ...

... interrupted processes Mutual exclusion: keeping shared resource use separate Determinate program operation: programs get the same result every time independent of what else is running Deadlock ...

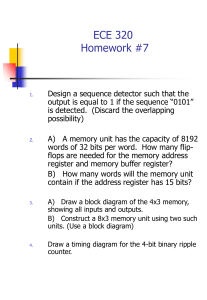

EE 320 – Homework #7

... words of 32 bits per word. How many flipflops are needed for the memory address register and memory buffer register? B) How many words will the memory unit contain if the address register has 15 bits? A) Draw a block diagram of the 4x3 memory, showing all inputs and outputs. B) Construct a 8x3 memor ...

... words of 32 bits per word. How many flipflops are needed for the memory address register and memory buffer register? B) How many words will the memory unit contain if the address register has 15 bits? A) Draw a block diagram of the 4x3 memory, showing all inputs and outputs. B) Construct a 8x3 memor ...

university of helsinki 24.8.2001

... In a multiprogramming environment the applications are not allowed to mess each other and they are not allowed to use resources not owned by themselves without given permissions. To implement a multiprogramming operating system certain hardware level features are desirable. Explain what kind of supp ...

... In a multiprogramming environment the applications are not allowed to mess each other and they are not allowed to use resources not owned by themselves without given permissions. To implement a multiprogramming operating system certain hardware level features are desirable. Explain what kind of supp ...

COS 598: Advanced Operating System

... What is a page fault? What happens on a page fault? Is paging good or bad? What is the size of the virtual address space for a 32 bit system? A 64-bit system? Is 2^64 a big number? Assume a system with 8 pages each of which is 1K bytes. How many bits are needed to generate addresses? What is interna ...

... What is a page fault? What happens on a page fault? Is paging good or bad? What is the size of the virtual address space for a 32 bit system? A 64-bit system? Is 2^64 a big number? Assume a system with 8 pages each of which is 1K bytes. How many bits are needed to generate addresses? What is interna ...

Memory management unit

A memory management unit (MMU), sometimes called paged memory management unit (PMMU), is a computer hardware unit having all memory references passed through itself, primarily performing the translation of virtual memory addresses to physical addresses. It is usually implemented as part of the central processing unit (CPU), but it also can be in the form of a separate integrated circuit.An MMU effectively performs virtual memory management, handling at the same time memory protection, cache control, bus arbitration and, in simpler computer architectures (especially 8-bit systems), bank switching.