Anx 30 B - B.Sc. ECS _Col_ 08-09

... Paper VIII : Digital and Cellular Communications Pract. III Digital Electronics Lab. Pract. IV Radio, TV and Instrumentation Lab Allied : IV Object Oriented Programming using C++ ...

... Paper VIII : Digital and Cellular Communications Pract. III Digital Electronics Lab. Pract. IV Radio, TV and Instrumentation Lab Allied : IV Object Oriented Programming using C++ ...

EVALUATION AND DESIGN SUPPORT

... (Continued from first page) Circuits from the Lab circuits are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab circuits in the design of your product, no other license is granted by i ...

... (Continued from first page) Circuits from the Lab circuits are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab circuits in the design of your product, no other license is granted by i ...

CPSC 121 Midterm 2 Friday November 13th, 2015

... [3] b. Describe as simply as you can the set of words that this finite-state automaton accepts. Solution : It accepts words that contain at least one I, do not contain any R, and where every L must be immediately preceded by an E. [11] 4. For each of the two following theorems, first translate the t ...

... [3] b. Describe as simply as you can the set of words that this finite-state automaton accepts. Solution : It accepts words that contain at least one I, do not contain any R, and where every L must be immediately preceded by an E. [11] 4. For each of the two following theorems, first translate the t ...

- GPW Morni, Panchkula

... components, thus allowing the features or function of a hardware implementation of a logic system to be changed. Electronic logic gates differ significantly from their relay-and-switch equivalents. They are much faster, consume much less power, and are much smaller (all by a factor of a million or ...

... components, thus allowing the features or function of a hardware implementation of a logic system to be changed. Electronic logic gates differ significantly from their relay-and-switch equivalents. They are much faster, consume much less power, and are much smaller (all by a factor of a million or ...

experiment no 4

... The circuit in fig 5.1 is an 8 bit binary Adder/Subtracter, it is constructed by cascading two 74LS83 (4 bit binary adder) in which the carry out of the first IC (low order) is connected to the carry in of the second IC (high order). ...

... The circuit in fig 5.1 is an 8 bit binary Adder/Subtracter, it is constructed by cascading two 74LS83 (4 bit binary adder) in which the carry out of the first IC (low order) is connected to the carry in of the second IC (high order). ...

Rosetta Demostrator Project MASC, Adelaide University

... Systems Approach Using VHDL, by Peter J. Ashenden, published by Morgan ...

... Systems Approach Using VHDL, by Peter J. Ashenden, published by Morgan ...

AD9300 4x1 Wideband Video Multiplexer Data Sheet (Rev. A)

... Bipolar construction used in the AD9300 ensures that the input impedance of the device remains high and will not vary with power supply voltages. This characteristic makes the AD9300, in effect, a switchable-input buffer. An onboard bias network makes the performance of the AD9300 independent of app ...

... Bipolar construction used in the AD9300 ensures that the input impedance of the device remains high and will not vary with power supply voltages. This characteristic makes the AD9300, in effect, a switchable-input buffer. An onboard bias network makes the performance of the AD9300 independent of app ...

Introduction to IC Testing

... Terms that Apply to Test parameters VCC : The supply voltage of a TTL device ICC : The current consumed by the circuitry of a TTL device VDD : The supply voltage of a MOS device IDD : The current consumed by the circuitry of a MOS device IIH : Input Leakage High is the maximum amount of current tha ...

... Terms that Apply to Test parameters VCC : The supply voltage of a TTL device ICC : The current consumed by the circuitry of a TTL device VDD : The supply voltage of a MOS device IDD : The current consumed by the circuitry of a MOS device IIH : Input Leakage High is the maximum amount of current tha ...

Trip Circuit Supervision for M

... 1. Under I/O Configuration, the Input #1 setting must be configured as “General Input”. ...

... 1. Under I/O Configuration, the Input #1 setting must be configured as “General Input”. ...

LF198/LF298/LF398, LF198A/LF398A Monolithic Sample-and-Hold Circuits LF198/LF298/LF398, LF198A/LF398A

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

LF198/LF298/LF398, LF198A/LF398A Monolithic Sample-and

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

... cap, for instance, may “sag back” up to 0.2% after a quick change in voltage. A long sample time is required before the circuit can be put back into the hold mode with this type of capacitor. Dielectrics with very low hysteresis are polystyrene, polypropylene, and Teflon. Other types such as mica an ...

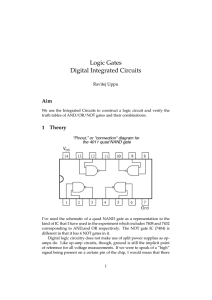

Logic Gates Digital Integrated Circuits

... truth tables of AND/OR/NOT gates and their combinations. ...

... truth tables of AND/OR/NOT gates and their combinations. ...

DM7476 Dual Master-Slave J-K Flip-Flops with Clear, Preset, and

... This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flop after a complete clock pulse. While the clock is LOW the slave is isolated from the master. On the positive transition of the clock, the data from t ...

... This device contains two independent positive pulse triggered J-K flip-flops with complementary outputs. The J and K data is processed by the flip-flop after a complete clock pulse. While the clock is LOW the slave is isolated from the master. On the positive transition of the clock, the data from t ...

An ultimatic adapter for iambic keyers

... 4. Lin = 0, Rin = 0 after Lin = 1, Rin = 0 gives output Lout = 1, Rout = 0. 5. Lin = 0, Rin = 0 after Lin = 0, Rin = 1 gives output Lout = 0, Rout = 1. State 1 has both paddles open and neither key line keyed. States 2 and 3 have either just the left or just the right paddle closed and the correspo ...

... 4. Lin = 0, Rin = 0 after Lin = 1, Rin = 0 gives output Lout = 1, Rout = 0. 5. Lin = 0, Rin = 0 after Lin = 0, Rin = 1 gives output Lout = 0, Rout = 1. State 1 has both paddles open and neither key line keyed. States 2 and 3 have either just the left or just the right paddle closed and the correspo ...

An 8-bit 50-MS/s CMOS DIGITAL-ANALOG CONVERTER

... In this paper a new 8-bit CMOS DAC has been presented. The presented DAC is constructed using only active elements, which makes it suitable for integration. The performance of the DAC is tested using SPICE simulation program. The conversion rate of the proposed DAC is 50 Msample/s with settling time ...

... In this paper a new 8-bit CMOS DAC has been presented. The presented DAC is constructed using only active elements, which makes it suitable for integration. The performance of the DAC is tested using SPICE simulation program. The conversion rate of the proposed DAC is 50 Msample/s with settling time ...

CMOS

... to an output. The sum must be less than the output’s IOH specification. Step 2: add up the IIL for all inputs connected to an output. The sum must be less than the output’s IOL specification. Examples 8-7 to 8-9. ...

... to an output. The sum must be less than the output’s IOH specification. Step 2: add up the IIL for all inputs connected to an output. The sum must be less than the output’s IOL specification. Examples 8-7 to 8-9. ...

Digital electronics

Digital electronics or digital (electronic) circuits are electronics that handle digital signals- discrete bands of analog levels, rather than by continuous ranges (as used in analogue electronics). All levels within a band of values represent the same numeric value. Because of this discretization, relatively small changes to the analog signal levels due to manufacturing tolerance, signal attenuation or parasitic noise do not leave the discrete envelope, and as a result are ignored by signal state sensing circuitry.In most cases the number of these states is two, and they are represented by two voltage bands: one near a reference value (typically termed as ""ground"" or zero volts), and the other a value near the supply voltage. These correspond to the ""false"" (""0"") and ""true"" (""1"") values of the Boolean domain, respectively, yielding binary code.Digital techniques are useful because it is easier to get an electronic device to switch into one of a number of known states than to accurately reproduce a continuous range of values.Digital electronic circuits are usually made from large assemblies of logic gates, simple electronic representations of Boolean logic functions.