4 - Binus Repository

... Since impedance relates phasor voltage to phasor current, it is a complex quantity whose units are ohms. Although impedance can be a complex number, it is not a phasor. Phasors represent sinusoidal signals, while impedances characterize circuit elements in the sinusoidal steady state. Finally, it is ...

... Since impedance relates phasor voltage to phasor current, it is a complex quantity whose units are ohms. Although impedance can be a complex number, it is not a phasor. Phasors represent sinusoidal signals, while impedances characterize circuit elements in the sinusoidal steady state. Finally, it is ...

MAX530 +5V, Low-Power, Parallel-Input, Voltage-Output, 12

... The MAX530 is a low-power, 12-bit, voltage-output digital-to-analog converter (DAC) that uses single +5V or dual ±5V supplies. This device has an on-chip voltage reference plus an output buffer amplifier. Operating current is only 250µA from a single +5V supply, making it ideal for portable and batt ...

... The MAX530 is a low-power, 12-bit, voltage-output digital-to-analog converter (DAC) that uses single +5V or dual ±5V supplies. This device has an on-chip voltage reference plus an output buffer amplifier. Operating current is only 250µA from a single +5V supply, making it ideal for portable and batt ...

AD8037

... clamp levels, signals with speeds up to 240 MHz can be applied to the clamp pins. The clamp values can also be set to any value within the output voltage range provided that VH is greater that VL. Due to these clamp characteristics, the AD8036 and AD8037 can be used in nontraditional applications su ...

... clamp levels, signals with speeds up to 240 MHz can be applied to the clamp pins. The clamp values can also be set to any value within the output voltage range provided that VH is greater that VL. Due to these clamp characteristics, the AD8036 and AD8037 can be used in nontraditional applications su ...

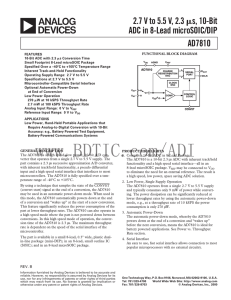

AD7810 数据手册DataSheet下载

... The analog input of the AD7810 is made up of a pseudo differential pair. VIN+ pseudo differential with respect to VIN–. The signal is applied to VIN+, but in the pseudo differential scheme the sampling capacitor is connected to VIN– during conversion (see Figure 8). This input scheme can be used to ...

... The analog input of the AD7810 is made up of a pseudo differential pair. VIN+ pseudo differential with respect to VIN–. The signal is applied to VIN+, but in the pseudo differential scheme the sampling capacitor is connected to VIN– during conversion (see Figure 8). This input scheme can be used to ...

MAX847 1-Cell, Step-Up Two-Way Pager System IC ________________General Description

... This is not a tested parameter, since the IC is powered from OUT, not BATT. The only limitation in the BATT range is the inability to generate more than 5 times, or less than 1.15 times the BATT voltage at OUT. This is due to PWM controller duty-cycle limitations in Run Mode. Minimum start-up voltag ...

... This is not a tested parameter, since the IC is powered from OUT, not BATT. The only limitation in the BATT range is the inability to generate more than 5 times, or less than 1.15 times the BATT voltage at OUT. This is due to PWM controller duty-cycle limitations in Run Mode. Minimum start-up voltag ...

The LM3900 A New Current-Differencing Quad of Plus or Minus

... The gain stage is basically a single common-emitter amplifier. By making use of current source loads, a large voltage gain has been achieved which is very constant over temperature changes. The output voltage has a large dynamic range, from essentially ground to one VBE less than the power supply vo ...

... The gain stage is basically a single common-emitter amplifier. By making use of current source loads, a large voltage gain has been achieved which is very constant over temperature changes. The output voltage has a large dynamic range, from essentially ground to one VBE less than the power supply vo ...

COMPUTER AIDED DESIGN OF ELECTRONIC DEVICES

... Designers have long used computers for their calculations. Digital computers were used in power system analysis or optimization as early as proto-“Whirlwind” in 1949. Circuit design theory, or power network methodology would be algebraic, symbolic, and often Vector based. Examples of problems being ...

... Designers have long used computers for their calculations. Digital computers were used in power system analysis or optimization as early as proto-“Whirlwind” in 1949. Circuit design theory, or power network methodology would be algebraic, symbolic, and often Vector based. Examples of problems being ...

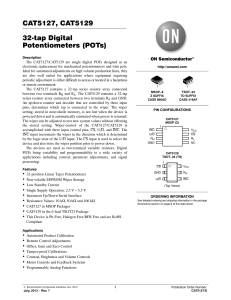

POTs - ONSemi

... RL: Low End Potentiometer Terminal (CAT5127 only) RL is the low end terminal of the potentiometer. It is not required that this terminal be connected to a potential less than the RH terminal. Voltage applied to the RL terminal cannot exceed the supply voltage, VCC or go below ground, GND. RL and RH ...

... RL: Low End Potentiometer Terminal (CAT5127 only) RL is the low end terminal of the potentiometer. It is not required that this terminal be connected to a potential less than the RH terminal. Voltage applied to the RL terminal cannot exceed the supply voltage, VCC or go below ground, GND. RL and RH ...

BD91361MUV

... (Note 2) IC only (Note 3) Mounted on a 1-layer 74.2mmx74.2mmx1.6mm glass-epoxy board, occupied area by copper foil : 10.29mm2 (Note 4) Mounted on a 4-layer 74.2mmx74.2mmx1.6mm glass-epoxy board, 1st and 4th copper foil area : 10.29mm2, 2nd and 3rd copper foil area : 5505mm2 (Note 5) Mounted on a 4-l ...

... (Note 2) IC only (Note 3) Mounted on a 1-layer 74.2mmx74.2mmx1.6mm glass-epoxy board, occupied area by copper foil : 10.29mm2 (Note 4) Mounted on a 4-layer 74.2mmx74.2mmx1.6mm glass-epoxy board, 1st and 4th copper foil area : 10.29mm2, 2nd and 3rd copper foil area : 5505mm2 (Note 5) Mounted on a 4-l ...

比较器系列ADCMP609 数据手册DataSheet 下载

... equivalent). For large fan outputs, buses, or transmission lines, use an appropriate buffer to maintain the excellent speed and stability of the comparator. With the rated 15 pF load capacitance applied, more than half of the total device propagation delay is output stage slew time. Because of this, ...

... equivalent). For large fan outputs, buses, or transmission lines, use an appropriate buffer to maintain the excellent speed and stability of the comparator. With the rated 15 pF load capacitance applied, more than half of the total device propagation delay is output stage slew time. Because of this, ...

AN2123

... 6 2-Level turn-off In the event of a short-circuit or overcurrent in the load, a large voltage overshoot can occur across the IGBT at turn-off and can exceed the IGBT breakdown voltage. By reducing the gate voltage before turnoff, the IGBT current is limited and the potential over-voltage is reduced ...

... 6 2-Level turn-off In the event of a short-circuit or overcurrent in the load, a large voltage overshoot can occur across the IGBT at turn-off and can exceed the IGBT breakdown voltage. By reducing the gate voltage before turnoff, the IGBT current is limited and the potential over-voltage is reduced ...

Evaluation Board User Guide UG-122

... when supplying its largest load level (300 mA). Figure 15 shows the typical ground current consumption for various load levels at VIN = 2.5 V. When the device is disabled (EN2 = PGND), ground current drops to less than 2 μA. ...

... when supplying its largest load level (300 mA). Figure 15 shows the typical ground current consumption for various load levels at VIN = 2.5 V. When the device is disabled (EN2 = PGND), ground current drops to less than 2 μA. ...

AD8113 数据手册DataSheet 下载

... isolation of 90 dB. In addition, ground/power pins surround all inputs and outputs to provide extra shielding for operation in the most demanding audio routing applications. The differential gain and differential phase of better than 0.1% and 0.1°, respectively, along with 0.1 dB flatness out to 10 ...

... isolation of 90 dB. In addition, ground/power pins surround all inputs and outputs to provide extra shielding for operation in the most demanding audio routing applications. The differential gain and differential phase of better than 0.1% and 0.1°, respectively, along with 0.1 dB flatness out to 10 ...

STM6522

... delay are met, the device generates an output reset pulse for a fixed timeout period (tREC). The typical application hookup shows that either a single Smart Reset™ input, or both reset inputs can be connected to the applications interrupt and control both the interrupt pin and the hard reset functio ...

... delay are met, the device generates an output reset pulse for a fixed timeout period (tREC). The typical application hookup shows that either a single Smart Reset™ input, or both reset inputs can be connected to the applications interrupt and control both the interrupt pin and the hard reset functio ...