MAX13085EASA+中文资料

... that have very slow rise and fallstate against an external parasitic capacitance up totimes. Receiver propagation delay increases by 25_0pF that can drive DE high. After 7?s, the timerdue to this filtering. ...

... that have very slow rise and fallstate against an external parasitic capacitance up totimes. Receiver propagation delay increases by 25_0pF that can drive DE high. After 7?s, the timerdue to this filtering. ...

SN74LVC1G3208-Q1 数据资料 dataSheet 下载

... Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to a ...

... Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to a ...

LME49710 数据资料 dataSheet 下载

... the error signal (distortion) is amplified by a factor of 101. Although the amplifier’s closed-loop gain is unaltered, the feedback available to correct distortion errors is reduced by 101, which means that measurement resolution increases by 101. To ensure minimum effects on distortion measurements ...

... the error signal (distortion) is amplified by a factor of 101. Although the amplifier’s closed-loop gain is unaltered, the feedback available to correct distortion errors is reduced by 101, which means that measurement resolution increases by 101. To ensure minimum effects on distortion measurements ...

Lesson 6

... • Structures of N and P material can control current flow through the semiconductor. 2014 Technician License Course ...

... • Structures of N and P material can control current flow through the semiconductor. 2014 Technician License Course ...

UM10301 User Manual for NXP Real Time Clocks PCF85x3, PCA8565

... This application note deals with the PCF85x3 family with focus on the PCF8563, and with the more recent additions to the NXP RTC portfolio PCF2123 and PCA2125. The PCF2123 is an extremely low power RTC which allows fine tuning of the clock using an offset register (electronic tuning). PCA2125 is tar ...

... This application note deals with the PCF85x3 family with focus on the PCF8563, and with the more recent additions to the NXP RTC portfolio PCF2123 and PCA2125. The PCF2123 is an extremely low power RTC which allows fine tuning of the clock using an offset register (electronic tuning). PCA2125 is tar ...

Electrical energy supply

... insufficient power causes a drop in frequency. Automated systems disconnect producers that do not comply with the standards, but for the regulators of the system this automation results in random events that are not controlled and may cause damage. In many countries throughout the world the system i ...

... insufficient power causes a drop in frequency. Automated systems disconnect producers that do not comply with the standards, but for the regulators of the system this automation results in random events that are not controlled and may cause damage. In many countries throughout the world the system i ...

74CBTLV3861 1. General description 10-bit bus switch with output enable

... LOW, the switch is closed and port A is connected to the B port. When OE is HIGH, the switch is disabled. To ensure the high-impedance OFF-state during power-up or power-down, OE should be tied to the VCC through a pull-up resistor. The minimum value of the resistor is determined by the current-sink ...

... LOW, the switch is closed and port A is connected to the B port. When OE is HIGH, the switch is disabled. To ensure the high-impedance OFF-state during power-up or power-down, OE should be tied to the VCC through a pull-up resistor. The minimum value of the resistor is determined by the current-sink ...

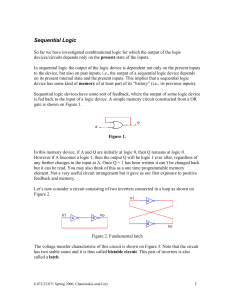

Sequential Logic

... inputs of gate GR are 0 and so the output of GR must be 1. So Q = 1 and Q = 0. In this case we say that the flip-flop is SET 2. R = 1, S = 0. In this case the output of NOR gate GR must be 0 (Q = 0). Now both inputs of gate GS are 0 and so the output of GS must be 1. So Q = 0 and Q = 1. In this case ...

... inputs of gate GR are 0 and so the output of GR must be 1. So Q = 1 and Q = 0. In this case we say that the flip-flop is SET 2. R = 1, S = 0. In this case the output of NOR gate GR must be 0 (Q = 0). Now both inputs of gate GS are 0 and so the output of GS must be 1. So Q = 0 and Q = 1. In this case ...

Robust FinFET Memory Circuits with P

... The width of a FinFET is quantized due to the vertical gate structure. The fin height determines the minimum transistor width. Since the fin height is fixed in a FinFET technology, multiple parallel fins are utilized to increase the width of a FinFET, as shown in Figure 2. The two vertical gates of a Fi ...

... The width of a FinFET is quantized due to the vertical gate structure. The fin height determines the minimum transistor width. Since the fin height is fixed in a FinFET technology, multiple parallel fins are utilized to increase the width of a FinFET, as shown in Figure 2. The two vertical gates of a Fi ...

LTM8047 - 3.1VIN to 32VIN Isolated uModule DC/DC Converter

... BIAS Pin Considerations The BIAS pin is the output of an internal linear regulator that powers the LTM8047’s internal circuitry. It is set to 3V and must be decoupled with a low ESR capacitor of at least 4.7μF. The LTM8047 will run properly without applying a voltage to this pin, but will operate mo ...

... BIAS Pin Considerations The BIAS pin is the output of an internal linear regulator that powers the LTM8047’s internal circuitry. It is set to 3V and must be decoupled with a low ESR capacitor of at least 4.7μF. The LTM8047 will run properly without applying a voltage to this pin, but will operate mo ...

APPLICATION NOTE—105 Application Note 105 December 2005 Current Sense Circuit Collection

... This is the same sampling architecture as used in the front-end of the LTC2053 and LTC6800, but sans op amp gain stage. This particular switch can handle up to 18V, so the ultra-high precision concept can be utilized at higher voltages than the fully integrated ICs mentioned. This circuit simply com ...

... This is the same sampling architecture as used in the front-end of the LTC2053 and LTC6800, but sans op amp gain stage. This particular switch can handle up to 18V, so the ultra-high precision concept can be utilized at higher voltages than the fully integrated ICs mentioned. This circuit simply com ...

NCP5106BA36WGEVB NCP5106B 36W Ballast Evaluation Board User's Manual

... when the low side power MOSFET (Q2) is switched ON, the BRIDGE pin is pulled down to the ground, thus the capacitor connected between BRIDGE pin and VBOOT pin is refuelled via the diode D3 and the resistor R5 connected to VCC. When Q2 is switched OFF the bootstrap capacitor C6 supplies the high side ...

... when the low side power MOSFET (Q2) is switched ON, the BRIDGE pin is pulled down to the ground, thus the capacitor connected between BRIDGE pin and VBOOT pin is refuelled via the diode D3 and the resistor R5 connected to VCC. When Q2 is switched OFF the bootstrap capacitor C6 supplies the high side ...

word - Rackcdn.com

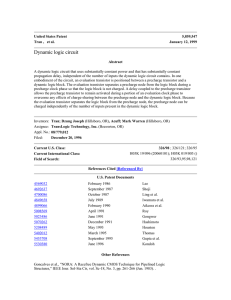

... the capacitors C.sub.1 -C.sub.4 absorb enough charge from capacitor C.sub.5 that the circuit output erroneously goes high. The larger the number of inputs, the more charge-sharing that occurs and the more likely the circuit will improperly operate. An objective of the invention, therefore, is to pr ...

... the capacitors C.sub.1 -C.sub.4 absorb enough charge from capacitor C.sub.5 that the circuit output erroneously goes high. The larger the number of inputs, the more charge-sharing that occurs and the more likely the circuit will improperly operate. An objective of the invention, therefore, is to pr ...

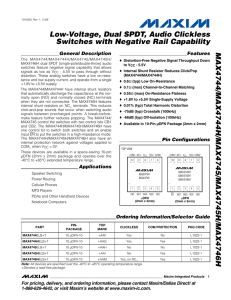

MAX4744/MAX4744H/MAX4745/MAX4745H/MAX4746H Low-Voltage, Dual SPDT, Audio Clickless Switches with Negative Rail Capability General Description

... Figure 3. Break-Before-Make Interval ...

... Figure 3. Break-Before-Make Interval ...

Xtender, Unit combining inverter, battery charger and transfer system

... Studer Innotec SA 2015 – V4.6.0 ...

... Studer Innotec SA 2015 – V4.6.0 ...

Power MOSFET

A power MOSFET is a specific type of metal oxide semiconductor field-effect transistor (MOSFET) designed to handle significant power levels.Compared to the other power semiconductor devices, for example an insulated-gate bipolar transistor (IGBT) or a thyristor, its main advantages are high commutation speed and good efficiency at low voltages. It shares with the IGBT an isolated gate that makes it easy to drive. They can be subject to low gain, sometimes to degree that the gate voltage needs to be higher than the voltage under control.The design of power MOSFETs was made possible by the evolution of CMOS technology, developed for manufacturing integrated circuits in the late 1970s. The power MOSFET shares its operating principle with its low-power counterpart, the lateral MOSFET.The power MOSFET is the most widely used low-voltage (that is, less than 200 V) switch. It can be found in most power supplies, DC to DC converters, and low voltage motor controllers.